Contadores

Anuncio

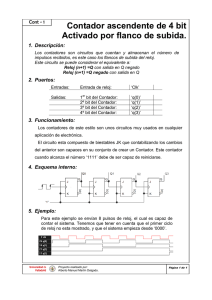

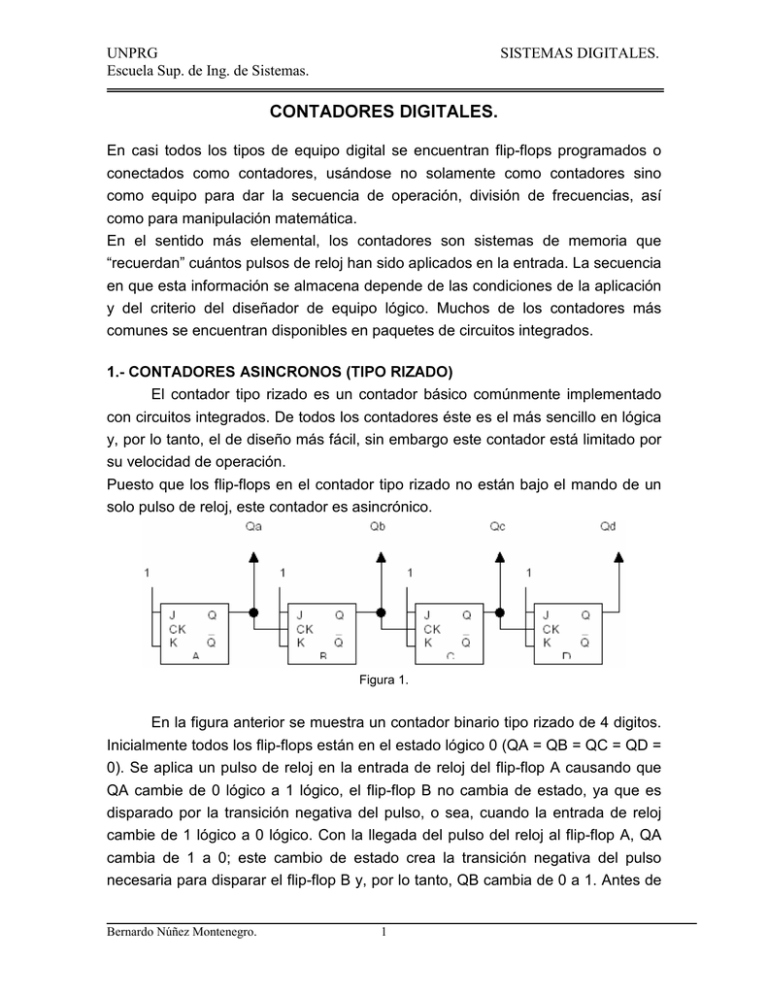

UNPRG Escuela Sup. de Ing. de Sistemas. SISTEMAS DIGITALES. &217$'25(6',*,7$/(6 En casi todos los tipos de equipo digital se encuentran flip-flops programados o conectados como contadores, usándose no solamente como contadores sino como equipo para dar la secuencia de operación, división de frecuencias, así como para manipulación matemática. En el sentido más elemental, los contadores son sistemas de memoria que “recuerdan” cuántos pulsos de reloj han sido aplicados en la entrada. La secuencia en que esta información se almacena depende de las condiciones de la aplicación y del criterio del diseñador de equipo lógico. Muchos de los contadores más comunes se encuentran disponibles en paquetes de circuitos integrados. &217$'25(6$6,1&521267,325,=$'2 El contador tipo rizado es un contador básico comúnmente implementado con circuitos integrados. De todos los contadores éste es el más sencillo en lógica y, por lo tanto, el de diseño más fácil, sin embargo este contador está limitado por su velocidad de operación. Puesto que los flip-flops en el contador tipo rizado no están bajo el mando de un solo pulso de reloj, este contador es asincrónico. Figura 1. En la figura anterior se muestra un contador binario tipo rizado de 4 digitos. Inicialmente todos los flip-flops están en el estado lógico 0 (QA = QB = QC = QD = 0). Se aplica un pulso de reloj en la entrada de reloj del flip-flop A causando que QA cambie de 0 lógico a 1 lógico, el flip-flop B no cambia de estado, ya que es disparado por la transición negativa del pulso, o sea, cuando la entrada de reloj cambie de 1 lógico a 0 lógico. Con la llegada del pulso del reloj al flip-flop A, QA cambia de 1 a 0; este cambio de estado crea la transición negativa del pulso necesaria para disparar el flip-flop B y, por lo tanto, QB cambia de 0 a 1. Antes de Bernardo Núñez Montenegro. 1 UNPRG Escuela Sup. de Ing. de Sistemas. SISTEMAS DIGITALES. la llegada del decimosexto pulso del reloj todos los flip-flops están en el estado 1, y el pulso número 16 causa que QA, QB, QC y QD cambien a 0 lógico. Figura 2. El contador binario de 4 dígitos repite el ciclo cada 2n (n = número de flipflops) pulsos de reloj. Este contador establece la secuencia en un sistema de números de base 16 y tiene 16 estados discretos que van desde 0 hasta N-1. Los 16 estados binarios se muestran en la tabla siguiente: La frecuencia máxima del reloj para un contador es dada por: 1/f <= N(Tp) + Ts N = número de etapas de flip-flops. Tp= tiempo de propagación de un flip-flop. Ts = tiempo de compuerta, ancho del pulso de la salida decodificada. Bernardo Núñez Montenegro. 2 UNPRG Escuela Sup. de Ing. de Sistemas. SISTEMAS DIGITALES. Suponiendo que cada flip-flop del contador mostrado en la figura tiene un pulso de propagación de 50ns, se requieren entonces 200 ns, para que el contador cambie de 1111 a 0000, y si la decodificación de un estado requiere 100 ns, entonces: 1/f >= 4(50) + 100 = 300 ns f <= 3.67 Mhz El flip-flop A en el contador de la figura, cambia de estado con cada pulso de reloj, por lo que divide entre 2 la frecuencia del reloj de entrada. El flip-flop B cambia de estado con cada dos pulsos de reloj, dividiendo la frecuencia entre 4. Un contador de 4 etapas puede usarse para dividir entre 16 ( 2n, N = número de flip-flops ), se pueden agregar más etapas si se requiere dividir entre una potencia de 2 más alta. 3DUD GLYLGLUHQWUHFXDOTXLHUHQWHURVHSXHGHXVDUHOVLJXLHQWHPpWRGR Encontrar el número n de flip-flops requeridos : 2n-1 <= N <= 2n 'RQGH N = longitud del ciclo del contador. Si N no es una potencia de 2, usar la siguiente potencia superior de 2. 2. Conectar todos los flip-flops como contador tipo rizado. 3. Encuentre el número binario N – 1. 4. Conecte todas las salidas de los flip-flops que son 1 en la cuenta N-1 como entradas en el bloque NAND. También conecte el pulso de reloj al bloque NAND. 5. Conecte la salida del bloque NAND a las entradas de preenergizado (clear) de todos los flip-flops para los cuales Q = 0 en la cuenta N-1. Figura 3. Bernardo Núñez Montenegro. 3 UNPRG Escuela Sup. de Ing. de Sistemas. SISTEMAS DIGITALES. El contador se restablece de la siguiente manera: En la transición positiva del pulso N de reloj, todos los flip-flops tienen el valor de 1 lógico y en la parte final del mismo pulso o sea en la parte de transición negativa, todos los flip-flops cuentan para el estado 0, es decir, que el contador se restablece y empieza de nuevo el ciclo. Para N = 10: • 23 <= 10 <= 24. Entonces, se requieren 4 flip-flops. • N = 10; 1010 • N – 1 = 9 : 1001 • Conecte como se muestra en la Fig anterior. Cada flip-flop en un contador, como el de la Figura, tiene un peso o valor decimal específico asignado. El flip-flop A tiene un peso de 20 ( 1 ), cuando su salida está en 1 lógico. El flip-flop B tiene un peso de 21 ( 2 ), C tiene un peso de 22 ( 4 ), y D tiene un peso de 23 ( 8 ). El número almacenado en el contador en cualquier tiempo específico se puede determinar por la suma de los pesos decimales de los flip-flops que tengan valor de 1 lógico. Un contador que cuenta en forma binaria estándar y recicla cada 10 pulsos, es referido como contador BCD 8-4-2-1 (binary- code decimal). En muchos paquetes de contadores en circuitos integrados, las líneas de preenergizado mostradas en la Figura, no existen; sólo se dispone de una línea de borrado común ( reset). &217$'25(66,1&521,&26 El contador sincrónico elimina los retrasos acumulativos de los flip-flops que se vieron en los contadores tipo rizado. Todos los flip-flops en el contador sincrónico están bajo el control del mismo pulso de reloj. La velocidad de repetición está limitada sólo por el retraso de uno de los flip-flops, más el retraso introducido por los bloques de control. El diseño de contadores sincrónicos para cualquier base numérica diferente de alguna potencia de 2 se dificulta más que los contadores tipo rizado, pero el diseño se simplifica mediante el uso de la técnica de mapas de Karnaugh. En la Figura 4, muestra un contador sincrónico de 4 dígitos binarios con cargo en paralelo. El cargo en paralelo, también conocido como “ cargo adelantado” es el más rápido de los dos métodos de control de flip-flops. De acuerdo con la tabla de estados, el flip-flop A se requiere que cambie de estado con la ocurrencia de cada pulso de reloj, el flip-flop B cambia cuando QA = 1; C cambia de estado cuando Bernardo Núñez Montenegro. 4 UNPRG Escuela Sup. de Ing. de Sistemas. SISTEMAS DIGITALES. QA = Qn = 1, y D cambia de estado cuando QA = QB = QC = 1. El control del flipflop A se puede lograr mediante la conexión de JA y KA a un 1 lógico; el control del flip-flop B se logra con la conexión de JB y KB a QA; el control del flip-flop C se logra mediante la salida invertida de un bloque NAND de 2 entradas, cuyas entradas son QA y QB. El flip-flop D se controla en la misma forma que C, excepto que las entradas del bloque NAND son QA, QB y QC. Figura 4. Se pueden diseñar contadores sincrónicos para conteo binario con una longitud de ciclo 2n una vez que se ha visto el patrón de la lógica de control; para ciclos de longitud diferente de 2n, la lógica de control algunas veces puede llegar a hacerse un tanto confusa y ésta es la razón por la que las matrices de control ( mapas de Karnaugh ) tienen que dibujarse para cada uno de los flip-flops. En la tabla se presentan las matrices de control para el contador sincrónico de 4 dígitos binarios de la Figura 4 Bernardo Núñez Montenegro. 5 UNPRG Escuela Sup. de Ing. de Sistemas. SISTEMAS DIGITALES. 275267,326'(&217$'25(6 • Contadores en Anillo. • Contadores Jonson. • Contadores de decadas. • Contadores Ascendente /descendente. Bernardo Núñez Montenegro. 6