Crónometro Digital

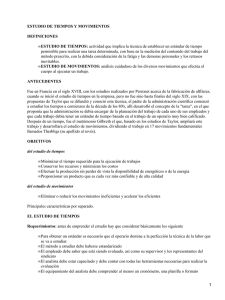

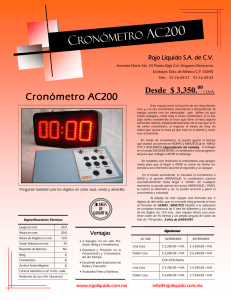

Anuncio

CODISEÑO HARDWARE/SOFTWARE EN FPGA Crónometro Digital Funcionamiento del dispositivo El dispositivo a diseñar es un reloj digital programable de 24 horas, con alarma, que puede también funcionar como cronómetro ascendente o descendente, pudiéndose programar la cuenta atrás. Los modos de funcionamiento se controlan con los interruptores 0, 1 y 2 (ver Figura 1). El rango de valores del dispositivo es de 00:00:00.00 a 23:59:59.99 horas, minutos, segundos y centésimas de segundo. El interruptor 2 activa o desactiva el modo de programación en cualquier modo: en modo reloj sirve para programar la hora actual, en modo alarma para establecer la hora a la que se activará esta, y en el modo cronómetro descendente fija el valor para la cuenta atrás. El modo de programación se activa cuando el interruptor está en posición “1” (o levantado). Los pulsadores permiten el desplazamiento y la programación de cada uno de los dígitos. El pulsador 2 va pasando secuencialmente por cada dígito, lo que se muestra con el punto decimal, y también por los leds 2 a 0, que muestra el valor en binario de la posición actual. Con los pulsadores 0 y 1 se aumenta y disminuye respectivamente el valor del dígito seleccionado. Según la posición y el valor de la cuenta actual, se permitirán unos valores u otros de programación (por ejemplo, no se permitirá pasar de 3 horas cuando las décimas de hora sean 2, para no sobrepasar las 24 horas). En modo alarma sólo se programan horas y minutos. El interruptor 1 permite cambiar entre los modos reloj y cronómetro: levantado selecciona modo reloj, y bajado modo cronómetro. En modo cronómetro, los pulsadores 0 y 1 se utilizan para iniciar y parar la cuenta respectivamente. En modo ascendente y descendente se podrá parar y reanudar la cuenta con ambos pulsadores. En modo descendente hay que programar primero el valor de la cuenta atrás antes de poder iniciarla. El interruptor 0 distingue, en modo cronómetro, entre modo ascendente (levantado) o cuenta atrás (bajado), y en modo reloj activa o desactiva la alarma. En modo alarma, cuando la hora actual coincide con el valor programado para ésta, los leds 7 a 0 se encienden y apagan una vez por segundo. Por último, en los modos de cronómetro el pulsador 3 actúa como botón de clear de la cuenta. 1/3 CODISEÑO HARDWARE/SOFTWARE EN FPGA Señales externas e internas Para la interfaz del dispositivo se proponen las siguientes señales: entity Cronometro is Port ( modo : in STD_LOGIC_VECTOR (2 downto 0); -- Modos de funcionamiento: (Interruptores 2 1 0) -- 0 1 1 : Funcionamiento como reloj digital. -- 1 1 1 : Modo de programación del reloj digital. -- 0 0 0 : Cronómetro de A a cero (cuenta atrás). -- 1 0 0 : Programación del valor inicial para cuenta atrás. -- 0 0 1 : Cronómetro hacia adelante. -- 1 1 0 : Modo de programación de alarma del reloj digital. -- 0 1 0 : Activación de alarma del reloj digital. clk : in STD_LOGIC; -- Señal del reloj interno. clear : in STD_LOGIC; -- Señal de reset de los cronómetros (Pulsador 3). posicion_cambio : in STD_LOGIC; -- Cambiar posicion en modos de programación (Pulsador 2). disminuir : in STD_LOGIC; -- Disminuir valor o parar cronómetro (Pulsador 1). aumentar : in STD_LOGIC; -- Aumentar valor o iniciar cronómetro (Pulsador 0). leds_posicion : out STD_LOGIC_VECTOR (7 downto 0); -- Informacion en los 8 leds. an : out STD_LOGIC_VECTOR (3 downto 0); -- Control de los 7-segmentos. a,b,c,d,e,f,g,punto : out STD_LOGIC); -- Salidas de los 7-segmentos. end Cronometro; Las entradas y salidas se mapean de la siguiente forma: Tabla 1 2/3 CODISEÑO HARDWARE/SOFTWARE EN FPGA Diagrama de la interfaz: Figura 1 Calificación de la práctica por hitos • • • • • • Cronómetro ascendente con reset y stop: 5 Cronómetro ascendente con desplazamiento de display: 6 Cronómetro descendente con carga de valor inicial: 7 Modo reloj (visualización y configuración): 8 Modo alarma: 9 Otras prestaciones extras añadidas por el diseñador: 10 3/3