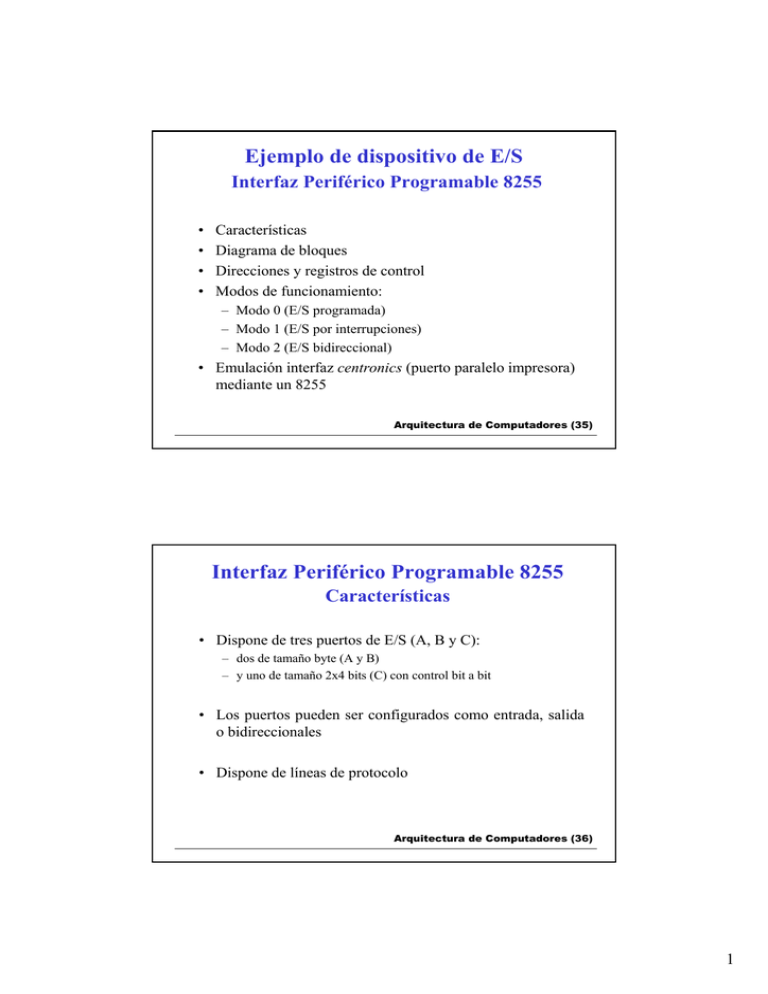

Ejemplo de dispositivo de E/S Interfaz Periférico Programable 8255

Anuncio

Ejemplo de dispositivo de E/S Interfaz Periférico Programable 8255 • • • • Características Diagrama de bloques Direcciones y registros de control Modos de funcionamiento: – Modo 0 (E/S programada) – Modo 1 (E/S por interrupciones) – Modo 2 (E/S bidireccional) • Emulación interfaz centronics (puerto paralelo impresora) mediante un 8255 Arquitectura de Computadores (35) Interfaz Periférico Programable 8255 Características • Dispone de tres puertos de E/S (A, B y C): – dos de tamaño byte (A y B) – y uno de tamaño 2x4 bits (C) con control bit a bit • Los puertos pueden ser configurados como entrada, salida o bidireccionales • Dispone de líneas de protocolo Arquitectura de Computadores (36) 1 Interfaz Periférico Programable 8255 Diagrama de bloques Arquitectura de Computadores (37) Interfaz Periférico Programable 8255 Direcciones y registros de control Arquitectura de Computadores (38) 2 Interfaz Periférico Programable 8255 Modo 0 (E/S Programada) • Se utilizan los tres puertos (A,B,C) como simples registros donde leer y escribir. La CPU y el/los dispositivo/s externo/s correspondiente/s se encarga/n de leer/escribir de acuerdo a un determinado protocolo previamente definido ¾El puerto A (8 bits) se configura como entrada o salida con el bit D4 del registro de control ¾El puerto B (8 bits) se configura como entrada o salida con el bit D1 del registro de control ¾El puerto C alto (4 bits) se configura como entrada o salida con el bit D3 del registro de control ¾El puerto C bajo (4 bits) se configura como entrada o salida con el bit D0 del registro de control Arquitectura de Computadores (39) Interfaz Periférico Programable 8255 Cronograma Modo 0 Arquitectura de Computadores (40) 3 Interfaz Periférico Programable 8255 Modo 1 (E/S por interrupciones) • En este modo se utiliza el protocolo Handshake ¾El puerto A (8 bits) se configura como entrada o salida con el bit D4 del registro de control ¾El puerto B (8 bits) se configura como entrada o salida con el bit D1 del registro de control ¾El puerto C contiene las señales del protocolo Arquitectura de Computadores (41) Interfaz Periférico Programable 8255 Modo 1 (E/S por interrupciones). Configuración de entrada Señales de protocolo cuando el puerto está configurado como entrada STBA (strobe input): Un cero en esta línea de entrada indica que hay dato disponible en el puerto A (activada por el dispositivo externo) IBFA (input buffer full): Un uno en esta línea de salida indica que el dato ya ha sido cargado en el registro del puerto A. IBFA se desactiva cuando se desactiva STBA (el dispositivo externo da su confirmación) y se produce el flanco de subida de la señal RD (dato leído por la CPU) Las señales STBB , IBFB son funcionalmente equivalentes Arquitectura de Computadores (42) 4 Interfaz Periférico Programable 8255 Modo 1 (E/S por interrupciones) Configuración de salida Señales de protocolo cuando el puerto está configurado como salida OBFA (output buffer full): esta línea de salida se pone a cero (activa en baja) para indicarle al dispositivo que la CPU ha escrito un dato en el puerto A. Se activa con el flanco de subida de la señal WR (escritura finalizada) y se desactiva con la confirmación del dispositivo (ACKA) ACKA (acknowledge input): un cero en esta entrada indica que los datos del puerto A han sido leídos por el dispositivo externo. Esencialmente es una respuesta del dispositivo periférico indicando que ha sido recibido el dato enviado por la CPU Las señales OBFB y ACKB son funcionalmente equivalentes Arquitectura de Computadores (43) Interfaz Periférico Programable 8255 Modo 1 (E/S por interrupciones). Interrupciones Interrupciones • Señales de interrupción se pueden generar en los puertos A y B tanto si están configurados como entrada (la CPU debe leer un dato) como si lo están como salida (la CPU ya puede escribir un nuevos dato) • El bit 4 del puerto C (PC4) es el bit de habilitación de interrupción del puerto A:INTEA. El del puerto B es el bit 2 (PC2): INTEB • Para que el 8255 genere una interrupción asociada al puerto A (señal INTRA) cuando está configurado como entrada, se debe cumplir que: STBA es 1, IBFA es 1 e INTEA es 1 (semejante para el puerto B) • Para que el 8255 genere una interrupción asociada al puerto A (señal INTRA) cuando está configurado como salida, se debe cumplir que: ACKA es 1, OBFA es 1 e INTEA es 1 (semejante para el puerto B) Arquitectura de Computadores (44) 5 Interfaz Periférico Programable 8255 Modo 1 (E/S por interrupciones). Registros y señales Arquitectura de Computadores (45) Interfaz Periférico Programable 8255 Cronograma Modo 1 1 2 Comienzo de la ejecución de los manejadores de interrupción 5 3 4 1 2 4 3 5 Arquitectura de Computadores (46) 6 Interfaz Periférico Programable 8255 Modo 2 (E/S bidireccional) • El PUERTO A funciona de forma bidireccional. Es como un doble modo 1. El PUERTO B no tiene este modo ¾ Los cinco líneas superiores del puerto C contienen las señales de protocolo Señales de protocolo (semejantes a las descritas en el modo 1) STB (strobe input) IBF (input buffer full) ACK (acknowledge) OBF (output buffer full) INTR Arquitectura de Computadores (47) Interfaz Periférico Programable 8255 Modo 2 (E/S bidireccional). Registro y señales Arquitectura de Computadores (48) 7 Interfaz Periférico Programable 8255 Cronograma Modo 2 Arquitectura de Computadores (49) Interfaz Periférico Programable 8255 Emulación interfaz centronics (puerto paralelo impresora) Arquitectura de Computadores (50) 8