CONTADORES ASÍNCRONOS Binario de 3 bits Binario de 3 bits

Anuncio

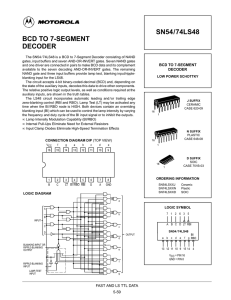

DEPARTAMENTODEAUTOMÁTICA ! ARQUITECTURAYTECNOLOGÍADECOMPUTADORES DEPARTAMENTO*DE*AUTOMÁTICA* ARQUITECTURA*Y*TECNOLOGÍA*DE*COMPUTADORES* GradoenIngeniería Informática Grado*en*Ingeniería* FUNDAMENTOSDE Informática* TECNOLIGÍADE COMPUTADORES FUNDAMENTOS*DE* TECNOLIGÍA*DE* COMPUTADORES* Curso*Académico*2012/2013! ! ! CONTADORES ASÍNCRONOS CONTADORES Binario de 3 bits ASÍNCRONOS Binario de 3 bits ! ! ! ! ! ! ! ! ! Binario de 4 bits Binario de 4 bits Flip-flops activos en flanco de bajada (atención a las entradas de Flip-flops activos en flanco a las entradas de clock de los flip-flops, ahorade esbajada Q y no(atención Q negado) clock de los flip-flops, ahora es Q y no Q negado) ! ! ! ! ! ! ! ! ! ! Contador de décadas asíncrono Contador de décadas asíncrono ! ! ! ! ! ! ! ! ! ! ! Contador módulo 12 asíncrono SN74LSXXD SOIC pinouts (Connection Diagram) as the Dual In-Line Package. GND = PIN 10 he device. s than 100 ns. LOGIC DIAGRAM CONNECTION DIAGRAM DIP (TOP VIEW) LS92 SYMBOL LS93 SN54/74LS90 • SN54/74LS92 • SN54/74LS93 SN54/74LS93 LS92 CP0 J 14 Q J CP KC Q D LS90 Q J CP KC Q D Q J CP KC Q D CP KC Q D AND LS93 LS92 MODE 1 SELECTION 14CP CP0 MODE SELECTION 1 RESET / SET INPUTS OUTPUTS 6 CP1 1 MR 1 12 11 MR1 MR2 MR MS1 MS2MR QQ Q Q 0 QQ 2 7 0 11Q2 Q23 3 Q Q 1 H H L L 0L L L X H H X L L L L 1 2 L X X H H L L H H L X L X 2 3 12 9Count 8 11 X L X L Count L X X L VCC = PIN 5Count X L L X GND = PIN Count 10 Q0 Q1 Q2 Q3 12 11 9 8 RESET INPUTS 9 ODE DIAGRAM HLOGIC = HIGH Voltage Level L = LOW Voltage Level SELECTION X = Don’t Care NC = PIN 4, 6, 7, 13 LS92 AND LS93 NPUTS OUTPUTS LS TTL DATA S1 MS2 -90 H X L H X L L X Q0 Q1 Q2 Q3 14 CP0 L L LS90 L L L L L L BCD COUNT SEQUENCE H L L H Count OUTPUT 1 COUNT Count Q0 Q1 QCP 2 1 Q3 2 Count 0 L L LMR1 L Count 1 H L LMR2 L3 2 L H L L 3 H H L L 4 L L H L 5 H L H L 6 L H H L 7 H H H L 8 L L L H 9 H L LS92 L H OUTPUTS 8 MR Q 2 1 MR2 QQ 0 3 Q1 Q2 H H L L L L = PIN H NUMBERS Count Count HVCC =LPIN 5 Count LGND =LPIN 10 4/74LS90 • SN54/74LS92 • SN54/74LS93 = PIN 5 = PIN 10 PINS LS90 2, 3, 4, 13 Q L L L L L L L H H to Input 1 2 3 4 5 6 7 8 9 10 11 H L H L H L H L H L H L H H L L L L H H L L NOTE: Output Q0 is connected to Input CP1. H L H L H L H L H L H L H L H L H H L L H H L L H H L L H H L H L H L H L H L H L H L H L H FAST AND LS TTL DATA 5-93 12 Q0 NC 4 11 Q1 VCC 5 10 GND MR1 6 9 Q2 MR2 7 8 Q3 L L H H L L H H L L H H L L H H CP1 1 14 CP0 MR1 2 13 NC MR2 3 12 Q0 NC 4 11 Q3 VCC 5 Q3 6 NC L 10 GND 9 Q1 L L L 7 8 Q2 NC L L L L H NCL= NO INTERNAL CONNECTION H NOTE: L H TheLFlatpak version has the same H pinouts L (Connection Diagram) as Dual In-Line Package. L the H L H L H L H H H H H H H H H L NOTE: L Output Q is connected to Input 0 L CP1.L L L H L H L H L H L L H L H L H L H H H H H H H H H NOTE: Output Q0 is connected to Input CP1. NC 3 CONNECTION DIAGRAM DIP (TOP VIEW) H = HIGH 0 VoltageLLevelL9 12 L = LOW 1 VoltageHLevelL X =QDon’t 0 2 Care L Q1H 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 13 NC NOTE: The Flatpak version has the same pinouts (Connection Diagram) as the Dual In-Line Package. RESET OUTPUTS INPUTS J Q J Q J Q J Q Q0 Q1CP Q2 Q3 CP 2 CP MR1 MRCP LS92 LS93 KC Q H K C Q LTABLE KC Q KC Q H L L L TRUTH TRUTH TABLE D D D D Count L H OUTPUT OUTPUT Count H L COUNT COUNT Count L L Q0 Q1 Q2 Q3 Q0 Q1 Q2 L L L L L H H H H H H NC 2 NC = NO INTERNAL CONNECTION L MODELS93 SELECTION L L L H H L L L L H H 14 CP0 Q3 H = HIGH Voltage Level L = LOW Voltage Level X = Don’t Care 0 L L 8 11 1 L L Q Q3 Level 2 L L2 evel 3 3 H H L L = PIN NUMBERS 4 4 L L H L 5 H L H L VCC = PIN 5 5 6 L L L H GND = PIN 10 6 7 7 H L L H 8 8 L H L H 9 9 H H LLS93 H 10 10 L LTRUTH H TABLE H NCE NOTE: Output Q0 is TRUTH connected TABLE to Input 11 11 H L H H CP1 for BCD count. T OUTPUT NOTE: Output Q is connected OUTPUT FAST AND LS TTL 12 DATA to Input 0 COUNT COUNT 13 CP . Q2 Q3 Q0 Q1 Q2 Q31 Q0 Q15-91 Q2 Q3 14 0 0 L L L L L L L L L L15 L L L H H H H L L CP1 1 A B C D E F 0 1 CONTADORES SÍNCRONOS J Q J CLK Binario de 4 bits K 2 Q J CLK Q Q J CLK K Q Q CLK K Q K Q reloj Q0 Q1 Q2 Q3 5 reloj CLK K Q 10 16 J 7 Q 15 9 6 CLK K Q 14 12 Q0 J S 2 1 Q R 12 4 Q 11 CLK K 10 8 14 Q 11 R K Q 3 CLK J S 7 6 S 9 R 15 Q 3 16 J 8 1 R 4 4 S 2 3 Q1 Q2 Q0 Q3 Q1 Q2 6 up/down 7 reloj J Q J CLK K Q J CLK Q K Q CLK Q K Q Q0 8 Q1 reloj Q2 9 Q3 A B C D E F Contador de décadas síncrono A B C D E F 0 1 J Q J CLK K 2 Q J CLK Q K Q J Q CLK K Q K Q reloj Q0 Q1 Q2 Q3 J0 = K0 = 1 reloj reloj 1 2 CLK K Q 10 16 3 Q0 4 5 7 Q 15 9 6 CLK K Q 14 12 6 7 Q1 8 J S 12 J Q R 1 Q 11 CLK K 10 8 4 J3 = K 3 = Q0Q1Q2 + Q0Q3 14 Q 11 3 K Q R CLK J S 7 6 J 2 = K 2 = Q0Q1 S 9 3 16 15 Q R 1 8 4 J R 4 S 2 J1 = K1 = Q0 Q3 2 3 5 Q CLK 9 0Q2 1 Q3 Q0 Q0 Q1 Q2 6 up/down Q1 Q2 J Q J Q J Q 7 CLK Q3 K CLK Q K CLK Q K Q 8 reloj 9 A B C D E F 5 K Q 10 16 J 7 Q 15 9 6 CLK K Q 14 12 J S 1 Q R 2 4 8 12 11 Q 11 CLK K 10 8 14 Q Q CLK R K J 3 6 S 7 9 S 15 Q CLK R J 3 16 S 2 1 R 4 4 Contador síncrono ascendente/descendente reloj Q0 Q1 Q2 Q0 Q3 Q1 Q2 6 up/down J Q J Q J Q 7 CLK CLK K Q K CLK Q K Q 8 reloj 9 up/down A reloj B 1 2 C 3 4 5 D 6 Q0 Q1 Q2 5 E 4 3 2 F 3 4 G 5 6