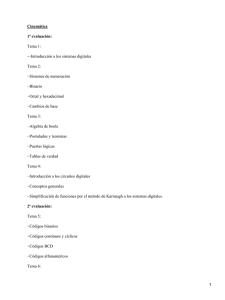

Riesgos en circuitos combinacionales

Anuncio

Riesgos en circuitos combinacionales EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 1 Riesgos en circuitos combinacionales Riesgos en circuitos combinacionales Ejemplo EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 2 • Una función lógica tiene el siguiente mapa: B A 1 0 1 3 2 1 4 5 7 6 1 1 C • El modelo lógico es: f ( A, B, C ) = B C + AC Riesgos en circuitos combinacionales El circuito lógico EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 3 Riesgos en circuitos combinacionales Observaciones EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 4 • Con ABC= 101 la compuerta Y2 genera un 0 a la salida y la Yl genera un 1; • Con ABC= 100 es Yl la que genera un 0, mientras Y2 genera un 1. • Cuando C cambia de 1 a 0, a la compuerta Y1 le afecta inmediatamente ese cambio, mientras que para la Y2 ese cambio ha de propagarse a través de un inversor antes de que llegue a la salida. • Por tanto, Y1 cambia de 1 a 0 antes de que Y2 haya cambiado de 0 a 1; en otras palabras, momentáneamente las dos entradas a la compuerta O (salidas de Y1 e Y2) valdrán 0, y la salida del circuito momentáneamente tomará el valor 0. • Este comportamiento que se acaba de describir es un ejemplo sencillo de riesgo estático. Riesgos en circuitos combinacionales Riesgo estático EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 5 • Riesgo Estático: Se dice que en un circuito lógico se presenta un riesgo estático si en una transición en la que la salida deba permanecer en el valor V, momentáneamente toma el valor V. • Se le llama al cero o al uno si se produce cuando se cambia de uno a cero o de cero a uno. Riesgos en circuitos combinacionales Riego Dinámico EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 6 • También puede ocurrir que en una determinada transición en las entradas. La salida deba cambiar de 0 a 1 (o de 1 a 0), pero momentáneamente regresa al valor original, efectuando el recorrido 0⇒1⇒0⇒1 (1⇒0⇒1⇒0); en este caso se dice que hay un riesgo dinámico. Riesgos en circuitos combinacionales Razones por las que aparecen los riesgos EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 7 • Cuando el riesgo (estático o dinámico) ocurre en una transición de las entradas en la que sólo cambie una de las entradas, como en el caso anterior, se trata de un riesgo lógico. • Estos riesgos ocurren por los diferentes retardos en la propagación de una misma señal en el circuito con el que se realiza la función. • En el circuito anterior la señal C se propaga por dos caminos diferentes, con retardos desiguales, de manera que en un determinado instante la variable toma el mismo valor en diferentes partes del circuito, y por ello aparecen los riesgos. Riesgos en circuitos combinacionales Razones por las que aparecen los riesgos EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 8 • Por lo general el riesgo se presenta en una transición entre dos celdas adyacentes del mapa de Karnaugh, cubiertas por agrupaciones de áreas, y lo que ocurre es que se sale de la celda antes de haber entrado en la otra celda. • Si los dos unos de dos celdas estuvieran cubiertos por una misma agrupación, no habría riesgos. • Se tiene un procedimiento inmediato para eliminar los riesgos estáticos a los unos: basta incluir todos los implicantes primarios de la función que cubran dos o más unos. • Para eliminar los riesgos estáticos a los ceros, el procedimiento es el mismo. Riesgos en circuitos combinacionales Razones por las que aparecen los riesgos EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 9 • Si los riesgos dinámicos son consecuencia de los riesgos estáticos, una vez eliminados los riesgos estáticos, también se habrán eliminado los riesgos dinámicos. Riesgos en circuitos combinacionales CONCLUSION EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 10 • Si se diseña un circuito combinacional como una red con dos niveles en forma AND a OR, para que en el circuito no aparezcan riesgos lógicos hay que incluir todos los implicantes primarios de la función. • Existen riesgos siempre que, en una realización concreta, se empleen términos que son adyacentes en el mapa de Karnaugh . Riesgos en circuitos combinacionales Control de riesgos EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 11 • La eliminación de riesgos es un problema complejo debido al gran número de combinaciones de los distintos retardos. • Los riesgos pueden ser eliminados en ocasiones mediante retardos insertados en lugares adecuados. • También se puede enfrentar el problema añadiendo términos redundantes que hagan puente entre los causantes del riesgo en el mapa de Karnaugh . Riesgos en circuitos combinacionales Control de riesgos EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 12 • Los glitches desaparecen cuando las señales de entrada se estabilizan y se consumen los tiempos de propagación. • En vista de que son difícil de que desaparezcan los glitches lo mejor es dejar que existan y diseñar para que los eventos claves se produzcan una vez que han desaparecido. • Para eliminar la posibilidad de fenómenos aleatorios dinámicos se realiza al minimizar su función por el método de Karnaugh, porque la expresión suma de productos obtenida nunca obtendrá el producto a·a (o la suma a+a) si se trata de una expresión de producto de sumas. Riesgos en circuitos combinacionales Control de riesgos EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 13 • Se tiene que garantizar que no quede ninguna pareja de 1's adyacentes sin que estén cubiertos por algún implicante común. Por lo tanto, en la fórmula lógica deberán aparecer los implicantes esenciales y no esenciales necesarios para garantizar que no exista ninguna pareja de 1’s (0’s) adyacentes que no esté cubierta por un mismo implicante. • Alternativas para evitar los riesgos – Inserción de retardos hardware: Su valor es difícilmente controlable y varía con las condiciones de funcionamiento, pudiendo dar lugar a nuevos riesgos. – Inserción de lógica redundante: Permite eliminar únicamente los riesgos lógicos. – Inserción de lógica registrada: No elimina los riesgos, sino su efecto. Consiste en muestrear la lógica cuando ha finalizado el régimen transitorio -y por tanto ya no existen glitchesalmacenando los estados de salida en flip-flops. Riesgos en circuitos combinacionales Riesgos funcionales EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 14 • Cuando las transiciones en las entradas que producen un riesgo suponen el cambio de más de una entrada, entonces se trata de un riesgo funcional. Riesgos en circuitos combinacionales Ejemplo EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 15 • Sea la siguiente función lógica mostrada en el mapa K. 1 1 1 1 1 1 Riesgos en circuitos combinacionales Observaciones EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 16 • De la transición 0000 a 0101 hay un riesgo funcional estático a los unos, pues nunca las dos entradas BD cambiarán con absoluta simultaneidad de 0 a 1. • Por lo tanto la transición de la celda 0000 a la 0101 se hará a través de la 0001 o de la 0100, y en ambos casos la función toma momentáneamente el valor 0. • De igual forma, en la transición de la celda 0001 a la 0100 habrá un riesgo funcional estático c los ceros. En la transición de 0101 a 1110 hay un riesgo funcional dinámico, pues las celdas por las que pasará son: 0101⇒0111⇒0110⇒1110 o 0101⇒0111⇒1111⇒1110 o 0101⇒1101⇒1111⇒1110, y en todos los casos en que las salidas son: 1⇒0⇒1⇒0. Riesgos en circuitos combinacionales Observaciones EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 17 • Los riesgos funcionales no dependen de la forma de realización, no dependen del circuito concreto y son inevitables • Son fáciles de anticiparlos y prever sus repercusiones. • Implican el cambio en más de una variable; por ejemplo, si se aplica el principio de que nunca dos variables cambiarán simultáneamente, se puede analizar adecuadamente cualquier circuito combinacional, o en otras palabras, los riesgos funcionales se evitan limitando los cambios en las entradas a una sola variable. • Lo normal es que estas excursiones momentáneas al 0 y al 1 que se dan en los riesgos sean de muy corta duración, lo que se conoce como pulso espurio (glitches). En cualquier caso la magnitud de estos pulsos erróneos dependen de los parámetros del circuito, del tipo de compuertas que se estén utilizando, etc.