Departamento de Ciencias Computacionales

Anuncio

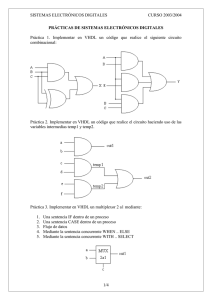

UNIVERSIDAD DE GUADALAJARA CENTRO UNIVERSITARIO DE CIENCIAS EXACTAS E INGENIERÍAS DIVISIÓN DE ELECTRÓNICA Y COMPUTACIÓN DEPARTAMENTO DE CIENCIAS COMPUTACIONALES DATOS GENERALES CLAVE DE MATERIA : CC408 NOMBRE DE LA MATERIA : TIPO : CURSO TEÓRICO/ PRÁCTICO CARÁCTER DEL CURSO : OPTATIVA AREÁ DE FORMACIÓN : OPTATIVA ABIERTA PRERREQUISITOS : ORGANIZACIÓN DE COMPUTADORAS II DEPARTAMENTO DE ADSCRIPCIÓN : CIENCIAS COMPUTACIONALES ACADEMIA Simulación de Sistemas Digitales : SISTEMAS DIGITALES CARGA HORARIA GLOBAL : 80 HORAS CARGA HORARIA SEMANAL : 4 HORAS VALOR EN CRÉDITOS : FECHA DE ACTUALIZACIÓN CALENDARIO DE APLICACIÓN 11 : JULIO/2004 : 2006A OBJETIVO GENERAL: Al finalizar el curso, el alumno tendrá los conocimientos fundamentales de las herramientas requeridas en el desarrollo de dispositivos programables, así mismo comprenderá la el flujo de diseño de un ASIC, de tal manera que tendrá capacidad de diseñar e implementar sistemas para aplicación especifica en algunas aplicaciones de propósito particular. UNIVERSIDAD DE GUADALAJARA DIVISIÓN DE ELECTRÓNICA Y COMPUTACIÓN DEPARTAMENTO DE CIENCIAS COMPUTACIONALES Simulación de Sistemas Digitales CONTENIDO TEMÁTICO PRINCIPAL 1 Módulo 1: Introducción al VHDL, 4 horas Objetivo: Al término de este módulo, el alumno conocerá la historia del diseño de dispositivos programables (FPGA y CPLDs) y adquirirá la capacidad de evaluar los diferentes circuitos programables y programas (software especializado) y podrá evaluar diferentes familias de dispositivos programables. 1.1.- Breve reseña histórica 1.2.- VHDL vs MSI 1.3.- ¿Qué es un PLD? 1.4.- Conociendo el lenguaje VHDL 1.5.- Concurrencias y señales 1.6.- ¿Qué es VLSI y ASIC? 1.7.- Diversas compañías fabricantes de dispositivos programables y herramientas de VHDL: 1.7.1.- Generalidades de cada compañía 1.7.2.- Maxplus II, http://www.altera.com (ALTERA) 1.7.3.- Warp, http://www.cypress.com (Cypress Semiconductors) 1.7.4.- Foundation, http://www.xilinx.com (Xilinx Inc.) 1.7.5.- Desktop, http://www.actel.com (Actel) 1.7.6.- Synopsys, http://www.synopsys.com (Synopsys) 2 Módulo 2: Unidades Básicas de diseño, 4 horas Objetivo: El alumno comprenderá y usará las diferentes formas de declarar señales de entrada y salida de un dispositivo programable y podrá reproducir un programa básico en este lenguaje. 2.1. Cómo se declara una entidad 2.1.1. Modos 2.1.2 . Tipos 2.2. Cómo se declara una arquitectura 2.2.1. Estilos 3 Módulo 3: Objetos, tipos de datos y operaciones, 4 horas Objetivo : En esta etapa el alumno tendrá la capacidad de conocer los elementos básicos de las señales y tipos de ellas usadas en los programas de VHDL. 3.1.- Objetos 3.2.- Identificadores 3.3.- Palabras reservadas 3.4.- Símbolos especiales 3.5.- Tipos de datos 3.6.- Expresiones y operadores 3.7.- Atributos de los vectores 3.8.- Declaración de constantes, señales y variables 3.8.1.- Constantes 3.8.2.- Variables 3.8.3.- Señales 4 Módulo 4: Gramática del Lenguaje I, 4 horas Objetivo: El alumno adquirirá la capacidad de desarrollar programas de VHDL básicos, con estructuras de control para la implementación de diversos sistemas 4.1.- Sentencias secuenciales 4.2.- Asignación a señal 4.3.- Asignación a variable 4.4.- Sentencia if 4.5.- Sentencia case 4.6.- Sentencia loop 4.7.- Sentencia exit 4.8.- Sentencia next 4.9.- Sentencia null 4.10.- Sentencia wait 4.11.- Sentencia wait until 5 Módulo 5: Gramática del Lenguaje II, 4 horas Objetivo: El alumno adquirirá la capacidad de desarrollar programas de VHDL básicos secuenciales y concurrentes, con estructuras de control para la implementación de diversos sistemas 6.1.- Sentencias concurrentes 6.2.- Sentencia process 6.3.- Asignación concurrente a señal 6 6.4.- Asignación concurrente condicional 6.5.- Asignación concurrente con selección Módulo 6: Conceptos avanzados en VHDL, 5 horas Objetivo: El alumno se familiarizará con el uso de algunos beneficios con que cuenta VHDL 6.1.- Buses y resolución de señales 6.2. Punteros en VHDL 6.3.- Ficheros 7 Módulo 7: VHDL para síntesis, 5 horas Objetivo particular: El alumno diferenciara código sintetizable del que no es sintetizable solo para simulación. 7.1.- Restricciones y consejos en la descripción 7.2.-Construcciones básicas 7.3.- Descripción de maquinas de estado 7.3.1.- Maquinas Mealy 7.3.2.- Maquinas Moore 8 Módulo 8: VHDL para síntesis, 5 horas Objetivo: El alumno aprenderá a usar las ventajas de la herramienta del Maxplus II, contra otros software descriptores de Hardware. 8.1.- Funciones Parametrisadas y su uso en el Maxplus II 8.2.- Funciones Uso de funciones especiales del Maxplus II 9 Módulo 9: Verilog, 5 horas Objetivo: El alumno aprenderá un lenguaje alterno a VHDL, y podrá comparar las ventajas y desventajas. 9.1. 9.2. Introducción 9.1.1. Comentario 9.1.2. Números 9.1.3. Identificadores 9.1.4. Variables Estructura general 9.2.1. Procesos y Operadores 9.2.2. Binarios aritméticos y Relaciónales 9.2.3. Lógicos 9.2.4. Lógica de bit 9.3. Estructuras de control 9.3.1. if 9.3.2. case 9.3.3. for 9.3.4. while 9.3.5. repeat 9.3.6. wait MODALIDAD DE ENSEÑANZA APRENDIZAJE. En la exposición de las explicaciones se recomienda un acercamiento descendente (de los conceptos generales a los detalles) y por acercamientos sucesivos en las tareas construir el modelo de la arquitectura. Practicas: 1. Conocer el ambiente de trabajo de Maxplus II, Esta practica consiste en que el profesor exponga un ejemplo y use las herramientas principales del programa para VHDL y el alumno pueda reproducirlo. 2. El alumno realizara un programa básico de las compuertas ( AND, OR, NOT, XOR ) en un programa de VHDL, donde se utilizara el Maxplus II para evaluar su desempeño, al final de la practica el alumno entregara un reporte escrito (1) 3. El Alumno desarrollara un circuito multiplexor usando arquitectura de flujo de datos ( ecuaciones booleanas) y lo en un programa de VHDL, donde se utilizara el Maxplus II para evaluar su desempeño, al final de la practica el alumno entregara un reporte escrito (1). 4. El Alumno desarrollara un circuito multiplexor usando arquitectura de flujo de datos ( ecuaciones booleanas), este programa en cada una de sus entradas A,B,C y D será un bus de 4 bits y lo en un programa de VHDL, donde se utilizara el Maxplus II para evaluar su desempeño, al final de la practica el alumno entregara un reporte escrito (1). 5. El alumno realizara un sumador por medio de ecuaciones booleanas y lo hará en un programa de VHDL, donde se utilizara el Maxplus II para evaluar su desempeño, al final de la practica el alumno entregara un reporte escrito (1). 6. El alumno realizara un flip-flop en una arquitectura de comportamiento y lo hará en un programa de VHDL, donde se utilizara el Maxplus II para evaluar su desempeño, al final de la practica el alumno entregara un reporte escrito (1) 7. El Alumno desarrollara un circuito contador usando arquitectura comportamental y lo en un programa de VHDL, donde se utilizara el Maxplus II para evaluar su desempeño, al final de la practica el alumno entregara un reporte escrito (1) 8. El Alumno desarrollara un circuito contador ascendente y descendente y con carga de datos usando arquitectura comportamental y lo en un programa de VHDL, donde se utilizara el Maxplus II para evaluar su desempeño, al final de la practica el alumno entregara un reporte escrito (1) 9. El alumno realizara un circuito generador de bits aleatorios usando como base un scrambler usando arquitectura estructural y lo en un programa de VHDL, donde se utilizara el Maxplus II para evaluar su desempeño, al final de la practica el alumno entregara un reporte escrito (1) 10. El Alumno desarrollara un circuito de movimiento de fase de un reloj digital usando arquitectura estructural y lo en un programa de VHDL, donde se utilizara el Maxplus II para evaluar su desempeño, al final de la practica el alumno entregara un reporte escrito (1) 11. El Alumno desarrollara un circuito de movimiento de fase de un reloj digital usando arquitectura estructural y lo en un programa de VHDL, donde se utilizara el Maxplus II para evaluar su desempeño, al final de la practica el alumno entregara un reporte escrito (1) 12. El Alumno desarrollara una maquina de estados para un generador de un bis I2C usando arquitectura mixta y lo en un programa de VHDL, donde se utilizara el Maxplus II para evaluar su desempeño, al final de la practica el alumno entregara un reporte escrito (1). 13. El Alumno desarrollara y simulara una memoria RAM usando arquitectura comportamental y lo en un programa de VHDL, donde se utilizara el Maxplus II para evaluar su desempeño, al final de la practica el alumno entregara un reporte escrito (1). 14. El Alumno desarrollara un procesador de 5 instrucciones y de bus de datos de 4 bits usando arquitectura comportamental y lo en un programa de VHDL, donde se utilizara el Maxplus II para evaluar su desempeño, al final de la practica el alumno entregara un reporte escrito (1) Nota 1.- El reporte contendrá lo siguiente: Diagrama a bloques de la implementación, explicación de forma escrita del funcionamiento de la practica, Código Fuente, Porcentaje de uso del dispositivo CPLD, Diagrama de tiempos, matriz de desempeño, y footprint. Nota 2.- La evaluación de estas practicas es de 0 a 100, y se toman varias características en cuenta, como son el documento de entrega de practica y el correcto funcionamiento y demostración en MAXPLUS II. BIBLIOGRAFÍA BÁSICA 1. VHDL, Lenguaje para síntesis y modelado de circuitos. Fernando Pardo, José A. Boluda, Alfaomega. BIBLIOGRAFÍA ADICIONAL 1. 2. 3. 4. VHDL for Programmable LOGIC, Kevin Skahill, Cypress Semiconductor Lógica digital y diseño de computadoras, T.R. McCalla, Megabyte VHDL Análisis and modeling of digital systems Manuales de los procesadores TMS320C31 y 56000 (Motorola) a. Paginas: i. Maxplus II, http://www.altera.com (ALTERA) ii. Warp, http://www.cypress.com (Cypress Semiconductors) iii. Foundation, http://www.xilinx.com (Xilinx Inc.) iv. Desktop, http://www.actel.com (Actel) v. Synopsys, http://www.synopsys.com (Synopsys) Bibliografía Web: http://www.cucei.udg.mx/~jjme29/Simulacion_de_Sistemas_Digitales.html MATERIAL DE APOYO ACADÉMICO - Acetatos - Laboratorio de computadoras CRITERIOS DE EVALUACIÓN Se evalúa durante el periodo escolar mediante: - 2 Exámenes Departamentales.............50% - Prácticas ......... ....................................50%