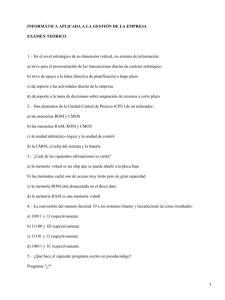

Memoria del ordenador

Anuncio

MEMORIA Sistemas Digitales INTRODUCCION Empezamos por hablar de lo que todo el mundo conoce por memoria. La mayoría de las personas no conocen más que las memorias de almacenamiento externo, como por ejemplo el disco duro o los disquetes, y la memoria RAM debido a que los juegos necesitan una cantidad especifica y ésta bien indicada en la parte trasera de la caja. Por lo demás los PCs poseen otras memorias mucho más importantes y de vital importancia. Empecemos por intentar definir cuanta memoria es suficiente para un equipo. La cantidad justa varía en relación al tipo de trabajo que realiza el ordenador y de las aplicaciones de software que utilice. Así, por ejemplo, aunque la cantidad mínima de RAM para W95 es de 8 Mbytes, dicho sistema operativo (al igual que su hermano mayor, Windows NT) sólo comienza a trabajar de forma eficaz a partir de los 16 Mb. De hecho, el trabajo con los modernos procesadores de texto y hojas de cálculos requiere como mínimo 12 Mb. Sin embargo, los sistemas equipados con 32 Mb se han convertido en sistemas de gama baja para desarrolladores de software y de sistemas operativos, en tanto que los utilizados por las empresas de artes gráficas y multimedia necesitan al menos 64 Mb de memoria, y ya es normal que lleguen a tener 128 Mb o más. La memoria es una parte imprescindible de los ordenadores, ya que sin ella, se pueden dar una infinidad de problemas como por ejemplo la relentización del arranque del sistema operativo, errores que aparecen con frecuencia acusando la carencia de memoria, e incluso hay veces que no se pueden ejecutar programas hasta que previamente se haya cerrado una aplicación anteriormente en uso para liberalizar recursos de la memoria. Sin embargo, en un equipo con suficiente memoria es posible incluso imprimir varios documentos mientras se trabaja con otro programa. En definitiva, la memoria es el componente que más influye en el tipo y cantidad de aplicaciones que podemos ejecutar (aunque no directamente en su velocidad de ejecución), ya que el ordenador usa la RAM (Random Access Memory, o memoria de acceso aleatorio) para mantener provisionalmente las instrucciones y datos necesarios para completar las tareas, lo que permite a la CPU o procesador acceda muy rápidamente a estos. En términos prácticos, esto significa más trabajo acabado y menos tiempo de espera a que el ordenador termine sus operaciones. Una de las primeras cosas que hay que tener en cuenta es la marca de la memoria, ya que una buena marca significa una memoria fiable. Lo principal a tener en cuenta es la calidad de los chips utilizados, sean de DRAM o de otro tipo; verificando que fueron fabricados por una firma fiable (como IBM, Hitachi, Micron, Motorola, Nec, Samsung o Toshiba, Ya que se trata de los mayores suministradores de memorias en el mundo). Oreo punto de interés debería ser la edad de los chips, que en el caso ideal debería ser inferior a un año. ¿QUÉ ES LA MEMORIA? La memoria es el órgano que almacena la información. Las operaciones básicas que se van a efectuar con las memorias son la escritura y la lectura. • La escritura o almacenamiento consiste en grabar los datos en una determinada posición. • La lectura consiste en obtener la información contenida en una posición determinada. 1 La capacidad de las memorias suele darse en octetos o Bytes, es decir, 8 bits. Las medidas de capacidad típicas son • Kilo K (1024 Bytes) • Mega M (1024 kilobytes) • Giga (1024 MegaBytes) JERARQUIA DE MEMORIAS. Se pueden catalogar las memorias en función de los siguientes factores: • Coste por bit • Tiempo de acceso a la información. • Capacidad. El coste por bit decrece rápidamente al aumentar el tiempo de acceso, y por otro lado, a menor velocidad de acceso mayor capacidad. Obviamente, lo ideal es gran capacidad de almacenamiento, tiempo de acceso pequeño y precio reducido. Por ello, la memoria está estructurada en diferentes niveles, siguiendo un criterio jerárquico en función de la probabilidad de uso. Así unos datos poco utilizados estarán almacenados en un nivel jerárquico bajo, de acceso lento con gran capacidad de almacenamiento. Dado que la utilización de la infamación va variando según las necesidades de los usuarios debe producirse un continuo movimiento ascendente y descendente de la información, de tal forma que en los niveles superiores se encuentre disponibles aquellos datos que vayan a ser usados por la unidad central de procesos. En la siguiente tabla se recoge de modo orientativo un típico sistema jerárquico de memoria. JERARQUIA Capacidad en octetos 6−200 8k−512k 1M − 1G 128M−20G Registros Mem.cache Mem.principal Mem.expandida Mem.secundaria por 50M−1G disco Mem.auxiliar por disco 50M−10G Mem.auxiliar por cinta 300k − 8G Tiempo de acceso 1−10 ns 10−30 ns 30−100 ns 100−200 ns Tipo Acceso elemental RAM RAM RAM RAM Palabra. Palabra. Palabra. Varias Palabras. 10 ms A.Directo Sector. 30 ms Minutos A.Directo A.Secuencial Sector. Registro. FUNDAMETOS DE LAS MEMORIAS Una memoria se compone de los siguientes elementos básicos: • El medio o soporte donde se almacenan los datos (ceros o unos). • Un trasductor que coloque en el soporte el dato deseado o que detecte su valor actual. • Un mecanismo de direccionamiento, que permita leer o grabar la información en lugar y tiempos deseados. MEDIO O SOPORTE 2 Para que un medio pueda almacenar datos binarios, ha de cumplir tres condiciones: • Ha de presentar dos estados estables, caracterizados por una magnitud física. • Se ha de poder pasar de un estado a otro aplicando una señal externa. • Se ha de poder detectar el estado existente en todo momento. Los soportes pueden ser discretos o continuos. En el primer caso un dispositivo físico individual almacena cada bit. En el segundo, se almacenan unos bits a continuación de otros en un medio continuo. En general, los medios discretos son más caros, pero requieren trasductores más sencillos y el acceso a los datos es más rápido y simple. En función del tiempo que los datos permanecen grabados se puede efectuar la siguiente clasificación para la memoria: • Duradera: los datos se mantienen de forma permanente, mientras no se realice una operación de escritura. Se dice que la memoria es no volatil. • Volátil: la información desaparece sé de deja de suministrar energía a la memoria. • Con refresco: aunque la memoria este alimentada, los datos se van degradando llegando un momento en que no se pueden leer correctamente. Para que sean útiles, deben refrescarse periódicamente. • De lectura destructiva: la lectura implica el borrado de la información, por lo que cada vez que se realiza una lectura debe volverse a grabar el dato. • Permanente o de solo lectura: contienen siempre la misma información y no pueden borrarse. En contraposición están los soportes de lectura escritura, que se puede grabar cuantas veces se quiera. Una situación intermedia son aquellas que requieren de un proceso especial para ser borradas. TRASDUCTOR Los trasductores son dispositivos generalmente costosos, por lo que debe intentar reducir su número, sin comprometer el tiempo de acceso a los datos. En función de los trasductores pueden hacerse dos grupos de memorias: • Memorias estáticas: el trasductor esta físicamente unido al soporte, existiendo un cableado que emite acceder al dato deseado. Es el caso de las memorias de semiconductor. • Memorias dinámica: el punto de memoria debe posicionarse frente al trasductor para poder ser leído o grabado. En general, los trasductores de las memorias dinámicas trabajan con niveles de señal bajos, por lo que son mas caros que los fijos. Sin embargo, la relación de numero de bits por sensor es mucho más alta, por lo que al final el coste por bit es inferior. MECANISMO DE DIRECCIONAMIENTO La funcion del mecanismo es seleccionar el punto de memoria deseado. Puede establecerse la clasificación siguiente: • Direccionamiento en memorias estáticas: direccionamiento y cableado. En una memoria estática el mecanismo de direccionamiento es inherente a su propia construcción. El cableado de los trasductores permite activar el punto de memoria deseado. Por eso se habla de direccionamiento cableado. Se considera que la memoria tiene palabras de n bits y que para indicar la dirección buscada se necesitan m bits, de forma que 2m sea igual o mayor que el tamaño total de la memoria. Este tipo de acceso se 3 llama acceso por palabra y el tiempo de acceso es fijo. Estas memorias reciben también el nombre de RAM. Tenemos dos tipos de direccionamiento: • Direccionamiento 2D • Direccionamiento 3D • Direccionamiento en memorias dinámicas: La técnica más empleada consiste en empaquetar la información en bloques, a los que se añade una cabecera que incluye el identificador del bloque. Estas cabeceras consumen partes de los puntos de direccionamiento, por lo que habrá una capacidad bruta de almacenamiento y una capacidad neta, que solo tenga en cuenta los datos. Por lo tanto, estas memorias se utilizan para acceder a bloques completos y no a posiciones individualizadas. Es el tipo de acceso por bloques. Dado que el soporte es continuo, es necesario disponer de una señal de sincronismo que permita diferenciar puntos de memoria discontinuos. Por ultimo se pueden establecer dos tipos de acceso: • Acceso secuencial, donde solo existe un trasductor fijo. El medio se desplaza hasta alcanzar la posición deseada. Un ejemplo es la cinta magnética. • Acceso directo, donde puede haber un trasductor móvil que se desplaza hasta alcanzar una determinada posición del soporte, o varios que se reparten distintas zonas del soporte. No obstante, el acceso dentro de cada zona es secuencial. Un ejemplo son los discos. • Memorias asociativas o CAM: La escritura se hace mediante direccionamiento cableado, pero la lectura es por contenido. Para ello, se suministra un dato y la memoria comprueba simultáneamente la concordancia de dicho dato con todos los contenidos almacenados, suministrando la dirección de coincidencia o un contenido asociado a ella. Organización de las memorias. Aunque hemos progresado desde la simple memoria de 1 bit de la figura 3−25 a la de 8 bits de la figura 3−27(b), no podemos seguir por este camino, debido a la falta de patas en las pastillas. Cada biestable requiere dos patas, D y Q, además de las de control compartidas por todos. Para construir memorias grandes se requiere una organización distinta. 4 Fig. 3−27. (b) Circuito integrado 74273 con biestables. Lo que se necesita es un diseño en que el numero de patas crezca en relación logarítmica con la capacidad de memoria, en lugar de hacerlo en forma lineal. Una organización de memorias muy extendida que cumple ese criterio es la de la figura 3−28. Este ejemplo ilustra una memoria de cuatro palabras de tres bits. Cada operación lee o escribe una palabra completa de 3 bits. Aunque la capacidad de esta memoria de 12 bits es algo mayor que la de nuestro registro de 8, necesita menos patas y, lo que es más importante, el diseño se generaliza fácilmente para memorias grandes. Aunque a primera vista la memoria de la figura 3−28 parece complicada, en realidad es bastante simple, debido a su estructura regular. Tiene ocho líneas de entrada y tres salida. 5 De las de entrada, tres son de dato: DE0, DE1 Y DE2; dos de dirección: DIR0, Y DIR1; y tres de control: CS para seleccionar la pastilla, RD para distinguir la lectura de la escritura y OE para permitir la salida. Las líneas de salida son para los datos: DS0, DS1, y DS2. En principio, podía ponerse esta memoria en un chip de 14 patas, incluyendo la alimentación y la tierra, frente a las 20 del registro de ocho biestables. Se necesita una lógica externa que ponga CS en alto para seleccionar la pastilla, así como para poner RD a alto (1 lógico) para leer, o abajo (0 lógico) para escribir. Las dos líneas de dirección deben ajustarse para que indiquen cuál de las cuatro palabras de tres bits ha de leerse o escribirse, pero en las de salida aparece la palabra seleccionada. En una escritura, en cambio, no se usan las líneas de datos de salida, pero se recoge el dato de las de entrada y se guarda en la posición de memoria seleccionada. Examinemos ahora de cerca la figura 3−28 para ver cómo funciona. Las cuatro compuertas AND de selección de palabra de la izquierda forman un decodificador. Los inversores de sus entradas se han ubicado de manera que se habilite (salida en alto) cada una de las compuertas con una dirección distinta. Cada compuerta alimenta una línea de selección de palabra, la de arriba para la palabra 0, la siguiente hacia abajo para la 1, etc. Cuando se seleccione la pastilla para escritura, la línea vertical etiquetada estará en alto, habilitando a una de las cuatro compuertas de escritura, según la línea de selección de palabra que esté en alto. La salida de la compuerta de escritura mueve todas las señales CK de la palabra seleccionada, cargando los datos de entrada en los flip−flops de la misma. Sólo se escribe si CS está en alto y RD en bajo, y sólo en la palabra seleccionada por DIR0 y DIR1; las restantes permanecen sin ser alteradas. La lectura es similar a la escritura. La decodificación de direcciones es idéntica. Pero ahora la líneaesté en bajo, por lo que se deshabilita todas las compuertas de escritura y no se modifica ningún biestable. En cambio, la línea de selección de palabra elegida habilita las compuertas AND conectadas a las salidas Q de la palabra seleccionada. Por tanto, una palabra pasa sus datos a las compuertas OR de cuatro entradas de la parte inferior de la figura, mientras que a las otras tres palabras les pasan ceros. En consecuencia, la salida de las compuertas OR es idéntica al valor guardado en la palabra seleccionada. Las tres palabras no seleccionadas no contribuyen a la salida. 6 7 Fig. 3−28. Diagrama lógico de una memoria de 4 x 3. Cada fila es una de las cuatro palabras de tres bits. Las operaciones de lectura y escritura siempre leen o escriben una palabra completa. Aunque podría haberse diseñado un circuito en que las salidas de las compuertas OR se llevaran directamente a las líneas de salida, a veces eso causa problemas. En particular, se ha señalado que las líneas de datos de entrada y de salida son diferentes, pero en las memorias reales son las mimas. Si se hubieran conectado las compuertas OR a las líneas de salida, la pastilla intentaría sacar datos, es decir, forzar cada línea a un valor especifico, incluso en escritura, interfiriendo en esa forma con los datos de entrada. Por esta razón, es deseable tener algún modo de conectar las compuertas OR con las líneas de datos de salida en las lecturas, pero desconectarlas por completo en las escrituras. Lo que necesitamos es un conmutador electrónico que pueda abrir o cerrar una conexión en unos pocos nanosegundos. Por fortuna tales conmutadores existen. La figura 3−29(a) muestra el símbolo de lo que se llama un buffer no inversor. Tiene una entrada de dato, una salida de dato, una salida de dato y una entrada de control. Cuando la entrada de control está en alto, el buffer actúa como un hilo eléctrico, como se ve en la figura 3−29(b). Cuando la entrada de control está a nivel bajo, actúa como un circuito abierto como se muestra en la figura 3−29(c) ; es como si alguien hubiera desconectado la salida de datos del resto del circuito con cortacables, la conexión puede restaurarse en pocos nanosegundos volviendo a poner la entrada de control a nivel alto. Fig. 3−29. (a) Buffer no inversor. (b) Efecto de (a) cuando el control está a nivel alto. (c) Efecto de (a) cuando el control está a nivel bajo. (d) Buffer inversor. La figura 3−29(d) muestra un buffer inversor, que actúa como un inversor normal cuando el control está en alto y desconecta la salida cuando esta en bajo. Ambos tipos de buffers son dispositivos triestado, porque pueden dar 0, 1 o nada (circuito abierto). Los buffers también amplifican las señales, por lo que pueden manejar muchas entradas a la vez. Por esta razón, se les usa en circuitos, aunque no se necesiten sus propiedades de conmutador. Volviendo al circuito de memoria, podemos ahora entender para que sirve los buffers no inversores de las líneas de salida. Cuando CS, RD y OE esté en alto, la señal de habilitación de salida también estará es alto, habilitando los buffers y poniendo una palabra en las líneas de salida. Cuando cualquiera de las señales CS, RD, o OE esté en bajo, las salidas de datos se desconectarán del resto del circuito. Propiedades de las memorias. 8 Lo mas interesante de la memoria de la figura 3−28 es que se generaliza con facilidad para tamaños mayores. Tal como está dibujada, la memoria es de 4 x 3, es decir, de 4 palabras de 3 bits cada una. Para extenderla a 4 x 8 solo tendríamos que añadir cinco columnas mas de cuatro biestables cada una, así como cinco líneas de entrada y cinco de salida. Para ir de 4 x 3 a 8 x 3 deberemos añadir cuatro filas más de tres biestables cada una, así como una línea de dirección adicional, DIR2. Con esta clase de estructura, el numero de palabras debería ser una potencia de dos, para que la eficiencia sea máxima; sin embargo, el numero de bits por la palabra puede ser cualquiera. Como la tecnología de circuitos integrados es muy adecuada es muy adecuada para hacer pastillas con una estructura interna repetitiva en dos dimensiones, las memorias son aplicaciones ideales de aquella. A medida que esta tecnología se perfecciona, aumenta el numero de bits que pueden meterse en una pastilla, cuadruplicándose aproximadamente cada 3 o 4 años. En los primeros años de la década de los setenta las pastillas tenían 1K bits; más tarde, tuvieron sucesivamente 4K, 16K, 64K, 256K, etc. En 1990 ya eran comunes las memorias con 4 millones de bits. No siempre las pastillas de más capacidad velocidad, consumo, precio y conveniencia de interconexión. Para un tamaño de memoria dado, existen varias formas de organizar las pastilla. En la figura 3−30 se aprecian dos posibles organizaciones para una pastilla de tamaño mediano (256K−bit): 32K x 8 y 256K x 1. En la primera, se necesitan 15 líneas para direccionar el byte seleccionado y ocho líneas para cargar y almacenar los datos. En la segunda, se necesitan 18 líneas para direccionar el bit seleccionado, pero sólo una línea para sacar los datos. En ambos casos se requiere de líneas para distinguir lecturas de escrituras y para la selección de las pastilla. La línea representa la habilitación de salida; cuando tiene un valor de 0, hay una salida presente, y cuando es 1, no la hay (v.g., la salida está desconectada del circuito). La línea representa la habilitación de escritura. Las barras colocadas sobre significan que la señal está activada en un estado de voltaje bajo (0 lógico) en lugar de alto (1 lógico). Esta convención se verá en detalle más adelante. Fig. 3−30. Dos modos de organizar una pastilla de memoria de 256K bits. Nótese que para construir una memoria con una palabra de memoria de 16 bits a partir de pastillas de 256K x 1, se requiere de 16 pastillas en paralelo obteniendo una capacidad total de por lo menos 512K bytes, mientras que usando pastillas de 32K x 8 sólo se requiere de dos pastillas en paralelo permite construir memorias tan pequeñas como de 64K bytes. 9 Las memorias que hemos estudiado hasta ahora pueden utilizarse para leer o escribir. Se suelen denominar memorias vivas o RAM (siglas inglesas para memoria de acceso aleatorio); este último nombre es bastante inadecuado puesto que todas las pastillas de memoria son accesibles en forma aleatoria, pero el termino ya se ha arraigado. Hay dos variedades de memorias RAM: las estáticas y las dinámicas. Las RAM estáticas se construyen a partir de circuitos similares a nuestro biestable D básico. Tienen la propiedad de retener su contenido tanto tiempo como estén conectadas a la fuente de alimentación, sean segundos, minutos, horas o aun días. Las RAM dinámicas, por el contrario, no usan circuitos biestables como lo estudiados, sino que están construidas como un conjunto de pequeños condensadores, que pueden estar cargados o descargados. Como la carga eléctrica tiende a fugarse, cada bit de la RAM dinámica debe refrescarse cada pocos milisegundos, para impedir la perdida de su información. Como el cuidado del refresco debe encomendarse a lógica externa, las RAM dinámicas son mas difíciles de interconectar que las estáticas, aunque en muchas aplicaciones esta desventaja está compensada por su mayor capacidad. Algunas memorias dinámicas tienen la lógica de refresco en la propia pastilla, dando así gran capacidad y facilidad de conexión a los circuitos. Estas pastillas se denominan casi estáticas. Las RAM no son los únicos tipos de pastillas de memoria. En muchas aplicaciones, como juguetes, electrodomésticos y automóviles, los programas y parte de los datos deben permanecer aun cuando se desconecte la alimentación. Además, una vez instalados, ni el programa ni esos datos van a cambiarse nunca. Estos requisitos llevaron al desarrollo de las memorias fijas o ROM (siglas inglesas para memoria de sólo lectura), que no pueden cambiarse de ninguna manera. Los datos se graban durante la fabricación de la ROM, que consiste esencialmente en la exposición a la luz de un material fotosensible a través de una máscara con la configuración deseada de bits. Después se disuelve la parte expuesta a la luz (o la no expuesta). La única manera de cambiar un programa en ROM es sustituir la pastilla por otra. Las ROM son mucho más baratas que las RAM cuando se piden en grande cantidades, para amortizar el precio de hacer la mascara. Sin embargo son inflexibles, ya que no pueden cambiarse después de su fabricación y el plazo de entrega desde que se encargan hasta que se reciben puede abarcar varias semanas. Para facilitar a las empresas el desarrollo de productos basados en ROM, se inventó otro tipo de memoria muerta denominado PROM (ROM programable). Esta pastilla es como un ROM, excepto en que puede programarse (una sola vez), reduciendo así el plazo en que pueden tenerse grabadas. El siguiente avance en esta línea fue la EPROM (PROM borrable), que no sólo puede programarse sino también borrarse. Cuando la ventana de cuarzo una EPROM se expone a la luz ultravioleta potente durante 15 minutos, todos sus bits se ponen a 1. Si se espera hacer muchos cambios en el ciclo de diseños, las EPROM son mucho más económicas que las PROM porque pueden reutilizarse. Aún mejores que las EPROM son las EEPROM (EPROM eléctricamente borrables), también llamadas EAPROM (ROM eléctricamente alterables), que pueden borrarse mediante impulsos eléctricos, sin necesidad de que las introduzcan en un receptáculo especial para exponerlas a luz ultravioleta. Las EEPROM difieren de las RAM en que el tiempo necesario para grabar o borrar un byte es miles de veces mayor, a pesar de que los tiempos de acceso en lectura de las ROM, PROM, EPROM, EEPROM y RAM son similares (al máximo unas centenas de nanosegundos). MEMORIA ROM Memorias de Solo Lectura (ROM). Una memoria de solo lectura (ROM), como su nombre lo implica, es una unidad de memoria que realiza solamente la operación de lectura; no tiene la capacidad de escribir. Esto implica que la información binaria almacenada en una ROM se realiza permanentemente durante la producción del hardware de la unidad y no 10 puede ser alterada escribiendo palabras diferentes en ella. Mientras que una RAM es un dispositivo de propósito general cuyos contenidos pueden alterarse durante el proceso de computo, un ROM está restringido a la lectura de palabras que son permanentemente almacenadas dentro de la unidad. Un ROM m por n es un arreglo de celdas binarias organizados en m palabras de n bits cada una. Como se muestra en el diagrama de bloques de la Figura 2−22, un ROM tiene k líneas de dirección para seleccionar una de 2k = m palabras de memorias, y n líneas de salida, una para cada uno de los bits de la palabra. Un ROM CI también puede tener una o mas líneas de habilitación para expandir un numero de paquetes CI en un ROM con capacidad mucho mas grande. El ROM no necesita una línea de control leer puesto que en un instante dado, las líneas de salida automáticamente proporcionan los 1's y 0's de los n bits de la palabra seleccionada por el valor de la dirección. Debido a que las salidas son una función solamente de las entradas presentes (las líneas de dirección) un ROM es clasificado con un circuito de combinación. En realidad, un ROM se construye internamente con decodificadores y un conjunto de compuertas OR. No hay necesidad de proporcionar condiciones de almacenamiento con el RAM, puesto que los valores de los bits en el ROM se mantienen fijos permanentemente. Considere el diagrama lógico de un ROM 4 por 3 que se indica en la Figura 2−23. La unidad contiene un decodificador de 2 por 4 para decodificar las dos líneas de dirección. Las compuertas OR proporcionan tres salidas. Si cada uno de los minterms de salida del decodificador es conectado a la entrada de cada una de las compuertas OR, las salidas del circuito estarán en 1 no importa cuál sea la palabra seleccionada por las líneas de dirección. Supongamos que deseamos que el ROM contenga las combinaciones de bits que se numeran en la tabla de verdad que acompaña al diagrama. La tabla de verdad especifica una combinación de bit de 010 para la palabra 0. Esta combinación de bit se obtiene rompiendo dos alambres (marcados con una cruz) entre la palabra 0 y las entradas que están mas a la izquierda de las compuertas OR. En otras palabras cuando la línea de dirección de entrada es 00, la salida D0 del decodificador es igual a 1 y todas las otras salidas del decodificador son iguales a 0. Solamente la compuerta OR asociada con la salida A2 recibe una entrada de 1 debido a que los otros dos alambres están rotos. Por consiguiente, las líneas de salida proporcionarán una salida A1A2A3 = 010 (suponiendo que un alambre abierto de la compuerta OR se comporta como una entrada 0). Similarmente, todos los otros alambres se retiran del diagrama, el diagrama lógico así obtenido implementará la tabla de verdad que se enumera para el ROM. Un ROM CI se fabrica primero con todas las salidas en 1 (o todas en 0, dependiendo del CI particular). El patrón particular de 1's y 0's se obtiene proporcionado una máscara en el ultimo paso de fabricación. Cada una de las celdas en un ROM incorpora un enlace (en la posición de la cruz en el diagrama de la Figura 2−23) que puede fusionarse durante el ultimo proceso de fabricación. Un enlace roto en una celda define un estado binario y un enlace no roto representa el otro estado. El procedimiento involucrado en la fabricación de ROMs requiere que el cliente llene la tabla de verdad que él desea que satisfaga el ROM. El fabricante entonces hace la máscara correspondiente para los enlaces para que se produzca los 1's y 0's de cada palabra deseada. Este procedimiento es denominado una programación al cliente o una programación de máscara. Es un procedimiento de hardware aunque se utilice aquí la palabra programación. Para pequeñas cantidades es mas conveniente utilizar el ROM programable, conocido como un PROM. Cuando se ordena, los PROMs contienen todos 0's (o todos 1's) en cada palabra. Cada una de las celdas de un PROM incorpora un enlace que puede fundirse por aplicación de un pulso de corriente elevada. Un enlace roto en una celda define un estado binario y uno que no está roto representada el otro estado. El procedimiento usualmente es irreversible y, una vez fundido, la salida para aquel bit es permanente. Esto permite al usuario programar la unidad en su propio laboratorio rompiendo los enlaces y los datos de salida. También se encuentran disponibles los PROMs borrables. Estos ROMs tienen un procedimiento especial para reestructurar los enlaces a su valor inicial (todos en 0`s o todos en 1's) aunque ellos hayan sido programados previamente. En cualquier caso, todos los procedimientos para programar o borrar ROMs son procedimientos del hardware. Las aplicaciones digitales que utilizan ROMs especifican un patrón de palabra fija. El aspecto de programación del ROM tiene que ver con los procedimientos para obtener el patrón fijo deseado. 11 Los ROMs encuentran un amplio rango de aplicación en el diseño de sistemas digitales. Básicamente, un ROM genera una relación entrada−salida especificada por una tabla de verdad. Como tal, puede implementar un circuito de combinación con k entradas y n salidas. Un ROM también puede utilizarse en el diseño de circuitos secuenciales. Esto es debido a que los circuitos secuenciales pueden subdividirse en un grupo de flip−flops y un ROM para el circuito de combinación. Otro tipo de circuito LSI que implementa un circuito de combinación complejo es el Arreglo lógico programable (PLA). Un PLA es similar a un ROM excepto en el concepto que no proporciona decodificación completa en las líneas de entrada. Así, en un PLA, el decodificador en la Figura 2−23 es remplazado por un grupo de compuertas AND cada una de las cuales se puede programar para producir un termino AND de las variables de entrada. Las compuertas AND y OR dentro del PLA se fabrican inicialmente en el ultimo paso del procesamiento y contienen una máscara para los enlaces de entrada a las compuertas AND y las salidas de las compuertas AND a las entradas de las compuertas OR. Los ROMs son ampliamente utilizados para convertir un código binario a otro, para tablas que se necesitan en funciones matemáticas, para la exhibición de caracteres, y muchas otras aplicaciones que requieren un gran numero de entradas y salidas. También se emplean en el diseño de unidades de control para computadoras digitales. En este aspecto se usan para almacenar información codificada que representa la secuencia de variables de control internas necesarias para habilitar las diversas operaciones en el computador. Una unidad de control que utiliza un ROM para almacenar información de control binario es denominada una unidad de control microprogramada. ROM, siglas para la memoria inalterable, memoria de computadora en la cual se han grabado de antemano los datos. Una vez que los datos se hayan escrito sobre un chip ROM, no pueden ser quitados y pueden ser leídos solamente. Distinto de la memoria principal (RAM), la ROM conserva su contenido incluso cuando el ordenador se apaga. ROM se refiere como siendo permanente, mientras que la RAM es volátil. La mayoría de los ordenadores personales contienen una cantidad pequeña de ROM que salve programas críticos tales como el programa que inicia el ordenador. Además, las ROM se utilizan extensivamente en calculadoras y dispositivos periféricos tales como impresoras láser, cuyas fuentes se salvan a menudo en las ROM. Una variación de una ROM es un PROM (memoria inalterable programable). PROM son manufacturados como chips en blanco en los cuales los datos pueden ser escritos con dispositivo llamado programador de PROM. Memorias de Acceso Aleatorio (RAM). Una memora es una colección de registros de almacenamiento junto con los circuitos asociados necesarios para transferir información dentro y fuera de los registros. A los registros de memoria se puede tener acceso para transferencia de información como sea requerido y de aquí el nombre memoria de acceso aleatorio, abreviada RAM. Una unidad de memoria almacena información binaria en grupos de bits denominados palabras. Cada una de las palabras es almacenada en un registro de la memoria. Una palabra en una memoria es una entidad de n bits que se mueve dentro y fuera de la unidad de memoria. A una palabra de ocho bits algunas veces se le denomina un byte. Una palabra de una memoria es un grupo de 0's y 1's y puede representar un numero, un código de instrucción, caracteres alfanuméricos, o cualquier otra información codificada en binario. La comunicación entre la unidad de memoria y su ambiente se lleva a cabo a través de líneas de control, líneas 12 de selección de dirección, y líneas de salida y entrada de datos. Las señales de control especifican la dirección de la transferencia requerida, esto es, si una palabra debe almacenarse en un registro de la memoria o si una palabra previamente almacenada debe ser trasferida fuera del registro de la memoria. Las líneas de dirección especifican la palabra particular elegida de las cientos o miles disponibles. Las líneas de entrada proporcionan la información que se debe almacenar en la memoria y las líneas de salida suministran la información que sale de la memoria. Un diagrama de bloque de una unidad de memoria se muestra en la Figura 2−18. Una unidad de memoria se especifica por el numero de palabras que contiene y el numero de bits en cada una de las palabras. Las líneas de selección de dirección seleccionan una palabra particular de la memoria de las m palabras disponibles. A cada palabra en una memoria se le asigna un numero de identificación, denominado una dirección, arrancando de 0 y continuando con 1, 2, 3, y hasta m − 1. La selección binaria en las líneas de selección. Un decodificador dentro de la unidad de memoria acepta esta dirección y abre las rutas necesarias para seleccionar la palabra especifica. Así, k bits de dirección puede seleccionar una de 2k = m palabras. Las memorias de computador están en el rango de 1024 palabras, requiriendo una dirección de 10 bits, a 1,048,576 = 220 palabras, que requieren 20 bits de dirección. Es costumbre referirse al numero de palabras en la unidad de memoria con la unidad K. K se refiere a 1024 = 210 palabras: así 1 K = 1024 palabras, 4 K = 4096 palabras, y 64 K = 216 palabras. Las dos señales de control se denominan leer y escribir. Una señal escribir especifica una operación de transferencia de entrada; una señal leer especifica una operación de transferencia de salida. Al aceptar una de estas señales de control, los circuitos de control interno dentro de la unidad de memoria proporcionan la función deseada. Cuando la unidad de memoria recibe una señal de control escribir, el control interno trasfiere los n bits de datos de entrada dentro de la palabra especificada por las líneas de dirección. Con un señal de control leer, la palabra seleccionada por las líneas de dirección aparece en las n líneas de datos de salida. RAM CI. Las memorias de circuitos integrados algunas veces tienen una sola línea para el control leer / escribir. Un estado binario, digamos 1, especifica una operación leer y el toro estado binario especifica una operación escribir. Además, se puede incluir una o mas líneas de habilitación en cada uno de los paquetes del CI para proporcionar medios para expandir varios paquetes en una unidad de memoria con un gran numero de palabras. La construcción interna de una memoria de acceso aleatorio de m palabras con n bits por palabra consta de m x n celdas de almacenamiento binario y la lógica necesaria para seleccionar una palabra para escribir o leer. La celda de almacenamiento binario es el bloque de construcción básico de una unidad de memoria. El diagrama lógico de una celda binaria que almacena un bit de información se muestra en la Figura 2−19. aunque la celda se muestra que incluye cinco compuertas y un flip−flop, internamente es construida con dos flip−flop de transistores que tienen entradas múltiples. La celda binaria de una unidad de memoria debe ser muy pequeña para ser capaz de empacar tantas celdas como sea posible en el área del semiconductor disponible en la pastilla. La celda binaria se muestra que tiene tres líneas de entrada y una línea de salida. El propósito de la entrada select es seleccionar una celda de las muchas disponibles. Con la línea select en 1, un 1 en el terminal leer / escribir conforma una ruta de salida del flip−flop al terminal de salida. Con el terminal leer / escribir en 0, el bit en la línea de entrada se trasfiere al flip−flop. Tanto la entrada como la salida son deshabilitadas cuando la línea select es 0. note que el flip−flop opera sin pulso de reloj y que su propósito es almacenar el bit de información en la celda binaria. La configuración de una RAM de 4 por 3 se muestra en la Figura 2−20. contiene cuatro palabras de tres bits una para un total de 12 celdas binarias de almacenamiento. Cada caja pequeña rotulada BC en el diagrama contiene el circuito de una celda binaria. Las cuatro líneas que se ven en cada caja BC designan los tres terminales de entrada y un terminal de salida como se especificó en el diagrama de la Figura 2−19. 13 Las dos líneas de dirección van a un decodificador 2 por 4 con una entrada de habilitación. Cuando la habilitación de memoria es 0, todas las salidas del decodificador son 0 y ninguna de las palabras de la memoria se seleccionan. Con la entrada habilitada de memoria en 1, una de las cuatro palabras es seleccionada, dependiendo de la combinación del bit de las dos líneas de dirección. Ahora, con el control leer / escribir en 1, los bits de la palabra seleccionada van a tres compuertas OR y a los terminales de salida. Las celdas binarias no seleccionadas producen 0's en las entradas del OR y no tienen efecto en las salidas. Con el control leer / escribir en 0, la información disponible en las líneas de entrada se trasfiere a los flip−flops de la palabra seleccionada. Las celdas binarias no seleccionadas en las otras palabras son deshabilitadas por la línea de dirección de tal manera que los valores previos permanecen inmodificados. Así, con la habilitación de la memoria en 1, el control leer / escribir inicia las operaciones leer y escribir para la unidad de memoria. Una operación de inhibición se obtiene manteniendo la habilitación de memoria en 0. Esta condición deja los contenidos de todas las palabras en la memoria como eran, independiente del valor del control leer / escribir. Los RAMs CI algunas veces emplean celdas binarias cuyas salidas pueden conectarse para formar una función OR alambrada o un AND alambrado. Otros RAMs CI proporcionan salidas tri−estado. Estas salidas son convenientes cuando se tienen que conectar dos o mas CI para formar una unidad de memoria con un numero mayor de palabras puesto que ello elimina la necesidad de compuertas externas OR que de otra manera serian necesarias. Memoria de núcleo magnético. Las memorias CI retienen la información binaria cuando una palabra se lee de la memoria. Este tipo de memoria se dice que tiene una propiedad de lectura no destructiva debido a que el contenido de la palabra en la memoria no es destruido durante el proceso de lectura. Otra componente comúnmente utilizada como celda de almacenamiento binario en las unidades de memoria es el núcleo magnético. Un núcleo magnético es un toroide muy pequeño hecho de material ferromagnético. La cantidad física que hace que el núcleo magnético sea adecuado para almacenamiento binario es su propiedad magnética. Una dirección de magnetización se emplea para representar un 0 y la otra para representar un 1. La lectura de salida de la información binaria almacenada en un núcleo magnético requiere que su dirección de magnetización sea forzada al estado 0. Por consiguiente, una memoria de núcleo magnético tiene una propiedad de lectura destructiva; él pierde la información previamente almacenada después del proceso de lectura. Debido a la propiedad de lectura destructiva, una memoria de núcleo magnético debe proporcionar funciones de control adicional para restaurar el contenido original de la palabra que se acabó de leer. Una señal de control leer aplicada a la memoria de núcleo magnético trasfiere el contenido de la palabra direccionada a un registro externo y, al mismo tiempo, el registro de la memoria de núcleo magnético entonces proporciona señales adecuadas para realizar la restauración de la palabra en el registro de memoria. Esto se hace rescribiendo la información del registro externo en la misma palabra de memoria. Similarmente, para escribir nueva información en una palabra en una memoria de núcleo magnético, los bits de la palabra seleccionada primero se aclaran a 0. La información binaria de las líneas de entrada se trasfiere entonces a la palabra seleccionada colocando todos los bits que necesitan 1 y no cambiando los bits que necesitan 0. De nuevo, esta doble operación se lleva a cado automáticamente por medio del control de la unidad de memoria. Operaciones de memoria. La secuencia de control interno de una unidad de memoria es un función de sus componentes y del tipo de líneas de control proporcionados con la unidad. Además, la información de dirección y entrada puede provenir de diferentes fuentes y la información de salida puede ir a muchos destinos. La operación de una unidad de memoria se simplifica si asociamos con ella dos registros externos y suponemos la disponibilidad de dos señales de control como se muestra en la Figura 2−21. Las líneas de dirección de la unidad de memoria están permanentemente conectadas a las salidas de un registro externo denominado el Registro de Dirección de Memoria, abreviado MAR. La información binaria es trasferida entre palabras de memoria y el ambiente externo a través de un registro externo común denominado el Registro Separador de Memoria, abreviado MBR 14 (otros nombres son: registro de información, registro de almacenamiento y registro de datos.) La información de entrada es siempre trasferida al MBR, y la información de salida siempre se toma del MBR. Cuando la memoria recibe un comando escribir, el control interno interpreta el contenido del registro separador como los bits de información de la palabra almacenada. Con un comando leer el control interno trasfiere la palabra de la memoria en el registro separador. En cada caso, los contenidos del registro de dirección especifican la palabra particular en la memoria referenciada por la escritura o por la lectura. Si una memoria de núcleo magnético se utiliza, su secuencia de control interno automáticamente restaura la palabra en la memoria después de una operación de lectura. La secuencia de operaciones necesarias para comunicarse con la unidad de memoria con el fin de transferir una palabra fuera al ambiente externo son las siguientes: • Trasferir los bits de dirección de la palabra requerida en el MAR. • Activar el control de entrada leer. La información binaria almacenada en la palabra de la memoria especifica por MAR se encontrara entonces en MBR. El contenido de la palabra leída de la memoria no será destruido. La secuencia de operaciones externas que se necesitan para almacenar una palabra en la memoria son: • Trasferir los bits de dirección de la palabra requerida al MAR. • Trasferir los bits de datos de la palabra al MBR. • Activar la señal escribir. La información del MBR se almacena entonces en la palabra de memoria especificada por MAR. Los contenidos previos de la palabra son, obviamente, destruidos. Características especiales. El tiempo de acceso se define como la diferencia de tiempo entre el tiempo que una unidad de memoria recibe una señal leer y el instante en que la información leída de la memoria está disponible en las salidas. En una memoria de lectura destructiva, como la de núcleo magnético, la información sacada es físicamente destruida por el proceso de lectura. Sin embargo, es automáticamente restaurada; pero esto requiere un tiempo adicional. La suma de tiempo de acceso y el tiempo de restauración es denominada el tiempo de ciclo. En una memoria de lectura no destructiva, el tiempo de ciclo es igual al tiempo de acceso porque no hay tiempo de restauración. Los tiempos de ciclo típicos de unidades de memoria están en el rango de 100 ns hasta 1 s. El modo de acceso de una memoria se determina por el tipo de componentes que se utilizan. En una memoria de acceso aleatorio, los registros de la memoria pueden tomarse como si estuvieran en espacios separados, con cada uno de los registros ocupando un localización espacial particular como en las memorias RAM CI o las memorias de núcleo magnético. En una memoria de acceso secuencial, la información almacenada en algún medio no es accesible inmediatamente pero se encuentra disponible solamente después de cierto intervalo de tiempo. Una memoria de registro de desplazamiento es de este tipo. Los registros de desplazamiento se utilizan como memorias series y se encuentran disponibles en paquetes MOS / LSI. Los contenidos de la memoria son recirculados vía un circuito de realimentación de la salida a la entrada. Una memoria de acceso secuencial de m palabras por n bits se obtiene con n registros de desplazamiento en sincronización, en que cada uno de los registros de desplazamiento representa un bit de la palabra. La longitud de registro de desplazamiento determina el numero de palabras. La recirculación de los registros de desplazamiento utilizados como memorias deriva su dirección de un contador auxiliar que determina la palabra que debe emerger de los terminales de salida. Cada una de las palabras pasa a los terminales de salida una por una y la información es leída cuando la palabra requerida esté disponible en los terminales de salida. 15 En una memoria de acceso aleatorio, el tiempo de acceso es siempre el mismo independientemente de la localización particular de la palabra en el espacio. En una memoria secuencial, el tiempo de acceso depende de la posición de la palabra en el instante de ser requerida. Si la palabra que está precisamente saliendo del almacenamiento en el instante en que es requerida, el tiempo de acceso es el tiempo necesario para leerla. Si la palabra sucede que está en una posición diferente, el tiempo de acceso también incluye el tiempo requerido para que todas las otras palabras se muevan hacia los terminales de salida. Así, el tiempo de acceso en una memoria secuencial es variable. Las unidades de memoria cuyas componentes pierden la información almacenada con el tiempo o cuando la energía se apaga se dice que son volátiles. Las memorias CI son volátiles puesto que sus celdas binarias requieren potencia externa para mantener la información almacenada. En contraste, una unidad de memoria no−volátil tal como la de núcleo magnético o disco magnético retiene su información almacenada después de que se retira la energía. Esto es debido a que la información almacenada en componentes magnéticas es manifestada por la dirección de magnetización, la cual es retenida cuando se retira la energía. Una propiedad no−volátil se desea en computadores digitales debido a que mucho programas útiles se dejan permanentemente en la unidad de memoria. Cuando la energía se apaga y vuelve de nuevo, los programas previamente almacenados y otra información no se pierden pero continúan residiendo en la memoria. Los computadores con memorias volátiles pueden resolver el problema de la falla de energía utilizando baterías de respaldo o fuentes de potencia especial que continúen entregando potencia por algún tiempo después de que ocurra la interrupción de potencia. MEMORIA RAM Memoria de la computadora, denominada Memoria de Acceso Aleatorio, es un área de almacenamiento a corto plazo para cualquier tipo de dato que la computadora está usando. RAM a menudo se confunde con el almacenamiento. Para una aclaración, comparemos la computadora con una oficina. El gabinete de archivos representa el almacenamiento (unidad de disco duro) y el escritorio representa la RAM. Los archivos a usar se recuperan del almacenamiento. Mientras los archivos están en uso se guardan en la RAM, un área de trabajo de fácil acceso. Cuando los archivos dejan de usarse se regresan al sector de almacenamiento o se eliminan. RAM, son las siglas para la memoria de acceso al azar, un tipo de memoria de computadora que se puede alcanzar aleatoriamente; es decir, cualquier byte de memoria puede ser alcanzado sin el tocar los bytes precedentes. La RAM es el tipo más común de memoria encontrado en ordenadores y otros dispositivos, tales como impresoras. Hay dos tipos básicos de RAM: • RAM estática (SRAM) • RAM dinámica (DRAM) Estos 2 tipos difieren en la tecnología que utilizan para almacenar datos, RAM dinámica que es el tipo más común. La RAM dinámica necesita ser restaurada millares de veces por segundo. La RAM estática no necesita ser restaurada, lo que la hace más rápida; pero es también más costosa que la DRAM. Ambos tipos de RAM son volátiles, significando que pierden su contenido cuando se interrumpe el suministro de poder. En uso común, el término RAM es sinónimo de memoria principal, la memoria disponible para los programas. Por ejemplo, un ordenador con la RAM de los 8M tiene aproximadamente 8 millones de bytes de memoria 16 que los programas puedan utilizar. En contraste, la ROM (memoria inalterable) se refiere a la memoria especial usada para salvar los programas que inician el ordenador y realizan diagnóstico. La mayoría de los ordenadores personales tienen una cantidad pequeña de ROM (algunos tantos miles de bytes). De hecho, ambos tipos de memoria (ROM y RAM) permiten el acceso al azar. Para ser exacto, por lo tanto, RAM se debe referir como RAM de lectura/escritura y ROM como RAM inalterable. RAM DINÁMICA Un tipo de memoria física usado en la mayoría de los ordenadores personales. El término dinámico indica que la memoria debe ser restaurado constantemente (reenergizada) o perderá su contenido. La RAM (memoria de acceso aleatorio) se refiere a veces como DRAM para distinguirla de la RAM estática (SRAM). La RAM estática es más rápida y menos volátil que la RAM dinámica, pero requiere más potencia y es más costosa. RAM ESTÁTICA Abreviatura para la memoria de acceso al azar estática. SRAM es un tipo de memoria que es más rápida y más confiable que la DRAM más común (RAM dinámica). El término se deriva del hecho de que no necesitan ser restaurados como RAM dinámica. Mientras que DRAM utiliza tiempos de acceso de cerca de 60 nanosegundos, SRAM puede dar los tiempos de acceso de hasta sólo 10 nanosegundos. Además, su duración de ciclo es mucho más corta que la de la DRAM porque no necesita detenerse brevemente entre los accesos. Desafortunadamente, es también mucho más costoso producir que DRAM. Debido a su alto costo, SRAM se utiliza a menudo solamente como memoria caché. TIPOS Y MODELOS DE MEMORIAS RAM Dentro de los que genéricamente conocemos como memorias, tenemos que destacar que dependiendo del año de su fabricación pueden ser de 72 o de 128 contactos. Las de 72 contactos se utilizaban como norma estándar en los antiguos 286−386−486 e incluso en algunos Pentium pequeños, pero se sustituyeron por otro tipo de memorias que eran las de 128 contactos cuya velocidad superaba con creces a sus antecesoras. A las memorias de 72 contactos se las denomina SIMM (Single In−Line Memory Module). A las memorias de 128 contactos se las denomina DIMM (Dual In−Line Memory Module). Otro tipo de memorias que existían eran las de 72 contactos pero en un formato mucho más comprimido para poder ocupar menos espacio en los ordenadores portátiles. Este tipo de memorias son las denominada SODIMM ( Amall Outline Dimm). En lo referente al tipo de modelos que existen hoy día, hay que decir que cada vez que salen al mercado un nuevo tipo de memoria con unas prestaciones mayores a las de su antecesora, recibe un nombre distinto que hace referencia a las nuevas características de la nueva memoria. Podemos destacar las siguientes memorias. • La memoria EDORAM. Es un tipo de memoria que acorta el tiempo de acceso entre la memoria y la CPU. Gracias a esta memoria, un equipo que este preparado puede llegar a ser hasta un 15 % más rápido que en un equipo normal. • La SDRAM. También llamada DRAM Sincrona. Es una memoria que utiliza un reloj para sincronizar las operaciones de entrada y de salida en el chip. Supera y releva a la memoria EDORAM. 17 Como dato informativo, diremos que la memoria cache, que ya detallaremos mas adelante, supera en velocidad a EDORAM, en 50 nanosegundos. CACHE 10ns EDORAM 60 ns • CARACTERISTICAS DE LAS MEMORIAS Además de la duración de la información y el modo de direccionamiento, las memorias se caracterizan por el tamaño, velocidad y número de puertas. 1.1 Tamaño o capacidad. La capacidad mide el numero de datos que es capaz de almacenar una memoria. En las memorias de direccionamiento cableado existe una relación directa entre los bits necesarios para hacer el direccionamiento y la capacidad. Si la memoria tiene H palabras, se requieren m bits de dirección tal que 2m > o igual a H. En el caso de las memorias dinámicas, además de los datos debe almacenarse una cabecera y una señal de reloj, por lo que hay que distinguir entre capacidad útil y capacidad bruta. 1.2 Velocidad. Se puede definir la velocidad como el tiempo que se tarda en realizar una operación de lectura o escritura. Cabe diferenciar entre memorias estáticas y dinámicas. • Memorias estáticas. Dado que todos los puntos de memoria están cableados de forma equivalente, los tiempos son independientes de la dirección. El tiempo de acceso o lectura es el tiempo que tarda la memoria en suministrar una palabra, desde el momento en que se le presentan su dirección y la señal de lectura. Ahora bien, si se hacen n lecturas consecutivas, el tiempo total de lectura no será igual al de una sola lectura, ya que suele exigir un tiempo de regeneración de los decodificadores, trasductores y puntos de memoria. El tiempo de escritura es el tiempo que tarda la memoria en guardar la infamación desde el momento en que se suministra la información, la dirección y la señal de escritura. En la actualidad las memorias de semiconductores tienen un ciclo RMW (Rea−Midify−Write), consistente en hacer una operación de lectura seguido de otra de escritura sobre la misma dirección de memoria. • Memorias dinámicas. Para analizar la velocidad de las memorias dinámicas hay que considerar el tiempo que se tarda en hacer coincidir el trasductor con los datos, así como la cadencia a la que se leen o escriben datos consecutivos. El primer tiempo es el tiempo de acceso. Este tiempo se compone del tiempo de búsqueda. Tiempo que tarde el trasductor en alcanzar la posición deseada, mas el tiempo de latencia, esto es el tiempo que tarda la zona buscada del soporte en situarse frente al trasductor. Una vez accedida la zona deseada, pueden leerse o escribirse a alta velocidad una serie de palabras 18 consecutivas. Es la velocidad de transferencia. 1.3 Interconexión. Memorias multipuerta. Dentro de las memorias internas también existen memorias, llamadas multipuerta, en las que se dota a estas de varias vías de comunicación simultaneas. La memoria multipuerta se basa en los siguientes principios: • Está dividida en módulos, que pueden operar de forma independiente y simultanea. • Tienen un mecanismo que permite que una puerta este conectada a cualquiera sus módulos. • Tiene un sistema que detecta y soluciona problemas de colisión, caso que ocurre cuando 2 o más puertas intentan acceder a un mismo módulo. • MEMORIAS DE SEMICONDUCTORES Estas memorias son de direccionamiento cableado y, por tanto, estáticas y de acceso directo (RAM). Estas memorias se caracterizan por: • El bus de direcciones puede ser completo con m bits para direccionar 2m palabras, o puede estar multiplexado, transmtiendose primero m/2 bits y luego el resto. • El bus de datos es de tipo triestado, por lo que se pueden conectar directamente los buses de datos de varias pastillas. • Las señales de control, que suelen ser de activación de pastilla, de lectura y escritura, etc... • El ancho de palabra. • La capacidad. Seguidamente se van a analizar las memorias de semiconductores más habituales. • RAM estáticas SRAM. Mantienen su estado siempre que no se interrumpa la alimentación. Se usan en memorias pequeñas, dado que son mas caras, ocupan mas espacio y consumen mas que las dinámicas, pero son más rápidas y sencillas de usar. Son de lectura y escritura. • RAM dinámicas DRAM. En estas memorias el estado se almacena por medio de un condensador que tiende a descargarse, por lo que ha que refrescarse para que no pierdan la información. Se usan en memorias de tamaño mediano o grande ya que son más económicas que las estáticas. Son de lectura y escritura. • ROM Y PROM Solo permiten la operación de lectura. La información se graba en el momento de fabricación (ROM = Read Only Memory) o en un proceso posterior irreversible, (PROM = Programable Rom). Su uso consiste en almacenar el programa de arranque de las computadoras. Son por ello memorias permanentes. • EPROM y EEPROM. Son memorias permanentes de solo lectura, pero que se pueden borrar mediante procesos especiales. La ventaja de las EEPROM es que el borrado es selectivo, es decir, se borra a nivel de palabra, mientras que la EPROM se borra en su totalidad. • VRAM 19 Es una memoria RAM dinámica diseñada para memorias de refresco de terminales gráficos. • MEMORIA INTERNA La memoria interna esta constituida por tres grupos: • Los registros, incluidos en la unidad aritmética. • La memoria principal, que es la memoria donde residen los programas y sus datos. • La memoria caché, que es una memoria auxiliar que se emplea para acelerar los accesos a la memoria principal, pero que es transparente al usuario. • Mapa de memoria. Se llama mapa de memoria a todo el espacio direccionable por el computador. Así, para m bits de dirección, se dice que el mapa de memoria es de 2m. Por otro lado, las m líneas de dirección forman el bus de direcciones. • MEMRIA VIRTUAL Un computador emplea memoria virtual cuando las direcciones que generan sus programas se refieren a un espacio mayor que el espacio realmente disponible en memoria principal. Así, hay que diferenciar entre mapa de direcciones lógicas o virtual y el mapa de direcciones físicas o reales. El espacio virtual emplea como soporte un dispositivo de almacenamiento externo, como puede ser un disco. La realización de un computador con memoria virtual exige resolver dos problemas: • La traducción de direcciones. Los programas y datos residen en memoria principal, por lo que deben accederse mediante las direcciones físicas. Sin embargo, las direcciones que generan los programas se refieren a espacio virtual, por lo que debe establecerse un mecanismo de traducción que convierta direcciones virtuales a físicas. • La asignación de memoria física. Puesto que el espacio físico es mucho menor que el virtual no podrá residir en memoria mas que una parte del espacio virtual. Ello hace que se intente acceder a posiciones que no residen en memoria física. Por tanto, es necesario establecer un mecanismo que, de forma dinámica, asignen el espacio físico, de tal forma que los procesos tengan en todo momento en la memoria principal aquellas partes que requieran para su ejecución. Cuando un proceso genera un fallo de pagina, la política de reemplazo establece la forma en que se selecciona la pagina que hay que devolver al soporte del espacio virtual para dejar un hueco y poder traer la pagina que origino el hueco, necesaria para que continúe el proceso. Esta política de reemplazo es fundamental para el funcionamiento de la memoria virtual, puesto que afecta fuertemente a la tasa de fallos. Así, se deberá intentar eliminar aquellas paginas con menor probabilidad de uso, por ejemplo, la que lleve mas tiempo sin ser usada. La viabilidad del uso de la memoria virtual reside en la proximidad de las referencias a memoria. Existen dos tipos de proximidad. • Proximidad espacial • Proximidad temporal. • MEMORIA CACHE 20 La memoria cache es una memoria auxiliar de alta velocidad que se añade a la memoria principal para acelerar su funcionamiento. Suele ser del orden de 5 a 10 veces más rápida que la memoria principal y tiene un tamaño que oscila entre 8 y 64 Koctetos. El funcionamiento de la memoria cache con respecto a la principal es similar al de la memoria principal respecto a la virtual. Ambas memorias, caché y principal se dividen en bloques y líneas de unos pocos octetos, que hacen la función de las paginas. La propia cache se encarga de realizar la tradición de los identificadores de bloque, generando en su caso la señal de fallo. La secuencia de funcionamiento es la siguiente: • La CPU genera una dirección, que es enviada a la memoria cache. • La memoria cache realiza la tradición a dirección de cache y comprueba si tiene la referencia. En caso afirmativo realiza el acceso, con lo que el proceso finaliza. • En caso de fallo se accede directamente la palabra deseada de la memoria principal, y se procede a seleccionar un bloque para ser sustituido. • Cuando el bloque a sustituir no ha sufrido modificación, el proceso se limita a leer de la memoria principal el nuevo bloque y a almacenarlo en la posición del bloque a sustituir. Si el bloque fue modificado habrá que leerlo previamente de la cache y almacenarlo en la memoria principal. Memoria EEPROM Esta memoria EEPROM Electrical Erasable Programmable Read Only Memory, algo así como memoria de solo lectura programable y borrable de forma eléctrica, lo que significa que una vez que se le quita la corriente eléctrica mantiene la información de forma indefinida y además puede reprogramarse borrando su contenido de forma eléctrica. Esto es una ventaja frente a las memorias EPROM que se deben borrar con luz ultravioleta Descripción funcional −Es una memoria de 16 Kbits ( 16384 bits ) organizada en 8 bancos de 256 bytes cada uno. − Soporta protocolo de transmisión de datos en bus de dos líneas. − El bus se controla mediante un master que se encarga de generar el reloj ( SCL ), el control de acceso al bus y además genera las condiciones de START y STOP mientras el 24LC16B actua como slave. La siguiente figura muestra una configuración típica de esta memoria : 21 Características del bus • Sólo puede iniciarse transferencia de datos cuando el bus está libre. • Durante la transferencia de datos estos deben permanecer estables mientras la línea de reloj esté a nivel alto. Si se producen cambio se interpretan como un Start o un Stop. Operaciones de escritura La escritura comienza por un START, direccionamiento del dispositivo, dirección del byte y finalmente el byte a escribir, después de cada elemento se añade un ACK por parte de la memoria como se indica en la figura. Escritura secuencial Si lo que se desea es escribir un grupo de 16 bytes sólo es necesario enviar la dirección del primero de ellos y a continuación el resto, la memoria posee un contador interno que determina la dirección actual, este se irá incrementando para cada byte. La diferencia respecto a la escritura de un único byte estriba en el hecho del señalizador del STOP, si este no aparece es que se debe escribir sucesivos bytes. La figura muestra el caso. Una escritura incluye un borrado del contenido de la dirección por lo que esta es mucho más lenta que una lectura. 22 Operaciones de lectura Las operaciones de lectura son 3, la lectura de la dirección actual ( almacenada por el contador de dirección ), lectura arbitraria en cualquier posición de la memoria y finalmente la lectura secuencial. Lectura actual Toma la posición actual de la memoria, como puede verse en la figura, después del dato no hay un ACK, ya que este va dirigido al master. Lectura arbitraria En esta lectura se indica la posición a leer la información, hay que destacar que primero se ha de enviar la dirección y despues se recibe el dato, por eso existe un ACK después de la dirección. Lectura secuencial La lectura secuencial toma la dirección actual y va extrayendo los datos uno detrás del otro, hay que tener en cuenta que se lee la página actual y esta no se cambia cuando se llega al final por lo que la lectura como máximo es de 16 23 bytes. LA MEMORIA EPROM 2716 Descripción general La EPROM 2716 contiene características borrables y es eléctricamente reprogramable, es de alta velocidad y proporciona acceso a 16 Kbits de información, esta diseñada para aplicaciones en donde son importantes los cambios rápidos en la tensión. La EPROM 2716 esta empacada en un circuito integrado de 24 terminales, usa una placa transparente en su dorso, lo cual nos permite exponer el chip a rayos ultravioleta ópticos, que se utilizan para borrar la memoria, se le puede depositar una nueva información aun después de estar borrada siguiendo los procedimientos de programación adecuados, esta EPROM 2716 esta constituida con tecnología de alta densidad con compuertas CMOS de canal N. Ventajas ð Tiempo de acceso menor que 250 nseg. ð Bajo consumo de potencia ð Disipación en estado activo: 525 mW máx. ð Disipación en estado inactivo: 132 mW máx. ð Fuente de alimentación de +5 Volts ð Rango de temperatura de −40 hasta +85 grados centígrados ð Características estáticas (no requiere refrescamiento por medio del reloj) ð Entradas y salidas compatibles con la tecnología TTL ð Capacidad de colocarse en tercer estado. OPERACIÓN DEL DISPOSITIVO Existen 5 modos de operación, se debe hacer notar que todas las entradas son TTL independientemente del modo de operación, la fuente de alimentación requiere de +5.0 Volts en la terminal Vcc, la terminal Vpp esta en alta tensión +25 Volts durante 3 modos y en +5 Volts en los otros dos modos de operación. DESCRIPCIÓN DE LAS TERMINALES 24 ð A0−A10: Lineas de direcciones ð D0−D7: Salida de datos ð (CE)' Habilitador de la pastilla ð (OE)' Habilitador de salidas ð PGM Condición de programación ð Vcc Voltaje de alimentación +5.0 Volts ð Vss Terminal de tierra 0.0 Volts ð Vpp Voltaje de programación ð NC No conexión OPERACIÓN DE LECTURA Para leer la memoria se deben hacer las conexiones de las terminales que a continuación se especifican, la terminal Vpp se conecta a Vcc para inhibir con esto la programación, las entradas (OE)' y (CE)' se colocan en tierra y con estas simples conexiones se puede leer la memoria, los datos estarán sobre las terminales D1 − D7, la información se puede visualizar con LED'S quienes indican el dato direccionado por las terminales A0 − A10, cuya capacidad es de (2K X 8), 2048 localidades de 8 bits cada una. MODO DE PROGRAMACIÓN Para programar la memoria se requieren las siguientes conexiones: En la terminal 18 se debe depositar un pulso de Tw = 45 mseg aproximadamente, dicho pulso deberá estar dado por un monoestable. La terminal 20 que es el habilitador de salidas se conecta a la polarización de +5.0 Volts (la alimentación). La terminal 21, voltaje de programación se conecta a un voltaje fijo de +25.0 Volts, la memoria normalmente cuando no esta grabada contiene "unos", por lo tanto en la operación de grabación se procede a depositar ceros. PRECAUCIONES Excediendo de los 25 Volts en la terminal Vpp (pin 21) se dañara la EPROM 2716 y después todos los bits quedaran en el estado uno lógico. La información debe ser introducida usando el modo de programación, depositando solamente ceros lógicos en la localidad seleccionada y con la combinación deseada, aunque ambos unos y ceros pueden ser presentados como datos de entrada en la palabra de información a grabar. La única manera de cambiar los ceros por los unos es borrando totalmente la memoria EPROM 2716 a través de una intensa luz ultravioleta. La EPROM 2716 esta en la modalidad de programación cuando la fuente de alimentación de Vpp esta en +25 Volts y (OE)' en estado lógico alto. Se requiere un capacitor de 0.1 uF dispuesto entre +Vcc y GND para suprimir los estados transitorios de tensión que puedan dañar al dispositivo EPROM 2716. 25 La información debe se programada en 8 bits en paralelo dispuestos en las terminales de salida del chip, los niveles deben ser compatibles con la tecnología TTL. Cuando la dirección y el programa son estables, se debe hacer presente el pulso activo de programación durante 45 mseg. Se puede programar cualquier localidad en cualquier tiempo en forma secuencial o con acceso aleatorio,. El pulso de programación debe tener una duración máxima de 55 mseg. La EPROM 2716 no debe ser programada con una señal de CD en la terminal de programación (CE)'. Se pueden programar varias EPROM 2716 en paralelo con la misma información, debido a la simplicidad de los requerimientos de programación. 26