Organización lógica Identificación de bloque

Anuncio

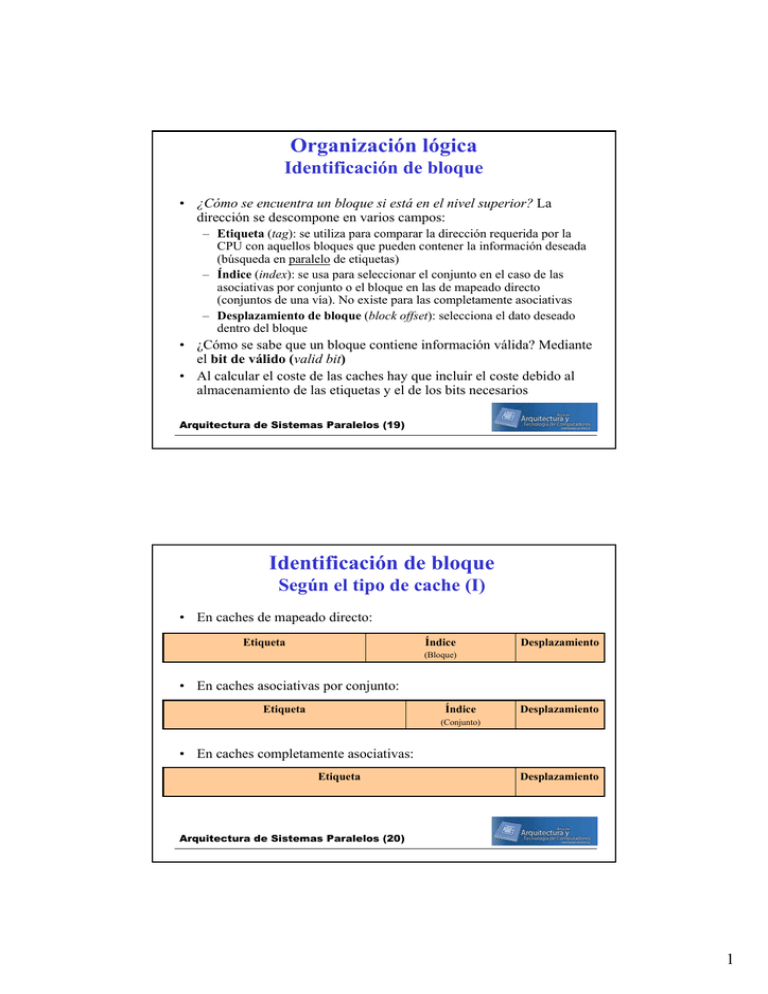

Organización lógica Identificación de bloque • ¿Cómo se encuentra un bloque si está en el nivel superior? La dirección se descompone en varios campos: – Etiqueta (tag): se utiliza para comparar la dirección requerida por la CPU con aquellos bloques que pueden contener la información deseada (búsqueda en paralelo de etiquetas) – Índice (index): se usa para seleccionar el conjunto en el caso de las asociativas por conjunto o el bloque en las de mapeado directo (conjuntos de una vía). No existe para las completamente asociativas – Desplazamiento de bloque (block offset): selecciona el dato deseado dentro del bloque • ¿Cómo se sabe que un bloque contiene información válida? Mediante el bit de válido (valid bit) • Al calcular el coste de las caches hay que incluir el coste debido al almacenamiento de las etiquetas y el de los bits necesarios Arquitectura de Sistemas Paralelos (19) Identificación de bloque Según el tipo de cache (I) • En caches de mapeado directo: Etiqueta Índice Desplazamiento (Bloque) • En caches asociativas por conjunto: Etiqueta Índice Desplazamiento (Conjunto) • En caches completamente asociativas: Etiqueta Desplazamiento Arquitectura de Sistemas Paralelos (20) 1 Identificación de bloque Según el tipo de cache (II) Memoria: 32 bloques Caches: 8 bloques Tres tipos: - Completamente asociativas - De correspondencia directa - Asociativa por conjuntos de 2 vías Arquitectura de Sistemas Paralelos (21) Identificación de bloque Ejemplos • • • 1 2 3 Procesador de 16 bits de datos y 24 de direcciones Tamaño de la cache: 8Kb Tamaño de la línea: 8 bytes 1. Cache completamente asociativa 2. Cache asociativa por conjuntos de 4 vías 3. Cache de mapeado directo Etiqueta: 21bits Desplazamiento: 3bits Palabra: 2bits Etiqueta: 13bits Conjunto: 8bits Desplazamiento: 3bits Palabra: 2bits Etiqueta: 11bits Bloque: 10bits Byte:1bit Byte:1bit Desplazamiento: 3bits Palabra: 2bits Byte:1bit Arquitectura de Sistemas Paralelos (22) 2 Identificación de bloque Implementación de caches de mapeado directo Arquitectura de Sistemas Paralelos (23) Identificación de bloque Implementación de caches totalmente asociativas Arquitectura de Sistemas Paralelos (24) 3 Identificación de bloque Implementación de caches asociativas por conjuntos Arquitectura de Sistemas Paralelos (25) Identificación de bloque Ejemplo: VAX-11/780 - Cache asociativa por conjunto de 2 vías - Capacidad de datos: 8Kb - Tamaño de bloque: 8 bytes - Número de conjuntos: 512 Pasos de un acierto: 1) División de la dirección 2) Acceso a ambos bancos 3) Comparación de etiquetas 4) Multiplexación 5) Envío a la CPU Arquitectura de Sistemas Paralelos (26) 4 Organización lógica Políticas de sustitución de bloque (I) • ¿Qué bloque debe reemplazarse en caso de fallo? Se pueden seguir diferentes estrategias: – Aleatoria (Random): Se elige un bloque al azar – FIFO (First Input First Out): Se sustituye el bloque que más tiempo ha estado en la cache – LRU (Least Recently Used): Se sustituye el bloque que más tiempo ha estado en la cache sin ser referenciado – LFU (Least Frecuently Used): Se sustituye el bloque que menos referencias ha tenido • Se tienen en cuenta criterios de coste y eficiencia • Los esquemas más utilizados son el aleatorio y el LRU Arquitectura de Sistemas Paralelos (27) Organización lógica Políticas de sustitución de bloque (II) Ejemplo de política LRU (cache de 4 bloques) Dirección Bloque LRU 0 3 2 1 0 0 2 3 1 3 0 0 0 0 3 3 3 1 0 0 2 Comparativa de frecuencias de fallos (VAX, 16bytes/bloque) Arquitectura de Sistemas Paralelos (28) 5 Organización lógica Políticas de escritura (I) • ¿Qué ocurre en una escritura? Opciones a la hora de escribir en la cache: – Escritura directa (Write through): La información se escribe en el bloque de la cache y en el bloque de la memoria de nivel inferior – Postescritura (Copy Back): La información se escribe sólo en el bloque de la cache. El bloque modificado de la cache se escribe en la memoria de nivel inferior sólo cuando es reemplazado • Los bloques de las caches copy back se denominan sucios o modificados cuando la información de la cache difiere de la memoria de nivel inferior • Para reducir la frecuencia de postescrituras en el reemplazo se usa el bit de modificación o sucio (dirty bit): si el bloque está limpio no se escribe en el nivel inferior • Cuando una cache es write through, la CPU debe esperar la finalización de cada escritura antes de proceder con la siguiente operación. Para evitarlo se utiliza un buffer de escritura que permite al procesador continuar mientras se actualiza la memoria Arquitectura de Sistemas Paralelos (29) Organización lógica Políticas de escritura (II) • Vetajas de las caches copy back: – En las caches copy back, las escrituras se realizan a la velocidad de la memoria cache, y múltiples escrituras en un bloque requieren sólo una escritura en la memoria de nivel inferior – Como cada escritura no va a memoria, la postescritura utiliza menos ancho de banda (multiprocesadores) • Vetajas de las caches write through: – En las caches write through, los fallos de lectura no ocasionan escrituras en el nivel inferior – Las caches write through son más fáciles de implementar – La escritura directa tiene la ventaja también de que la memoria principal tiene la copia más reciente de los datos (coherencia de cache, multiprocesadores y E/S) Arquitectura de Sistemas Paralelos (30) 6 Organización lógica Políticas de escritura (III) • ¿Qué ocurre en una escritura? Opciones cuando se produce un fallo de escritura: – Ubicar en escritura (Write allocation): El bloque se carga en la cache y a continuación se escribe sobre él (similar a un fallo en lectura) – No ubicar en escritura (No write allocatation): El bloque se modifica en el nivel inferior y no se carga en la cache • Aunque cualquier política de fallo de escritura puede utilizarse con la escritura directa o con la postescritura, las caches copy back utilizan write allocation (CB WA) y las write through usan no write allocation (WT - N WA) Arquitectura de Sistemas Paralelos (31) Organización lógica Caches unificadas vs. Caches separadas • Caches unificadas o mixtas (unified or mixed): Contienen tanto datos como instrucciones • Caches separadas (separated): Existe una cache para datos y otra para instrucciones Ventajas – No hay competencia entre el procesador de instrucciones y la unidad de ejecución – Duplicación del ancho de bus (puertos separados) – Parámetros de diseño (capacidad, tamaños de bloque, asociatividad, etc.) diferentes para instrucciones y datos (optimización) Inconvenientes – En general la tasa de fallos global es algo mayor (próxima transparencia): • la caches de instrucciones tienen menor frecuencia de fallos que las de datos (localidad) • la separación de instrucciones y datos elimina fallos debidos a conflictos pero al dividir también se fija el espacio de cache dedicado a cada tipo – No se equilibra la carga de trabajo de forma automática Arquitectura de Sistemas Paralelos (32) 7