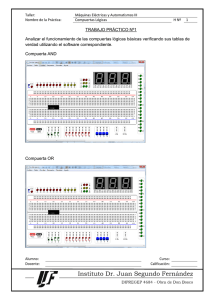

Práctica 1 Compuertas Lógicas

Anuncio

UASLP – FI Laboratorio de Sistemas Digitales Práctica 1 Práctica 1 Compuertas Lógicas 1.1 Objetivo Conocer el funcionamiento, conexión y utilización de las compuertas lógicas AND, OR, NOT, NAND, NOR, EX -OR y EX -NOR. 1.2 Antecedentes Los sistemas digitales están compuestos de una serie de circuitos integrados que ejecutan instrucciones para controlar sistemas mecánicos, eléctricos, neumáticos entre otros. La base de los sistemas digitales son los operadores lógicos que dan forma a sistemas que obedecen a tablas de verdad, grafos de transiciones, cartas algorítmicas, y que mediante comparaciones, corrimientos lógicos, aritméticos y almacenamiento de datos, entre otras operaciones; dan como resultado, un proceso digital que a través de adecuados circuitos de acoplamiento, interactúan como etapa de control sistemas de procesamiento de datos, como dispositivos decodificadores para exhibidores de siete segmentos, pantallas cristal líquido, como etapa de activación, monitoreo y control en sistemas con motores, electroválvulas, sistemas de computo, sistemas de comunicaciones, entre otros. Los sistemas digitales como ciencia, se basan en la teoría de conjuntos y el algebra de Boole, la cual está soportada mediante una cantidad suficiente de teoremas y postulados que permiten trabajar con el sistema binario en donde el universo digital de números se reduce a sólo 0s y 1s. De esta forma es relativamente fácil trabar la electrónica digital en el sistema binario que con el sistema decimal. En el sistema binario solamente se utilizan dos guarismos: el 0 y el 1 para representar las cantidades, de ahí su denominación de binario. A estos guarismos se les conoce como bits. Las señales físicas correspondientes a los dígitos (bits) que procesa el sistema digital son, por tanto, señales binarias. En la práctica, los voltajes típicos correspondientes a los circuitos integrados digitales de tecnología Lógica Transistor Transistor (TTL), son de 0 - 0.5V para el valor lógico (0) y de 3.5 - 5.0 V para el valor lógico (1). Esto se ilustra en la figura 1.1 y la interpretación de los valores lógicos en los sistemas digitales en la tabla 1. 1. 1 (3.5V) 0 (0 V) Figura 1.1 Valores típicos de voltaje para niveles de entrada en los circuitos integrados (CI) TTL. Tabla 1.1 Interpretación de los valores lógicos en los sistemas digitales. 0 Lógico Falso Desactivado Nivel Bajo (L) No Interruptor Abierto 1 Lógico Verdadero Activado Nivel Alto (H) Sí Interruptor Cerrado En el álgebra de Boole existen operadores binarios que obedecen a cada uno de los teoremas y postulados del álgebra de Boole. Los operadores lógicos principales son: AND (y), OR (o) y NOT (no), de ahí se derivan otros operadores que complementan los reglas de algebra de Boole. Puesto que las funciones booleanas se expresan en términos de operaciones AND (y), OR (o) y NOT (no), es más fácil implementar una función booleana con estos tipos de compuertas. La posibilidad de construir compuertas para las otras operaciones lógicas tiene un interés práctico. 2 UASLP – FI Laboratorio de Sistemas Digitales Práctica 1 Los circuitos integrados (CI) que se basan en los operadores lógicos antes mencionados, ejecutan una variedad de funciones lógicas a través de las llamadas compuertas lógicas. Las compuertas lógicas son bloques de construcción básica de los sistemas digitales que operan con niveles lógicos (que representan a los números binarios), por lo que se denominan compuertas lógicas binarias. Las compuertas ejecutan las operaciones lógicas de OR, AND y NOT. 1.2.1 Operaciones lógicas y compuertas Los operadores básicos representados en cada una de las compuertas solamente contienen dos entradas y una salida. Operador y compuerta OR Considerando como entradas a ‘A’ y ‘B’, y como salida a X, la operación OR se expresa como A + B = X . Lo que indica que si para las entradas A o B la salida es X. El CI de la compuerta OR es un circuito que internamente contiene desde cuatro hasta una compuerta lógica que puede tener como mínimo dos o máximo doce entradas lógicas y cuya salida es igual a la operación OR de todas las entradas que intervengan en esa compuerta. Como puede observar en la figura 1.2, la que muestra la tabla de verdad, el símbolo representativo del operador lógico y la simbología normalizada de la compuerta OR. TABLA DE VERDAD DE LA OPERACIÓN LÓGICA OR A B SIMBOLOGÍA IEEE DE LA COMPUERTA OR SIMBOLOGÍA CONVENCIONAL DE LA COMPUERTA OR X=A+B A 0 0 1 1 0 1 0 1 0 1 1 1 X B A 0 B 0 >=1 >= 1 0 X Figura 1.2 Tabla de verdad, operador lógico y simbología estándar de la compuerta OR (IEEE STD). Operador y compuerta AND Considerando como entradas a ‘A’ y ‘B’, y como salida a X. La operación AND Se expresa como A • B = X . Lo que indica que si para las entradas A y B la salida es X. La operación AND en un circuito integrado obedece a la tabla de verdad que se ilustra en la figura 1.3. De tal forma que la salida X está en su nivel alto si y solo si las entradas ‘A’ y ‘B’ están en nivel alto (3.5-5 Volts), para los otros casos la salida X de la compuerta AND estará en nivel bajo. La figura 1.3 muestra la tabla de verdad, el símbolo representativo de el operador AND y el diagrama estándar simplificado. TABLA DE VERDAD DE LA OPERACIÓN LÓGICA AND A B SIMBOLOGÍA CONVENCIONAL DE LA COMPUERTA AND SIMBOLOGÍA IEEE DE LA COMPUERTA AND X=A*B A 0 0 1 1 0 1 0 1 0 0 0 1 X B A 0 B 0 >=1 & 0 X Figura1.3 Tabla de verdad, operador lógico y simbología estándar de la compuerta AND (IEEE STD). 3 UASLP – FI Laboratorio de Sistemas Digitales Práctica 1 Operador NOT La operación NOT difiere de las operaciones AND y OR, ya que la operación NOT tiene efecto sobre una sola variable de entrada. En este operador para una entrada ‘A’ entregará a la salida la negación de ‘A’ o mejor conocido como el complemento de ‘A’. Por ejemplo, si la variable de entrada ‘A’ se somete a la operación NOT, la salida X = A , donde la barra superpuesta representa la operación NOT. El operador NOT o inversor solamente posee una entrada y una salida. Esta operación lógica siempre entregará a la salida una señal complemento de la entrada (contraria a su entrada). En la tabla de verdad de la figura 1.4 se puede apreciar que para una entrada 0 (nivel bajo) la salida es 1 (nivel alto), y para una entrada 1 (nivel alto) la salida es 0 (nivel bajo). La figura 1.4 muestra el símbolo básico representativo del operador lógico NOT y su símbolo estándar. TABLA DE VERDAD DE LA OPERACIÓN LÓGICA NOT A 0 1 SIMBOLOGÍA CONVENCIONAL DE LA COMPUERTA NOT SIMBOLOGÍA IEEE DE LA COMPUERTA NOT X=A 0 A 1 0 A X 0 >=1 1 0 X Figura 1.4 Tabla de verdad, operador lógico y simbología estándar de la compuerta NOT (IEEE STD). Las compuertas NAND y NOR Otros operadores que complementan a los teoremas y postulados del algebra de Boole nacen a partir de de el complemento de los operadores lógicos básicos AND y OR. En los circuitos digitales son de gran utilidad estas nuevas operaciones que permiten la síntesis de sistemas de gran complejidad. Los nuevos operadores son: NOR y NAND. El operador NOR es el complemento del operador OR es decir NOT-OR nos da el operador NOR y la operación NAND es el complemento de la operación AND es decir NOTAND. En la figura 1.5 se ilustra la simbología y su correspondiente equivalencia de las compuertas NAND y NOR. Comercialmente se encuentran CIs que contienen desde una compuerta NOR/NAND con doce entradas y una salida o cuatro compuertas NOR/NAND con 2 entradas y una salida cada una. NOR OR NAND NOT (a) AND NOT ( b) Figura 1.5 (a) Símbolo y circuito equivalentes de la compuerta NOR, (b) símbolo y circuito equivalente de la compuerta NAND. Operador NOR Dadas dos entradas lógicas ‘A’ y ‘B’ y una salida X. El operador lógico NOR realiza la suma complemento y se representa como: X = ( A + B) . Donde la barra superpuesta sobre la operación OR indica el complemento o negación de la operación. La figura 1.6 muestra la tabla de verdad y los símbolos representativos de la compuerta NOR. 4 UASLP – FI Laboratorio de Sistemas Digitales TABLA DE VERDAD DE LA OPERACIÓN LÓGICA NOR A B Práctica 1 SIMBOLOGÍA IEEE DE LA COMPUERTA NOR SIMBOLOGÍA CONVENCIONAL DE LA COMPUERTA NOR X=(A+B) A A 0 0 1 1 0 1 0 1 & >= 1 X 1 0 0 0 0 B B 0 X 0 Figura 1.6 Tabla de verdad, operador lógico y simbología estándar de la compuerta NOR (IEEE STD). Operador NAND Este operador realiza la operación AND complemento su tabla de verdad es exactamente al contrario de la que se obtiene al ejecutar al operador AND. Sean ‘A’ y ‘B’ las variables de entrada y X la salida. La operación NAND entre las dos variables de entrada es X = ( A • B) . Donde la barra superpuesta sobre la operación AND indica negación o el complemento de la operación. La figura 1.7 muestra la tabla de verdad del operador NAND, como puede observarse y compararse la tabla de verdad es completamente invertida a la de la operación AND. SIMBOLOGÍA CONVENCIONAL DE LA COMPUERTA NAND TABLA DE VERDAD DE LA OPERACIÓN LÓGICA NAND A B SIMBOLOGÍA IEEE DE LA COMPUERTA NAND X=(A*B) A 0 0 1 1 0 1 0 1 0 B 0 >=1 & X 1 1 1 0 A B 0 X Figura 1.7 Tabla de verdad, operador lógico y simbología estándar de la compuerta NAND (IEEE STD). Los operadores lógicos XOR y XNOR El operador OR – exclusiva o XOR La función OR- exclusiva o XOR se expresa de la siguiente forma. X = AB + AB es posible ser construida tal como se observa en la figura 1.8. NOT AND A OR NOT AND X= AB+AB B Figura 1.8 Circuito sistemático del operador OR- exclusivo (XOR). Este operado produce entrega un nivel bajo (0 lógico) cuando las entras ‘A’ y ‘B’ tienen el mismo valor, y se obtiene el nivel alto (1 lógico), cuando las entradas son diferentes. La tabla de verdad y el símbolo representativo de la compuerta XOR se presentan en la figura 1.9. 5 UASLP – FI Laboratorio de Sistemas Digitales TABLA DE VERDAD DE LA OPERACIÓN LÓGICA XOR A B SIMBOLOGÍA CONVENCIONAL DE LA COMPUERTA XOR Práctica 1 SIMBOLOGÍA IEEE DE LA COMPUERTA XOR X=AB+AB A 0 0 1 1 0 1 0 1 0 B 0 =1 =1 X 0 1 1 0 A B 0 X Figura 1.9 Tabla de verdad, operador lógico y simbología estándar de la compuerta XOR (IEEE STD). Operador NOR – exclusiva, XNOR. La compuerta XNOR trabaja de manera contraria a la operación XOR. Dadas dos entradas ‘A’ y ‘B’ con salida ‘X’, la expresión del operador XNOR es X = AB + ( AB) . Esto quiere decir que para A y B iguales la salida X será 1 lógico (5 volts) y la A deferente de B la salida X será 0 lógico (0 volts). A AND A OR B B X=AB+(AB) AND A B Figura 1.10 Circuito esquemático de la compuerta NOR- exclusivo (XNOR). La tabla de verdad y el símbolo representativo de la compuerta XNOR se presentan en la figura 1.11. TABLA DE VERDAD DE LA OPERACIÓN LÓGICA XNOR A B SIMBOLOGÍA CONVENCIONAL DE LA COMPUERTA XNOR X=AB+(AB) A 0 0 1 1 0 1 0 1 SIMBOLOGÍA IEEE DE LA COMPUERTA XNOR 1 0 0 1 X B A 0 B 0 >=1 =1 0 X Figura 1.11 Circuito equivalente de salida de la compuerta XNOR- exclusivo 6 UASLP – FI Laboratorio de Sistemas Digitales Práctica 1 1.3 Desarrollo de la práctica • Empleando el paquete de simulación CircuitMaker o Electronics Workbench (Multisim), arme los circuitos mostrados en la figura 1.12 (a) y 1.12 (b) y compruebe su tabla de verdad. o NOTA: Estos elementos, en la mayoría de los paquetes de simulación son dispositivos discretos. Sin embargo, en la práctica se encuentran empaquetados en CI con varios pines de conexión que corresponden a entradas, salidas, alimentación (Vcc) y tierra. Deberá consultar una hoja de datos correspondiente a cada elemento para ver su estructura interna y comenzar a armar su circuito de prueba para los siguientes puntos. 5V 5V 74LS32 74LS04 1K 330 5V 1K 1K 330 (a) (b) Figura 1.12 (a) Circuito de prueba utilizando una compuerta Inversora, (b) circuito de prueba utilizando una compuerta OR. • Implemente los circuitos de prueba mostrados en la figura 1.12 (a) y 1.12 (b). Intercambie el circuito integrado de la figura 1.12 (b) correspondiente a las operaciones lógicas descritas en la práctica (AND, NOR, NAND y XOR) y en cada caso compruebe la salida mediante el manejo de las entradas correspondientes a cada una de las compuertas utilizadas y compare lo obtenido con su respectiva tabla de verdad. 32 LS 74 (a) (b) Figura 1.13 (a) Conexión de CI 74LS04 (NOT), (b) Conexión del CI 74LS32 (OR). 7 UASLP – FI Laboratorio de Sistemas Digitales Práctica 1 La figura 1.13 muestra la forma de conectar las compuertas mostradas en la figura 1.12. Nota. Antes de empezar a probar los experimentos, verifique que todo CI esté correctamente montado en la tablilla de proyectos (Proto board), que esté perfectamente energizado y conexiones a tierra. En caso de no estar seguro de lo anterior, pregunte al instructor. • Empleando los CI, ahora realice las conexiones necesarias para obtener una compuerta de tres entradas y una salida. Obtenga su tabla de verdad mediante mediciones. Observe la figura 1.114, es un ejemplo de cómo interconectar las compuertas para obtener una compuerta lógica de tres entradas y una salida. Vea que la salida de la compuerta 1 es una señal de entrada a la compuerta 2. LS 74 32 Figura 1.14 Conexión de CI del CI 74LS32 (OR) para obtener una compuerta OR de tres entradas. • Anote sus conclusiones y responda el cuestionario de la práctica. 1.3.1 Material y equipo Material Cantidad 1 1 1 1 3 2 1 1 1 1 1 1 Elemento Fuente de 5 VCD Tablilla de conexiones Interruptor DIP Diodo Emisor de Luz Resistencias de 1KΩ Resistencia 330 Ω 74LS00 74LS02 74LS04 74LS08 74LS32 74LS86 Descripción Fuente de alimentación Para circuitos integrados 4 entradas de cambio deslizable Estándar Para proteger de un corto circuito el circuito Para protección de diodo emisor de luz. Circuito integrado NAND de dos compuertas Circuito integrado NOR de dos compuertas Circuito integrado inversor Circuito integrado AND de dos entradas Circuito integrado OR de dos entradas Circuito integrado XOR de dos entradas Elemento Unidad de cómputo Probador lógico de CI Descripción Equipada con el programa Circuit Maker y/o Electronics Workbench. Utilidad opcional para comprobar estado de los CI Equipo Cantidad 1 1 8 UASLP – FI Laboratorio de Sistemas Digitales Práctica 1 1.4 Conclusiones 1.5 Cuestionario 1) ¿Cuál es la razón de conectar resistencias a tierra en cada una de las entradas y salidas de los circuitos que se desarrollaron en la práctica? 2) Utilizando compuertas de dos entradas (AND y OR), realice las conexiones necesarias para obtener una compuerta de cuatro entradas y una salida y empleando algún paquete de simulación obtenga su tabla de verdad. 3) Investigue qué clase de fallas pueden ocurrir en los circuitos integrados. 4) Dibuje el circuito electrónico correspondiente a una compuerta NAND básica de la serie LS-TTL. 5) Investigue el tema de funciones lógicas en sus formas canónicas. Anexar las simulaciones de los circuitos solicitados 9