Introducción a los microprocesadores MIPS.

Anuncio

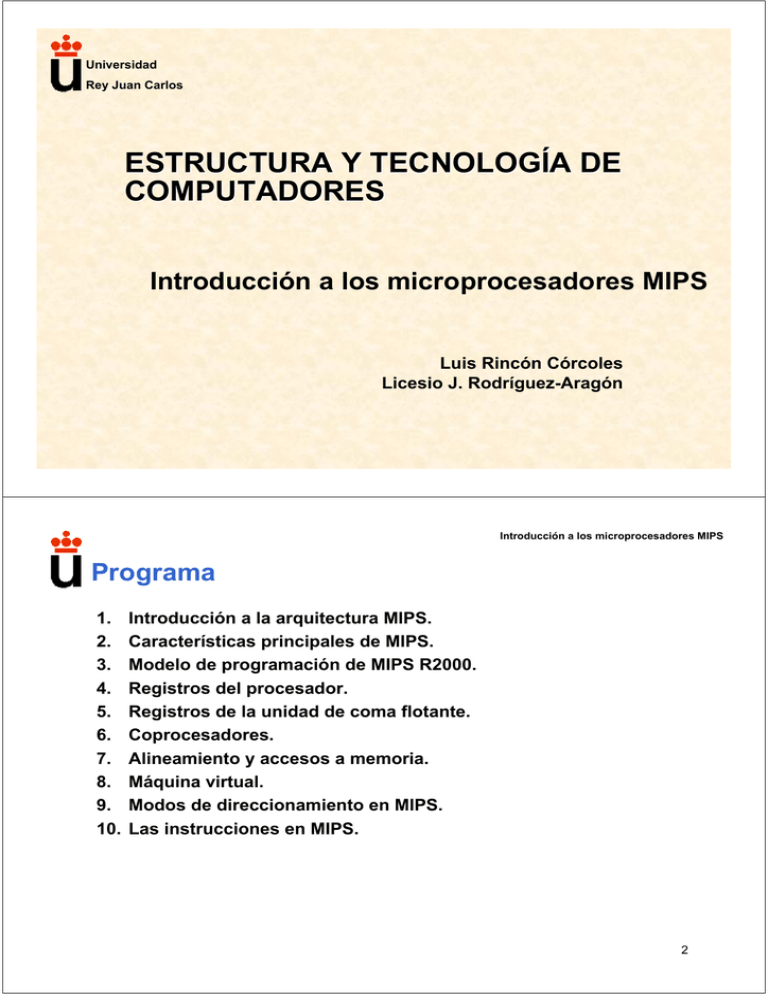

Universidad Rey Juan Carlos ESTRUCTURA Y TECNOLOGÍA DE COMPUTADORES Introducción a los microprocesadores MIPS Luis Rincón Córcoles Licesio J. Rodríguez-Aragón Introducción a los microprocesadores MIPS Programa 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. Introducción a la arquitectura MIPS. Características principales de MIPS. Modelo de programación de MIPS R2000. Registros del procesador. Registros de la unidad de coma flotante. Coprocesadores. Alineamiento y accesos a memoria. Máquina virtual. Modos de direccionamiento en MIPS. Las instrucciones en MIPS. 2 Introducción a los microprocesadores MIPS Bibliografía  D.A. PATTERSON, J.L HENNESSY. Estructura y diseño de computadores. Reverté, 2000.  D. SWEETMAN. See MIPS Run. Morgan Kaufmann, 2002.  E. FARQUHAR, P. BUNCE. The MIPS Programmer’s Handbook. Morgan Kaufmann, 1994.  J. GOODMAN, K. MILLER. A Programmer’s View of Computer Architecture. Saunders College Pub., 1993.  MIPS32 Architecture For Programmers – Volume I: Introduction to the MIPS32 Architecture. MIPS Technologies Inc., 2003.  MIPS32 Architecture For Programmers – Volume II: The MIPS32 Instruction Set. MIPS Technologies Inc., 2003.  MIPS32 Architecture For Programmers – Volume III: The MIPS32 Privileged Resource Architecture. MIPS Technologies Inc., 2003.  MIPS64 Architecture For Programmers – Volume I: Introduction to the MIPS64 Architecture. MIPS Technologies Inc., 2003.  MIPS64 Architecture For Programmers – Volume II: The MIPS64 Instruction Set. MIPS Technologies Inc., 2003.  MIPS64 Architecture For Programmers – Volume III: The MIPS64 Privileged 3 Resource Architecture. MIPS Technologies Inc., 2003. Introducción a los microprocesadores MIPS 1. Introducción a la arquitectura MIPS •Segmentación de instrucciones: técnica de implementación de unidades de control que permite tratar las instrucciones en serie dividiéndolas en fases. Con un único cauce de ejecución de instrucciones es posible mantener ejecutándose simultáneamente varias instrucciones, cada una en una fase distinta. •MIPS es una arquitectura diseñada para optimizar la segmentación en unidades de control y para facilitar la generación automática de código máquina por parte de los compiladores. •MIPS: Microprocessor without Interlocked Pipeline Stages (microprocesador sin bloqueos en las etapas de segmentación). •MIPS es RISC (computador con repertorio de instrucciones reducido). •Existen múltiples fabricantes de microprocesadores con arquitectura MIPS. 4 Introducción a los microprocesadores MIPS Arquitectura frente a implementación •Distinción arquitectura-implementación: Arquitectura: repertorio de instrucciones, registros, modelo de excepciones, manejo de memoria virtual, mapa de direcciones físicas y otras características comunes. Implementación: forma en que los procesadores específicos aplican la arquitectura. •La arquitectura MIPS está desacoplada de las implementaciones hardware específicas Se deja libertad a los diseñadores de microprocesadores a la hora de crear sus propios diseños dentro del marco de definición de la arquitectura. •Las implementaciones de las arquitecturas MIPS deben cumplir una serie de requisitos. Todas las instrucciones normales deben estar implementadas. La implementación de la coma flotante y de los restantes coprocesadores es opcional. El modo de ejecución de supervisor es opcional. Etc. 5 Introducción a los microprocesadores MIPS Versiones de MIPS •Versiones históricas del repertorio de instrucciones MIPS ISA (MIPS Instruction Set Architecture). Versión Ancho de los registros Procesadores Comentarios MIPS I 32 R2000, R3000 Versión comercial del procesador MIPS de la Universidad de Stanford MIPS II 32 R6000 Base del estándar MIPS32 MIPS III 64 R4000 Primera arquitectura MIPS de 64 bits MIPS IV 64 R5000, R10000 Actualización menor de MIPS III MIPS V 64 - Base del estándar MIPS64 •El modo de ejecución de usuario siempre es compatible hacia atrás. El entorno privilegiado no formaba parte del MIPS ISA, sino que puede variar dependiendo de la implementación. 6 Introducción a los microprocesadores MIPS Arquitecturas MIPS ISA actuales •MIPS32: Basada en MIPS II ISA. Incluye algunas instrucciones de MIPS III, IV y V para aumentar la eficiencia del código generado y la de la transferencia de datos. MIPS32 Release 1: lanzamiento inicial. MIPS32 Release 2: lanzada en 2002, incorpora una serie de mejoras. •MIPS64: Basada en MIPS V ISA. Es compatible hacia atrás con MIPS32. •Ambas arquitecturas incluyen la definición del entorno privilegiado (MIPS PRA: Privileged Resource Architecture). •Ambas arquitecturas prevén la adición de: MIPS ASEs: Application Specific Extensions (extensiones específicas dependientes de la aplicación). MIPS UDIs: User Defined Instructions (instrucciones definidas por el usuario). Coprocesadores específicos custom adaptados a la especificidad de las necesidades 7 del mercado. Introducción a los microprocesadores MIPS Relación entre MIPS32 y MIPS64 •MIPS32 es un subconjunto de MIPS64. •MIPS64 es compatible hacia atrás con MIPS32. 8 Introducción a los microprocesadores MIPS 2. Características principales de MIPS32 •Máquina RISC (computador con repertorio de instrucciones reducido). •Ancho de palabra y tamaño de los buses: 32 bits. •Tamaño de los datos en las instrucciones: Byte (b): 8 bits Halfword (h): 16 bits Word (w): 32 bits Doubleword (d): 64 bits •Arquitectura de carga / almacenamiento: Antes de ser utilizado en una instrucción aritmética, todo dato debe ser cargado previamente en un registro de propósito general. Instrucciones aritméticas con 3 operandos de 32 bits en registros. •Esquema de bus único para memoria y E/S. •Modos de funcionamiento: usuario, núcleo (kernel), supervisor y depuración. 9 Introducción a los microprocesadores MIPS 3. Modelo de programación de MIPS R2000 Memory CPU Coprocessor 1 (FPU) Registers Registers $0 $0 $31 $31 Arithmetic unit Multiply divide Lo Arithmetic unit Hi Coprocessor 0 (traps and memory) Registers BadVAddr Cause Status EPC 10 Introducción a los microprocesadores MIPS 4. Registros del procesador •32 registros de propósito general •Registros propósito específico: HI-LO: para productos y divisiones. PC. •Ancho de los registros: 32 bits. 11 Introducción a los microprocesadores MIPS Registros del procesador  En MIPS los registros $0 a $31 son de propósito general pueden emplearse para contener datos o punteros.  Existe un convenio que dota de pseudónimos y usos determinados a todos los registros del MIPS: • • • • • • • • • • • $s0 ... $s7 ($16 ... $23): respetados en llamadas a subprogramas. $t0 ... $t9 ($8 ... $15, $24 y $25): no respetados en llamadas a subprogramas. $v0 y $v1 ($2 y $3): valores de retorno de subprogramas. $a0 ... $a3 ($4 ... $7): argumentos para subprogramas. $zero ($0): valor constante 0 (no modificable). $gp ($28): puntero a zona de datos globales. $sp ($29): puntero de pila. $fp ($30): puntero a bloque de activación. $ra ($31): dirección de retorno (usado implícitamente en la instrucción jal). $at ($1): uso interno del traductor de ensamblador en pseudoinstrucciones. $k0 y $k1 ($26 y $27): uso privado del núcleo del sistema operativo (kernel).  Los registros $s0 ... $s7, $t0 ... $t9, $a0 ... $a3, $v0 y $v1 pueden contener tanto datos de cualquier tipo como punteros. 12 Introducción a los microprocesadores MIPS 5. Registros de la unidad de coma flotante •32 registros. •Ancho de los registros: 32 bits. •En instrucciones de precisión simple se pueden usar todos los registros: $0, $1, $2, $3, ... $31. •En instrucciones de precisión doble, los registros se usan en parejas de dos registros par-impar: $0,$2,$4, ... $30. 13 Introducción a los microprocesadores MIPS 6. Coprocesadores •Hasta 4 coprocesadores. Hasta 32 registros cada uno, accesibles mediante instrucciones específicas. •Coprocesador 0: Coprocesador de control de sistema (System Control Coprocessor). Obligatorio e incorporado en el chip de la UCP. Controla el susbsistema de memoria caché. Soporta el sistema de memoria virtual y traduce direcciones virtuales en físicas. Soporta el manejo de excepciones. Maneja los cambios en el modo de ejecución (usuario, núcleo, supervisor). Proporciona control de diagnósticos y recuperación ante errores. •Coprocesador 1: Reservado para la unidad de coma flotante. •Coprocesador 2: Reservado para implementaciones específicas. •Coprocesador 3: Reservado para la unidad de coma flotante en MIPS64 Release 2. 14 Introducción a los microprocesadores MIPS 7. Alineamiento y accesos a memoria •MIPS puede funcionar con ordenación de datos little-endian o big-endian. Big-endian Little-endian •Normalmente se exige que los accesos a memoria estén alineados. Accesos a byte: sin alinear. Accesos a media palabra: alineados a dirección par. Accesos a palabra: alineados a dirección múltiplo de 4. Accesos a doble palabra: alineados a dirección múltiplo de 8. 15 Introducción a los microprocesadores MIPS 8. Máquina virtual  MIPS es una arquitectura RISC.  MIPS está diseñado para ser programado en alto nivel. • La programación en bajo nivel es bastante incómoda.  Los ensambladores para MIPS proporcionan al programador una máquina virtual que le hace un poco menos incómodo programar en bajo nivel. • Pseudoinstrucciones: instrucciones proporcionadas por el ensamblador.  Las pseudoinstrucciones sólo deberían ser utilizadas por los programadores, nunca por los compiladores.  El traductor de ensamblador oculta algunas otras características de los procesadores MIPS. • Huecos de retardo. 16 Introducción a los microprocesadores MIPS 9. Modos de direccionamiento en MIPS  Direccionamiento directo a registro.  Direccionamiento indirecto a registro con desplazamiento.  Direccionamiento relativo a PC con desplazamiento.  Direccionamiento inmediato.  Direccionamiento pseudodirecto.  Direccionamiento implícito. 17 Introducción a los microprocesadores MIPS Direccionamiento directo a registro  El campo tiene 5 bits.  Permitido para operando fuente o destino. Register addressing op rs rt rd ... funct Registers Register  Notación: $n  Los registros tienen alias, indicando la función para la que están dedicados según los convenios adoptados por programadores y compiladores. 18 Introducción a los microprocesadores MIPS Direccionamiento indirecto a registro con desplazamiento  Campos: • Registro: 5 bits. • Desplazamiento: 16 bits.  Permitido para operando fuente en almacenamientos y destino en cargas. Base addressing op rs rt Memory Address + Register Byte Halfword Word  Notación: desp($n) 19 Introducción a los microprocesadores MIPS Direccionamiento relativo a PC con desplazamiento  Campos: • Desplazamiento: 16 bits.  El desplazamiento se alinea a múltiplo de 4 (se multiplica por 4, o lo que es lo mismo, es desplazado dos posiciones a la izquierda) y se extiende en signo a 32 bits para calcular la dirección efectiva.  Se utiliza para direcciones en bifurcaciones. PC-relative addressing op rs rt Memory Address PC + Word  Notación: oculto en etiqueta. 20 Introducción a los microprocesadores MIPS Direccionamiento inmediato  Campos: • Inmediato de 16 bits.  Los datos inmediatos se extienden a 32 bits. • En ciertas instrucciones se hace extensión de signo. • En otras instrucciones se hace extensión con ceros.  También se usa para indicar la longitud de un desplazamiento. • En este caso el inmediato es de 5 bits.  Permitido sólo para operandos fuente. Immediate addressing rs op rt Immediate  Notación: dato (sin prefijo) 21 Introducción a los microprocesadores MIPS Direccionamiento pseudodirecto  Campos: • Dirección de 26 bits.  La dirección se desplaza dos bits a la izquierda, y se concatena a los cuatro primeros bits del contador de programa.  Se utiliza en instrucciones de salto. Pseudodirect addressing op Memory Address PC | Word  Notación: direccion (sin prefijo) 22 Introducción a los microprocesadores MIPS Direccionamiento implícito  Un operando tiene direccionamiento implícito cuando está determinado por el código de operación.  En MIPS hay pocos casos. 23 Introducción a los microprocesadores MIPS 10. Las instrucciones en MIPS •Máquina RISC (computador con repertorio de instrucciones reducido). •Arquitectura de carga / almacenamiento. Antes de ser utilizado en una instrucción aritmética, todo dato debe ser cargado previamente en un registro de propósito general. •Tamaño de las instrucciones: 32 bits. •Número de operandos: 0, 1, 2 ó 3. Instrucciones de carga o almacenamiento: 2 operandos, uno en registro y el otro en memoria (de 8, 16 ó 32 bits). Instrucciones aritméticas o lógicas: 3 operandos de 32 bits en registros. Instrucciones aritméticas o lógicas con un inmediato: 3 operandos, dos de 32 bits en registros, y el tercero inmediato de 16 bits con extensión de signo (ceros o unos). •Máquina virtual: el programador puede utilizar instrucciones y direccionamientos que no están incorporados en el hardware: pseudoinstrucciones. Las pseudoinstrucciones son proporcionadas por el ensamblador, que se encarga de traducirlas a código máquina. 24 Introducción a los microprocesadores MIPS Tipos de instrucciones en MIPS  Instrucciones de transferencia de datos.  Instrucciones aritméticas para enteros.  Instrucciones lógicas.  Instrucciones de activación condicional.  Instrucciones de rotación y desplazamiento.  Instrucciones de control de programa.  Instrucciones de control de sistema. 25 Introducción a los microprocesadores MIPS Instrucciones de transferencia de datos Sintaxis -------------------------lb rt,desp(rs) lbu rt,desp(rs) lh rt,desp(rs) lhu rt,desp(rs) lui rd,inm16 lw rt,desp(rs) lwcZ rt,desp(rs) lwl rt,desp(rs) lwr rt,desp(rs) sb rt,desp(rs) sh rt,desp(rs) sw rt,desp(rs) swcZ rt,desp(rs) swl rt,desp(rs) swr rt,desp(rs) mfcZ rt,rd mfhi rd mflo rd mtcZ rd,rt mthi rd mtlo rd T I I I I I I I I I I I I I I I I I I I I I Descripción -------------------------------------rt = ext_signo(Mem[desp+rs]7..0,32) rt = ext_ceros(Mem[desp+rs]7..0,32) rt = ext_signo(Mem[desp+rs]15..0,32) rt = ext_ceros(Mem[desp+rs]15..0,32) rd31..16 = inm16; rd15..0 = 0 rt = Mem[desp+rs] coprocesadorZ(rt) = Mem[desp+rs] rt31.16 = Mem[desp+rs] rt15..0 = Mem[desp+rs] Mem[desp+rs] = rt7..0 Mem[desp+rs] = rt15..0 Mem[desp+rs] = rt Mem[desp+rs] = coprocesadorZ(rt) Mem[desp+rs] = rt31.16 Mem[desp+rs] = rt15..0 rd = rt; rd: registro UCP; rt: registro del coprocesador Z rd = hi rd = lo rd = rt; rd: registro UCP; rt: registro del coprocesador Z hi = rd lo = rd 26 Introducción a los microprocesadores MIPS Instrucciones aritméticas y de desplazamiento para enteros e instrucciones lógicas Sintaxis -------------------------add rd,rs,rt addi rd,rs,inm16 addu rd,rs,rt addiu rd,rs,inm16 div rs,rt divu rs,rt mult rs,rt multu rs,rt sub rd,rs,rt subu rd,rs,rt T I I I I I I I I I I Descripción -------------------------------------rd = rs+rt rd = rs+ext_signo(inm16,32) rd = rs+rt rd = rs+ext_signo(inm16,32) lo = rs/rt; hi = rem(rs/rt) lo = rs/rt; hi = rem(rs/rt) hi-lo = rs1*s2 hi-lo = rs1*s2 rd = rs-rt rd = rs-rt and andi nor or ori xor xori rd,rs,rt rd,rs,inm16 rd,rs,rt rd,rs,rt rd,rs,inm16 rd,rs,rt rd,rs,inm16 I I I I I I I rd rd rd rd rd rd rd = = = = = = = rs rs rs rs rs rs rs sll sllv sra srav srl srlv rd,rt,shamt5 rd,rt,rs rd,rt,shamt5 rd,rt,rs rd,rt,shamt5 rd,rt,rs I I I I I I rd rd rd rd rd rd = = = = = = desp_log(rt,shamt5,izquierda) desp_log(rt,rs4..0,izquierda) desp_arit(rt,shamt5,derecha) desp_arit(rt,rs4..0,derecha) desp_log(rt,shamt5,derecha) desp_log(rt,rs4..0,derecha) AND rt AND ext_ceros(inm16,32) NOR rt OR rt OR ext_ceros(inm16,32) XOR rt XOR ext_ceros(inm16,32) 27 Introducción a los microprocesadores MIPS Instrucciones de activación condicional, control de programa y misceláneas Sintaxis -------------------------slt rd,rs,rt slti rd,rs,inm16 sltu rd,rs,rt sltiu rd,rs,inm16 T I I I I Descripción -------------------------------------Si rs < rt, rd = 1; si no, rd = 0 Si rs < ext_signo(inm16,32), rd = 1; si no, rd = 0 Si rs < rt, rd = 1; si no, rd = 0 Si rs < ext_signo(inm16,32), rd = 1; si no, rd = 0 bcZf bcZt beq bgez bgezal bgtz blez bltz bltzal bne j jal jalr jr I I I I I I I I I I I I I I Si Si Si Si Si Si Si Si Si Si PC ra rd PC I I I I Restaurar desde excepción (Restaura el registro Status) Llamada a un servicio del sistema ($v0: número del servicio) Provoca una excepción (código 1 reservado para el depurador) No operación etiqueta etiqueta rs,rt,etiqueta rs,etiqueta rs,etiqueta rs,etiqueta rs,etiqueta rs,etiqueta rs,etiqueta rs,rt,etiqueta objetivo objetivo rs,rd rs rfe syscall break codigo20 nop flag(coprocesadorZ) = 0, ramificar a etiqueta flag(coprocesadorZ) = 1, ramificar a etiqueta rs = rt, ramificar a etiqueta rs >= 0, ramificar a etiqueta rs >= 0, ramificar a etiqueta y enlazar ($ra = PC) rs > 0, ramificar a etiqueta rs <= 0, ramificar a etiqueta rs < 0, ramificar a etiqueta rs < 0, ramificar a etiqueta y enlazar ($ra = PC) rs <> rt, ramificar a etiqueta = PC31..28 || (objetivo << 2) = PC; PC = PC31..28 || (objetivo << 2) = PC; PC = rs = rs 28 Introducción a los microprocesadores MIPS Instrucciones para coma flotante (I) Sintaxis -------------------------mov.d fd,fs mov.s fd,fs T I I Descripción -------------------------------------fd = fs; fd y fs: registros de coma flotante de 64 bits fd = fs; fd y fs: registros de coma flotante de 32 bits abs.d abs.s add.d add.s div.d div.s mul.d mul.s neg.d neg.s sub.d sub.s fd,fs fd,fs fd,fs,ft fd,fs,ft fd,fs,ft fd,fs,ft fd,fs,ft fd,fs,ft fd,fs fd,fs fd,fs,ft fd,fs,ft I I I I I I I I I I I I fd fd fd fd fd fd fd fd fd fd fd fd = = = = = = = = = = = = abs(fs) abs(fs) fs+ft fs+ft fs/ft fs/ft fs*ft fs*ft -fs -fs fs-ft fs-ft cvt.d.s cvt.d.w cvt.s.d cvt.s.w cvt.w.d cvt.w.s fd,fs fd,fs fd,fs fd,fs fd,fs fd,fs I I I I I I fd fd fd fd fd fd = = = = = = convertir(fs); convertir(fs); convertir(fs); convertir(fs); convertir(fs); convertir(fs); precisión simple a precisión doble entero a precisión doble precisión doble a precisión simple entero a precisión simple precisión doble a entero precisión simple a entero 29 Introducción a los microprocesadores MIPS Instrucciones para coma flotante (II) Sintaxis -------------------------c.eq.d fs,ft T I Descripción -------------------------------------Si fs = ft, flag_coprocesador(1) = 1; si no, flag_coprocesador(1) = 0 c.eq.s fs,ft I Si fs = ft, flag_coprocesador(1) = 1; si no, flag_coprocesador(1) = 0 c.le.d fs,ft I Si fs <= ft, flag_coprocesador(1) = 1; si no, flag_coprocesador(1) = 0 c.le.s fs,ft I Si fs <= ft, flag_coprocesador(1) = 1; si no, flag_coprocesador(1) = 0 c.lt.d fs,ft I Si fs < ft, flag_coprocesador(1) = 1; si no, flag_coprocesador(1) = 0 c.lt.s fs,ft I Si fs < ft, flag_coprocesador(1) = 1; si no, flag_coprocesador(1) = 0 30 Introducción a los microprocesadores MIPS Formatos de instrucción  MIPS presenta tres formatos básicos de instrucción: Cód. Op. Registro fuente 1 Registro fuente 2 Registro destino xxxxxx rs rt rd shamt funct 6 5 5 5 5 6 31-26 25-21 20-16 15-11 10-6 5-0 Tipo I Cód. Op. Registro base Registro destino Desplazamiento (carga o almacenamiento, ramificación condicional, operaciones con inmediatos) xxxxxx rs rt Offset 6 5 5 16 31-26 25-21 20-16 15-0 Tipo R (shamt: shift amount en instrucciones de desplazamiento) Funct Tipo J Cód. Op. Dirección destino (salto incondicional) xxxxxx target 6 26 31-26 25-0 31