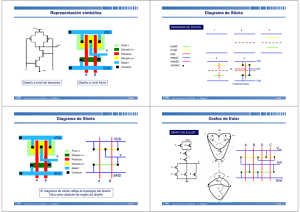

Circuitos secuenciales

Anuncio

Circuitos secuenciales Circuitos secuenciales Los circuitos lógicos secuenciales contienen uno o más bloques lógicos combinacionales junto con elementos de memoria en un camino de realimentación con la lógica. Hay varios puntos importantes: Se necesita tener las señales correlacionadas en el tiempo, I.e., las señales no han de mezclarse (en el tiempo). No importa donde esten las fronteras. De hecho, si el retraso a través de la lógica fuese exáctamente el mismo, no se necesitarían relojes. Los estados se almacenarían en las puertas y las líneas de conexión. Los relojes sirven para enlentecer las señales demasiado rápidas mediante Latches y FlipFlops, que actúan de barreras. Con un latch, la señal no puede propagarse hasta que el nivel del reloj es alto (latch activado a nivel alto) Con un FF, la señal sólo puede propagarse durante el flanco de subida del reloj (FF activado por flanco de subida). Los elementos de memoria son LATCHES o FLIP-FLOPS DMI DMI Circuitos secuenciales – A. Diéguez Circuitos secuenciales Circuitos secuenciales – A. Diéguez Elementos de memoria: Latches El problema es que latches y FFs también enlentecen las señales lentas. Los latches enlentecen la señal en el retraso a través del latch (td-q). Los FFs enlentecen la señal en el tiempo de set-up más el retraso desde la llegada del reloj hasta que se tiene el dato a la salida (tsu + tck-q). El problema más importante es que el reloj controla la carga de los latches/registros y nos es posible garantizar su distribución instantánea DMI Circuitos secuenciales – A. Diéguez DMI Circuitos secuenciales – A. Diéguez Elementos de memoria: Latches Elementos de memoria: Latches Los elementos de memoria en sistemas VLSI son LATCHES o FLIP-FLOPS tipo D D LATCH/FF significa Delay: Un FF D retrasa la señal (dato) un cliclo de reloj El latch más simple tipo D: z Almacena un 1 o un 0 en una capacidad X Interruptor cerrado: la capacidad se carga a la señal de entrada Y Interruptor abierto: la capacidad mantiene el valor El latch estático tipo D: z Utiliza realimentación para almacenar, no una capacidad z Puede recordar mientras se mantenga la alimentación z La capacidad sólo es necesaria para recordar el valor durante la conmutación X CLOCK=‘1’: La señal de entrada pasa a la salida Q (el latch es transparente) Y CLOCK=‘0’: La última entrada determina Q Posible implementación: Posible implementación: z 12 transistores z Hay una degradación del tsetup debido a la puerta de transmisión DMI Circuitos secuenciales – A. Diéguez DMI Circuitos secuenciales – A. Diéguez Elementos de memoria: Latches Elementos de memoria: Latches El inversor C2MOS (Clocked-inverter): z El inversor C2MOS es un híbrido entre una TG y un INV X E flota cuando el reloj φ está bajo Y E invierte la entrada E cuando el reloj φ está alto El MUX D-LATCH z Es simplemente un multiplexor X CLOCK=‘1’: D pasa a Q Y CLOCK=‘0’: Q se mantiene a través del camino de realimentación El latch C2MOS (Clocked-inverter): z 14 transistores X φ=‘1’: G1 está ‘on’, el latch es transparente. La señal D viaja DÆXÆq Y φ =‘0’: G2 está ‘on’. El latch almacena XÆqÆX formando un bucle no inversor z Implementado con puertas tiene 12 transistores + 2 del buffer de salida C y !C tienen retrasos diferentes se produce un glitch z La entrada es buffered: tiempo de setup aislada de la impedancia de salida de la etapa anterior z Si z Layout más z No DMI simple hay puerta de paso a la entrada Circuitos secuenciales – A. Diéguez DMI Circuitos secuenciales – A. Diéguez Elementos de memoria: Latches Elementos de memoria: Latches El MUX D-LATCH: implementación alternativa Alternativas dinámicas: Timming: DMI Circuitos secuenciales – A. Diéguez DMI Circuitos secuenciales – A. Diéguez Elementos de memoria: FlipFlip-Flops Elementos de memoria: FlipFlip-Flops Mayoritariamente basados en estructuras Master-Slave (tipo D en sistemas VLSI) Efectivamente, es edge-triggered (activado por flanco) Implementación: 2 latches D en serie, uno con CLK y el otro con CLK Operación: X MASTER transparente, SLAVE en hold Y MASTER en hold, SLAVE transparente Como siempre hay un latch en modo hold, el FF nunca es transparente. z El dato que entra en D justo antes de la caida del clock, llega a Q tras el flanco de bajada del reloj z Todos los FF D master-slave son activados por flanco, pero no todos los FF D activados por flanco son master-slave Símbolo D-FF: DMI Circuitos secuenciales – A. Diéguez DMI Circuitos secuenciales – A. Diéguez Elementos de memoria: FlipFlip-Flops DMI Circuitos secuenciales – A. Diéguez Elementos de memoria: FlipFlip-Flops DMI Elementos de memoria: FlipFlip-Flops Elementos de memoria: FlipFlip-Flops El Enabled D Flip-Flop z A menudo se necesita mantener un dato varios ciclos de reloj z En ocasiones se necesita eliminar datos indeseados de las entradas z ¿Por qué no desactivar el reloj estas ocasiones? El Enabled D Flip-Flop z Es una forma simple de eliminar el problema de inhabilitar el reloj con puertas z Conmuta la entrada D del flip-flop entre la antigua Q y la nueva entrada Operación: X ENABLE=1: la entrada introducida en el flip-flop Y ENABLE=0: Q se recarga en la entrada desde la salida Poner puertas para inhabilitar el reloj provoca Clock Skew: Aplicación: z El enable permite al flip-flop mantener el dato estable tanto tiempo como se desea sin poner puertas en la entrada del reloj Otras razones para no inhabilitar el reloj con puertas (gating the clock) z Puede causar falsos flancos de reloj si SIT cambia cuando CLK=1 DMI Circuitos secuenciales – A. Diéguez Circuitos secuenciales – A. Diéguez DMI Circuitos secuenciales – A. Diéguez Propiedades temporales de los FFs Propiedades temporales de los FFs Tiempos de setup y de hold z Los FFs tienen regisones restringidas cerca del flanco activo del reloj z Si D cambia en estas regiones, Q es indefinido z Q puede: ser el último valor de D; el nuevo D, tomar un nivel medio (~VDD/2) Señales síncronas y asíncronas z Síncrona: si no cambia en la región restringida z Asíncrona: puede cambiar en cualquier sitio Las señales asíncronas pueden generarse cuando: z Vienen de fuera del CI z Vienen de un circuito controlado por otro reloj z Señales generadas usando el reloj con algo más que latches o flip-flops. Ej: clock gating Los FFs actuales tienen un hold time nulo o negativo. z El dato puede cambiar antes del flanco y ser capturado z El diseño (del sistema) se simplifica DMI Circuitos secuenciales – A. Diéguez DMI Circuitos secuenciales – A. Diéguez Propiedades temporales de los FFs Propiedades temporales de los FFs Tiempo de propagación, tc-q z Es el retraso de un cambio de Q respecto al flanco de reloj activo z Los diseñadores han de hacer tc-q > thold Tiempo de ciclo (periodo) z En un circuito secuencial generalmente hay lógica entre FFs z Existe un periodo mínimo del reloj (o un tiempo máximo de propagación en la lógica) La señal de salida de un FF es siempre síncrona z si tc-q > thold (incluso si D no lo es ya que Q sólo cambia por acción del reloj) z tc-q desplaza los cambios deQ fuera de la región restringida para el siguiente FF (si algo produce un retraso despues del FF no tiene porque cumplirse) z Esta z Si DMI Circuitos secuenciales – A. Diéguez DMI es la principal restricción temporal en circuitos digitales. no se cumple se denomina violación de tiempo de setup Circuitos secuenciales – A. Diéguez Propiedades temporales de los FFs Propiedades temporales de los FFs Tiempo de hold z Existe un tiempo mínimo para la propagación de la lógica: Ocurre si tc-q < thold z Considerad 2 FFs con el mismo reloj. Para un tiempo grande de hold el FF1 puede cambiar de estado y enviar su nueva salida al FF2 de forma que ambos conmuten en el mismo flanco. z Para Tiempo de hold, visión alternativa z El mínimo retraso aparece cuando tc-q < thold z En este caso D1 puede provocar Q1 en el FF1 y viajar a través de la lógica y alcanzar el FF2 dentro de su tiempo de hold. El FF2 puede, por tanto, cambiar en el mismo flanco. evitar dobles conmutaciones: z Dicho de otra forma, el mínimo tiempo de propagación en la logica es: z Los z Si DMI prolemas de hold pueden solucionarse insertando un par de inversores en la lógica no se cumple se denomina violación de tiempo de hold. Máximo peligro en shift Regs. DMI Circuitos secuenciales – A. Diéguez Circuitos secuenciales – A. Diéguez Incertidumbre en el reloj Clock skew Clock skew z Cuando el flanco del reloj no alcanza a todos los FFs al mismo tiempo 4 Power Supply 3 Interconnect Devices 2 5 Temperature 6 Capacitive Load 7 Coupling to Adjacent Lines 1 Clock Generation Skew positivo z Los datos y el reloj se retrasan en la misma dirección. Skew negativo z Los datos y el reloj se retrasan en direcciones opuestas Retardo en una conexión del reloj DMI Circuitos secuenciales – A. Diéguez DMI Circuitos secuenciales – A. Diéguez Clock skew Clock skew Efecto del skew en el máximo tiempo de propagación skew positivo incrementa el periodo efectivo del reloj (hay más tiempo para alcanzar FF2) z El skew positivo incrementa tPD(MAX) en el skew Efecto del skew en el mínimo tiempo de propagación skew positivo equivale a aumentar el tiempo de hold del FF2 z El mínimo retraso de la lógica, tPD(MIN), necesario para evitar la región restringida aumenta z El DMI z El DMI Circuitos secuenciales – A. Diéguez Circuitos secuenciales – A. Diéguez Clock skew DMI Circuitos secuenciales – A. Diéguez Clock skew DMI Circuitos secuenciales – A. Diéguez Distribución del reloj Distribución del reloj CLK Distribución de arbol en H DMI Esquema de buffers distribuidos en áreas locales DMI Circuitos secuenciales – A. Diéguez Esquema del reloj en un sistema de dos fases Ejemplos de redes de distribución DEC Alpha 21164 300 MHz Circuitos secuenciales – A. Diéguez Con dos fases no solapadas, flancos distintos guardan los datos y modifican la salida EV6 (Alpha 21264) 600 MHz – 0.35 micron CMOS Generación: 100 Clk Phase 1 Phase 2 DMI Circuitos secuenciales – A. Diéguez DMI Circuitos secuenciales – A. Diéguez