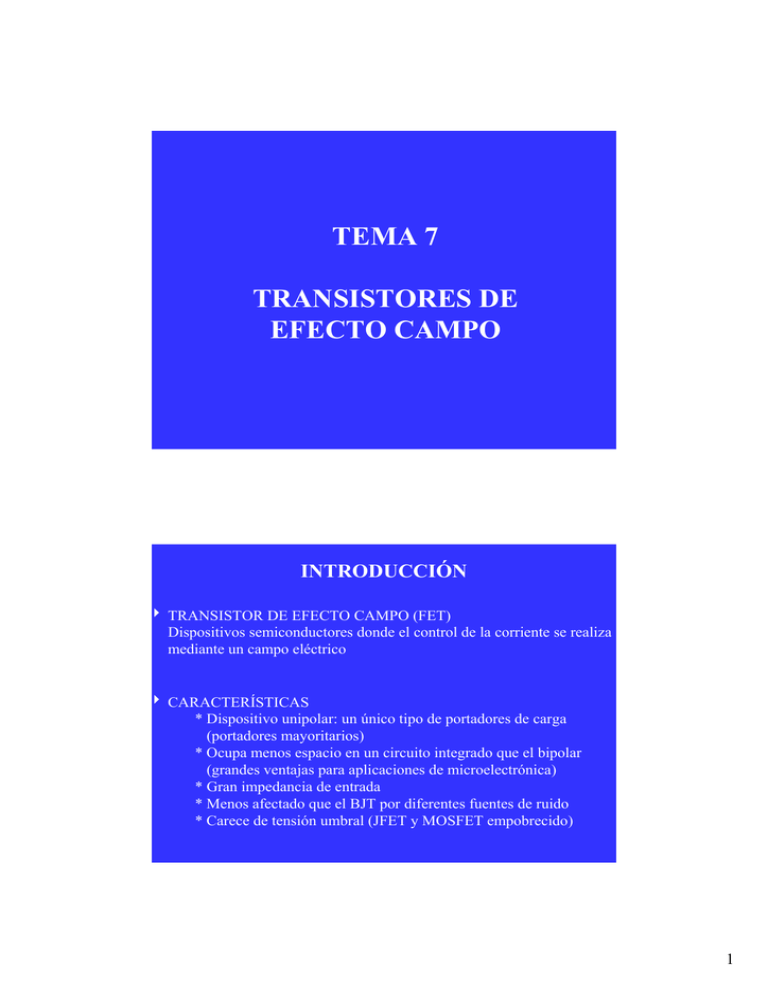

TEMA 7 TRANSISTORES DE EFECTO CAMPO

Anuncio

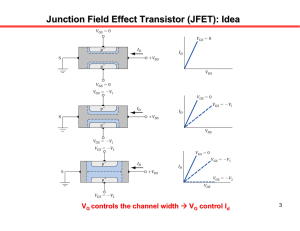

TEMA 7 TRANSISTORES DE EFECTO CAMPO INTRODUCCIÓN 4 TRANSISTOR DE EFECTO CAMPO (FET) Dispositivos semiconductores donde el control de la corriente se realiza mediante un campo eléctrico 4 CARACTERÍSTICAS * Dispositivo unipolar: un único tipo de portadores de carga (portadores mayoritarios) * Ocupa menos espacio en un circuito integrado que el bipolar (grandes ventajas para aplicaciones de microelectrónica) * Gran impedancia de entrada * Menos afectado que el BJT por diferentes fuentes de ruido * Carece de tensión umbral (JFET y MOSFET empobrecido) 1 4 TIPOS DE TRANSISTORES DE EFECTO CAMPO * De unión: JFET (Junction Field Effect Transistor) o FET * De puerta aislada: IGFET (Insulated Gate Field Effect Transistor) MOS (Metal Oxide Semiconductor) MOST MOSFET ESTRUCTURA DE LOS JFET * Barra semiconductora con contactos óhmicos en los extremos * JFET puede ser de canal N o canal P * Puerta muy impurificada con portadores distintos a los de la barra * Elementos: Fuente o surtidor (S) -> por donde entran los portadores Drenador (D) - > por donde salen los portadores Puerta (G) -> elemento de control Canal -> región situada entre las dos difusiones de puerta * La tensión puerta fuente (VGS) polariza inversamente las uniones 2 La corriente entre drenador y fuente se controla mediante el campo creado por la polarización inversa aplicada a la puerta. Cualquiera de los extremos se puede usar como fuente SÍMBOLOGÍA DE LOS JFET D G D G S Canal N S Canal P 3 ESQUEMA BÁSICO DE POLARIZACIÓN + IG ID + VGG VDS IS VDD VGS _ _ Para el canal P el esquema es idéntico pero con polaridades invertidas CANAL N VGS negativa VDS positiva ID positiva CANAL P VGS positiva VDS negativa ID negativa CURVA CARACTERÍSTICA ID = f(VDS, VGS) 4 4 PARA VGS = 0: * VDS pequeña (<VP): Canal casi completamente abierto. Resistencia pequeña y aproximadamente constante. Comportamiento lineal. => REGIÓN ÓHMICA * VDS cercana a VP: Canal se va cerrando por un punto y la resistencia aumenta con la tensión. Comportamiento no lineal. => REGIÓN DE CONTRACCIÓN * VDS > VP: La resistencia rds es grande y aproximadamente constante. No se puede cerrar completamente el canal porque dejaría de circular corriente y desaparecería la tensión inversa en la unión puerta-canal. JFET se comporta como fuente de corriente. => REGIÓN DE SATURACIÓN * VDS muy elevada (VDS ≥ BVDS): Conducción inversa en las uniones puerta-canal, lo que supone un aumento muy grande de la ID que produce la destrucción del JFET. => REGIÓN DE RUPTURA ZONAS DE FUNCIONAMIENTO ID ÓHMICA: |VDS| < ||Vp| - |VGS|| CONTRACCIÓN: |VDS| ≈ ||Vp| - |VGS|| SATURACIÓN: |VDS| > ||Vp| - |VGS|| VGS = 0 RUPTURA: VDS elevada |VGS|= |Vp| VDS CORTE: |VGS| > |Vp| 5 4 REGIÓN ÓHMICA (Valores pequeños de VDS: |VDS| < | |VP| - |VGS| |) * Resistencia óhmica: Canal N => rds = 1 L 1 L = σ 2 ⋅ a ⋅ w q ⋅ N D ⋅ µn 2 ⋅ a ⋅ w * Valores usuales de la resistencia entre 100 Ω y 100 KΩ rds > Rcesat (transistor bipolar) * Cada VGS define un valor de resistencia distinto * ID = f (VDS) -> función lineal. 4 REGIÓN DE CONTRACCIÓN (|VDS| ≈ | |VP| - |VGS| |) * Al elevar VDS, ID deja de crecer linealmente => se entra en la zona de contracción => se alcanza la anchura mínima del canal (δ) * Al aumentar más VDS, el canal no se estrecha más (δ permanece constante) y aumenta la longitud de la zona de estrechamiento máximo => se entra en la zona de saturación 4 REGIÓN DE SATURACIÓN (|VDS| > | |VP| - |VGS| |) 6 4 REGIÓN DE SATURACIÓN (|VDS| > | |VP| - |VGS| |) La anchura mínima del canal es δ. Al aumentar la tensión entre drenador y fuente, δ permanece constante y aumenta L’ y se entra en la zona de saturación. IDS : Corriente de drenador en saturación 2 ⎛ |V | ⎞ I DS = I DSS ⎜⎜1 − GS ⎟⎟ | VP | ⎠ ⎝ I DS IDSS: Corriente de drenador en saturación para VGS = 0 ⎛ |V | ⎞ = I DSS ⎜⎜1 − GS ⎟⎟ | VP | ⎠ ⎝ 2 IDS CANAL N IDSS Vp Vp IDSS VGS CANAL P 7 4 REGIÓN DE CORTE (|VGS| ≥ |VP|) |VGS| ≥ |VP| => El canal desaparece => IDS ≈ 0 G Región de deplexión S D G 4 REGIÓN DE RUPTURA (|VDS| ≥ BVDS) Cuando la tensión drenador fuente es muy grande, la corriente de drenador se eleva mucho y se llega a la destrucción del FET 8 CÁLCULO DE LA TENSIÓN DE CONTRACCIÓN (VP) N A >> N D ⇒ Wn ≈ W >> W p q ⋅ N D ⋅ w2 V j = V0 + VI = 2ε Demostrado cuando se calculó la capacidad de transición del diodo w( x ) = a − b ( x ) = w( x ) = a − b ( x ) = 2ε (Vo + V ( x ) ) q ⋅ ND 2ε (Vo + V ( x ) ) q ⋅ ND Si b = δ ≈ 0 (estrangulamiento máximo) y Vo << V(x), entonces: a= 2ε q ⋅ ND 2 Vp ⇒ Vp = a q ⋅ ND 2ε Vp es la VDS que provoca el estrangulamiento o estrechez máxima en un punto para VGS=0 Vp es la VGS que corta completamente el canal Si VDD = 0 => ID = 0 => Vo + V(x) = |VGS| independientemente de x 2ε 2ε ⎛ b⎞ 2 VGS ⇒ (a − b ) = VGS ⇒ VGS = ⎜1 − ⎟ V p q ⋅ ND q ⋅ ND ⎝ a⎠ 2 a−b = 9 EL TRANSISTOR MOS MOS: Metal Oxide Semiconductor Los transistores de efecto campo de puerta aislada de acumulación tienen la característica de presentar una ID nula con VGS = 0, lo cual es interesante para trabajar en conmutación. Estos transistores tienen una impedancia de entrada elevada, del orden de 1010 a 1015 Ω Canal P (sustrato N impur. P+) de enriquecimiento o acumulación Canal N (sustrato P impur. N+) MOS Canal P (sustrato N impur. P+) de empobrecimiento o de deplexión Canal N (sustrato P impur. N+) ESTRUCTURA DE UN MOSFET DE ACUMULACIÓN DE CANAL P 10 ESTRUCUTRA DE UN MOSFET DE DEPLEXIÓN DE CANAL N MOS DE ACUMULACIÓN ID = f(VDS, VGS) Región de no saturación u óhmica: |VDS| < |VGS - VTH| |ID| Región de contracción: |VDS| ≈ |VGS - VTH| Región de saturación: |VDS| > |VGS - VTH| |VGS| |VDS| |BV| Región de corte: |VGS| < |VTH| Tensión de ruptura 11 4 CURVAS CARACTERÍSTICAS EN SATURACIÓN Transistores enriquecidos CANAL N CANAL P ID V TH ID VGS VGS VTH I D = K (VGS − VTH ) para VGS > VTH mA K = 0,3 2 Valor típico V 2 Transistores empobrecidos CANAL P CANAL N ID ID Vp Deplexión VGS Acumulación IDSS IDSS VGS ⎛ V I D = I DSS ⎜⎜1 − GS VP ⎝ -Vp ⎞ ⎟ ⎟ ⎠ 2 4 SÍMBOLOS GRÁFICOS C anal P C anal N D G S D D E M P O B R E C ID O S O D E D E P L E X IÓ N ( D E P L E T IO N ) G S D E N R IQ U E C ID O S O G D E A C U M U L A C IÓ N S (E N H A C E M E N T ) O tr o tip o d e s ím b o l o : G S D D D E P L E X IÓ N G G S S D D A C U M U L A C IÓ N G G S S E n e le c tr ó n ic a d ig ita l: D G D A C U M U L A C IÓ N G S S 12 EL MOS EN CONMUTACIÓN ID +VDD VGS = VDD RL B + V’’’GS > V’’GS D G + Vent Vsal V’’GS > V’GS S _ _ V’GS > VTH VGS = VTH ≈0 Vent 0 +VDD Vsal Vent Vsal +VDD “0” “1” ≈0 “1” “0” En lógica digital VDS A +VDD 13