Tecnologías de C. I.

Anuncio

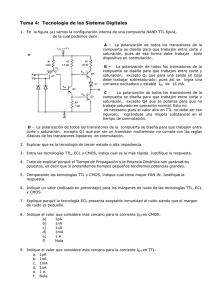

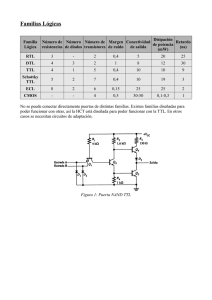

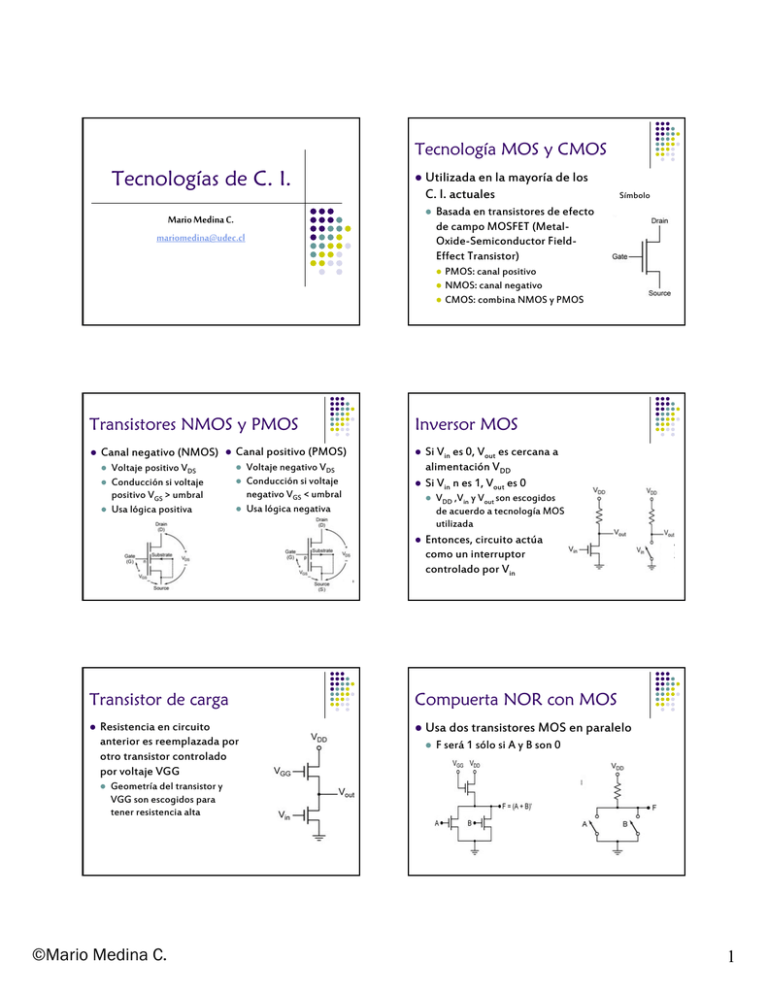

Tecnología MOS y CMOS Tecnologías de C. I. Utilizada en la mayoría de los C. I. actuales Mario Medina C. [email protected] Símbolo Basada en transistores de efecto de campo MOSFET (MetalOxide-Semiconductor FieldEffect Transistor) PMOS: canal positivo NMOS: canal negativo CMOS: combina NMOS y PMOS Transistores NMOS y PMOS Canal negativo (NMOS) Voltaje positivo VDS Conducción si voltaje positivo VGS > umbral Usa lógica positiva Canal positivo (PMOS) Voltaje negativo VDS Conducción si voltaje negativo VGS < umbral Usa lógica negativa Inversor MOS Transistor de carga Resistencia en circuito anterior es reemplazada por otro transistor controlado por voltaje VGG Si Vin es 0, Vout es cercana a alimentación VDD Si Vin n es 1, Vout es 0 VDD ,Vin y Vout son escogidos de acuerdo a tecnología MOS utilizada Entonces, circuito actúa como un interruptor controlado por Vin Compuerta NOR con MOS Usa dos transistores MOS en paralelo F será 1 sólo si A y B son 0 Geometría del transistor y VGG son escogidos para tener resistencia alta ©Mario Medina C. 1 Compuerta NAND con MOS Usa dos transistores MOS en serie F será 1 si A ó B son 0 Compuerta EXOR con MOS Usa 4 transistores MOS F será 0 si AB es 1 ó si A’B’es 1 Inversor CMOS F’ = AB + A’B’, es decir, F = AB’ + A’B Inversor CMOS CMOS: Complementary Metal-Oxide Semiconductor Utiliza transistores PMOS y NMOS Si Vin es 0, Q1 conduce y Q2 no conduce Si Vin es 1, Q1 no conduce y Q2 conduce Bajo consumo de potencia Sólo durante transiciones de estado Elimina transistor de carga Compuerta NAND CMOS Entrada Gate activa baja indica transistor PMOS ©Mario Medina C. Compuerta NOR CMOS Ejercicio: verificar operación de la compuerta mediante una tabla de verdad 2 Características eléctricas de familia TTL Fabricante especifica valores de voltaje reconocidos como 0 ó 1 lógico para señales de entrada y salida Capacidad de Carga (Fan-Out) Corrientes máximas de entrada y salida Número máximo de compuertas que pueden ser conectadas a la salida de una compuerta sin superar la capacidad de corriente de ésta. Compuertas TTL 54/74 están diseñadas para un Fanout de 10, es decir, pueden manejar adecuadamente 10 cargas típicas TTL Todo dispositivo que se conecta a la salida de otro inyecta o extrae corriente al primero IOH = Corriente de salida en alto (-400 A máximo) IOL = Corriente de salida en bajo (16 mA máximo) Voltaje entre los rangos dados no es reconocido como un estado lógico definido Características eléctricas de familia TTL Características eléctricas de familia TTL IIH IIL = Corriente de entrada en alto (40 A máximo) = Corriente de entrada en bajo (-1.6 mA máximo) Características eléctricas de familia TTL Manejo de Entradas Abiertas y No Usadas En TTL, entradas abiertas (no usadas) actúan como un 1 lógico Susceptibles a ruido Resistencias de Pull-Up y Pull-Down Compuerta en 0 puede alimentar a 10 compuertas TTL sin que VOL sea mayor que 0.4 V Compuerta en 1 puede alimentar a 10 compuertas TTL sin que VOH sea menor de 2.4 V ©Mario Medina C. 3