P2 - Departamento de Informática Aplicada

Anuncio

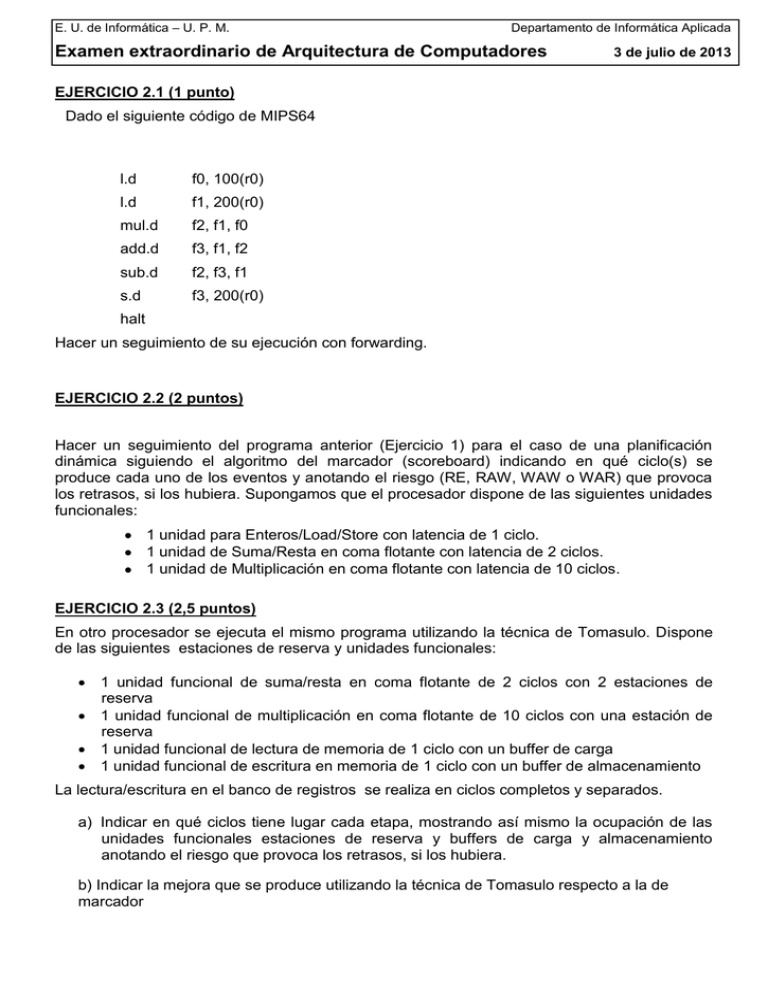

E. U. de Informática – U. P. M. Departamento de Informática Aplicada Examen extraordinario de Arquitectura de Computadores 3 de julio de 2013 EJERCICIO 2.1 (1 punto) Dado el siguiente código de MIPS64 l.d f0, 100(r0) l.d f1, 200(r0) mul.d f2, f1, f0 add.d f3, f1, f2 sub.d f2, f3, f1 s.d f3, 200(r0) halt Hacer un seguimiento de su ejecución con forwarding. EJERCICIO 2.2 (2 puntos) Hacer un seguimiento del programa anterior (Ejercicio 1) para el caso de una planificación dinámica siguiendo el algoritmo del marcador (scoreboard) indicando en qué ciclo(s) se produce cada uno de los eventos y anotando el riesgo (RE, RAW, WAW o WAR) que provoca los retrasos, si los hubiera. Supongamos que el procesador dispone de las siguientes unidades funcionales: 1 unidad para Enteros/Load/Store con latencia de 1 ciclo. 1 unidad de Suma/Resta en coma flotante con latencia de 2 ciclos. 1 unidad de Multiplicación en coma flotante con latencia de 10 ciclos. EJERCICIO 2.3 (2,5 puntos) En otro procesador se ejecuta el mismo programa utilizando la técnica de Tomasulo. Dispone de las siguientes estaciones de reserva y unidades funcionales: 1 unidad funcional de suma/resta en coma flotante de 2 ciclos con 2 estaciones de reserva 1 unidad funcional de multiplicación en coma flotante de 10 ciclos con una estación de reserva 1 unidad funcional de lectura de memoria de 1 ciclo con un buffer de carga 1 unidad funcional de escritura en memoria de 1 ciclo con un buffer de almacenamiento La lectura/escritura en el banco de registros se realiza en ciclos completos y separados. a) Indicar en qué ciclos tiene lugar cada etapa, mostrando así mismo la ocupación de las unidades funcionales estaciones de reserva y buffers de carga y almacenamiento anotando el riesgo que provoca los retrasos, si los hubiera. b) Indicar la mejora que se produce utilizando la técnica de Tomasulo respecto a la de marcador E. U. de Informática – U. P. M. Departamento de Informática Aplicada Examen extraordinario de Arquitectura de Computadores 3 de julio de 2013 Apellidos ...................................................................................................................................... Nombre .............................................................................. Nº matrícula..................................... EJERCICIO 2.1 (1 pto) Realizar un seguimiento de la ejecución del pipeline utilizando adelantamientos o forwarding cuando sea posible. 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 F D E M W l.d f1,200(r0) F D E M W l.d f0,100(r0) mul.d f2,f1,f0 add.d f3,f1,f2 sub.d f2,f3,f1 s.d halt f3,200(r0) F D D E E E E E E E M W F F D D D D D D D E E E E M W F F F F F F F D D D D E E E E M W F F F F D D D D E M W F F F F D E M W Nota: La ejecución de la suma/resta supondremos que tarda 4 ciclos y el producto 7 ciclos E. U. de Informática – U. P. M. Departamento de Informática Aplicada Examen extraordinario de Arquitectura de Computadores 3 de julio de 2013 Apellidos ...................................................................................................................................... Nombre ............................................................................. Nº matrícula .................................... EJERCICIO 2.2 (2 ptos) Hacer un seguimiento del programa anterior (Ejercicio 1) para el caso de una planificación dinámica siguiendo el algoritmo del marcador (scoreboard) indicando en qué ciclo(s) se produce cada uno de los eventos y anotando el riesgo (RE, RAW, WAW o WAR) que provoca los retrasos, si los hubiera. Supongamos que el procesador dispone de las siguientes unidades funcionales: 1 unidad para Enteros/Load/Store con latencia de 1 ciclo. 1 unidad de Suma/Resta en coma flotante con latencia de 2 ciclos. 1 unidades de Multiplicación en coma flotante con latencia de 10 ciclos. Instrucción Emisión Lectura Ejecución Escritura l.d f0,100(r0) l.d f1,200(r0) 1 4 (RE) 5 6 19 (WAW) 20 2 5 7 (RAW) 18 (RAW) 21 (RAW) 21 3 6 8-17 19-20 22-23 22 4 7 18 21 24 - mul.d f2,f1,f0 add.d f3,f1,f2 sub.d f2,f3,f1 s.d f3,200(r0) E. U. de Informática – U. P. M. Departamento de Informática Aplicada Examen extraordinario de Arquitectura de Computadores 3 de julio de 2013 Apellidos ...................................................................................................................................... Nombre ............................................................................. Nº matrícula .................................... EJERCICIO 2.3 (2,5 ptos) En otro procesador se ejecuta el mismo programa utilizando la técnica de Tomasulo. Dispone de las siguientes estaciones de reserva y unidades funcionales: 1 unidad funcional de suma/resta de 2 ciclos con 2 estaciones de reserva 1 unidad funcional de división/multiplicación de 10 ciclos con una estación de reserva 1 unidad funcional de lectura de memoria de 1 ciclos con un buffer de carga 1 unidad funcional de escritura en memoria de 1 ciclos con un buffer de almacenamiento La lectura/escritura en el banco de registros se realiza en ciclos completos y separados. a) Indicar en qué ciclos tiene lugar cada etapa, mostrando así mismo la ocupación de las unidades funcionales estaciones de reserva y buffers de carga y almacenamiento anotando el riesgo que provoca los retrasos, si los hubiera. Instrucción l.d f0,100(r0) l.d f1,200(r0) mul.d f2,f1,f0 add.d f3,f1,f2 sub.d f2,f3,f1 s.d f3,200(r0) Emisión Ejecución/Mem Escritura 1 2 3 4 5 6 2 3 5-14 (RAW) 16-17 (RAW) 19-20 (RAW) 22 (RAW) 3 4 15 18 21 - Unidades funcionales y de acceso a memoria, con sus correspondientes estaciones de reserva y buffers de carga y almacenamiento. ER1 ER2 UF +- ER1 UF Mult/Div 3-4 5-14 5-18 16-17 19-20 4-15 Buffer de carga Lectura de memoria Buffer de almacenamiento Escritura en memoria 1 2 2 3 6-21 22 b) Indicar la mejora que se produce utilizando la técnica de Tomasulo respecto a la de marcador 24/21= 1,1414%