TEMA 3 NOTA: Salvo que se indique lo contrario, se entiende que

Anuncio

Problemas de CIRCUITOS INTEGRADOS

3o Ing. Telecomunicación.

Curso 2006-2007.

Tema 3-1

TEMA 3

NOTA: Salvo que se indique lo contrario, se entiende que todas las tensiones deben estar comprendidas entre la tensión más negativa del chip (VSS = -1.65v) y la más positiva

(VDD = +1.65v). Las flechas hacia arriba indican VDD, y las flechas hacia abajo VSS.

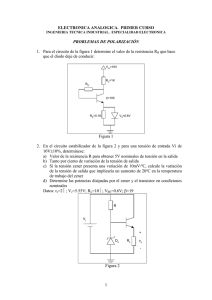

1: Para el circuito de la figura, obtenga expresiones

Iin

y represente la intensidad Iin frente a la tensión

Vin cuando esta última varía entre VSS y VDD.

Vin

W/L = 1, L = 1µm.

2: Repita el problema anterior empleando la variante complementaria del circuito.

3: Tomando transistores de geometrías mínimas, uno de canal n y otro de canal p, obtenga

primero la corriente máxima, y después, en el punto de operación de corriente máxima,

calcule los valores de todos los parámetros del modelo de pequeña señal a frecuencias

intermedias.

4: Considere un transistor pmos con aspecto geométrico S = 1 y con longitud L = 3µm. El

terminal de sustrato está conectado a VB = VDD =1.65v, el terminal de fuente a VS = 1.35v,

el de puerta a VG = 0v, y el drenador a VD = VSS = −1.65v. Calcule el valor de la intensidad

del transistor y el de todos los parámetros del modelo de pequeña señal (en DC y en AC).

5: Para un transistor nmos con longitud igual al triple de la mínima, y aspecto geométrico

igual a 1, dibuje las curvas de gran señal de la intensidad frente a VDS con VGS como

parámetro y con VSB = 0, y de la intensidad frente a VGS con VDS como parámetro con

VSB = 0. Emplee al menos cuatro valores distintos de la variable empleada como parámetro

(es decir, al menos cuatro curvas en cada caso), y calcule el valor de la intensidad en al

menos un par de puntos en cada región de operación del transistor en cada una de las curvas

resultantes.

6: Repita el problema anterior para un transistor pmos, empleando la notación habitual.

7: Explique, obtenga expresiones I = f(V), y dibuje las características I frente a V de cada uno

de los siguientes resistores no lineales, con V en el rango (VSS,VDD). Cuando sea necesario

considere diferentes tramos en las curvas, indicando las expresiones de cada uno y los

valores de los puntos extremos. Preste atención al signo de la intensidad según la definición

hecha.

VDD

I(V)

a)

b)

VDD−1v

c)

VDD−1v

d)

e)

f)

j)

k)

l)

VSS

V

VSS+1v

VSS+1v

g)

h)

i)

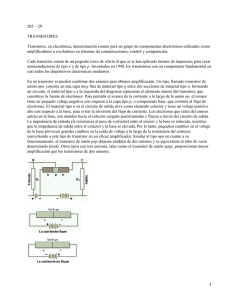

8: La figura muestra dos transistores pmos conectados “en serie”. Encuentre

la zona de operación de los dos transistores en función de VD y VG.

Desprecie el efecto sustrato y el efecto de modulación de la longitud de

V

canal. Se sugieren los siguientes pasos: demuestre primero que no puede G

estar un transistor en “on” y el otro en “off”, y después demuestre que uno

de los transistores no puede estar nunca saturado,

Departamento de Electrónica y Electromagnetismo. Escuela Superior de Ingenieros.

M1

M2

VD

Universidad de Sevilla.

Problemas de CIRCUITOS INTEGRADOS

3o Ing. Telecomunicación.

Curso 2006-2007.

Tema 3-2

9: Demuestre que las siguientes asociaciones de transistores pueden representarse

correctamente en gran señal en DC mediante un único transistor equivalente con la βeq que

se muestra en cada caso. Desprecie el efecto sustrato y el efecto de modulación de la

longitud de canal. Para el caso de asociación “en serie”, emplee los resultados del problema

anterior, y en las combinaciones de regiones de operación posibles, calcule la intensidad y

compárela con la de un único transistor.

VD

IDSeq

VD

Asociación “en paralelo”

β eq = β 1 + β 2

VG

β1

IDSeq

Asociación “en serie”

β2

VA

VG

β1 ⋅ β2

β eq = ----------------β1 + β2

β1

β2

VS

VS

10: La figura muestra dos casos

Mp

Mn

concretos de resistor no

I

I

VDD

lineal. Calcule expresiones y

V

V

dibuje las características I-V

VSS

de cada caso, con V en el

M

M

p

n

a)

b)

rango (VSS,VDD).

11: Para un transistor pmos con VBS = 0, represente la intensidad ISD, la transconductancia de

puerta gm, la conductancia de canal gsd, y el cociente gm/gsd, frente a VSG con VSD como

parámetro, y frente a VSD con VSG como parámetro. Utilice para ello el modelo de nivel 1

empleado normalmente para análisis a mano. Comente sobre las limitaciones de precisión,

dónde ocurren, y de qué tipo son.

12: Para un transistor nmos con VSB = 0 y con intensidad fijada IQ, represente gm, gds, y el

cociente gm/gds frente a VGS con W/L como parámetro. Repita las representaciones frente

a VDS, tomando de nuevo W/L como parámetro. Utilice para ello un modelo de nivel 1, y

comente las posibles discontinuidades y regiones de las curvas en las cuales el modelado

no sea correcto debido a limitaciones del modelo. Teniendo la intensidad fijada, ¿Cuál es

la zona de operación de máxima transconductancia? ¿Y la de máxima ganancia en tensión?

Nota: al barrer la variable independiente (VGS ó VDS) con VSB, IQ, y W/L fijadas, dejamos

que varíe la variable dependiente (VDS ó VGS, respec.). Preste atención a la existencia de

zonas de las curvas en las que el valor de la variable dependiente pueda ser irrealista, y

comente.

13: Repita el problema anterior para un transistor pmos, con la notación complementaria

habitual.

14: Considere un transistor pmos con W = 20µm, L = 2µm. Para cada uno de los puntos de

operación indicados en la tabla, calcule la intensidad de gran señal y los valores de todos

los elementos del modelo de pequeña señal. Procure aprovechar las similitudes entre casos

para ahorrar cálculos. Resuma los resultados en forma de tabla como se indica.

P.O.

A

Vs

(V)

Vd

(V)

Vg

(V)

Vb

(V)

1.65

0.00

1.35

1.65

B

1.65

0.00

0.55

1.65

C

1.65

0.00 -1.00

1.65

D

1.35 -0.35 -1.35

1.65

E

1.65 -1.00

1.65

0.55

Isd

(µA)

gm

gsd

gmb

(µA/V) (µA/V) (µA/V)

cgs

(fF)

cgd

(fF)

Departamento de Electrónica y Electromagnetismo. Escuela Superior de Ingenieros.

cgb

(fF)

csb

(fF)

cdb

(fF)

Universidad de Sevilla.

Problemas de CIRCUITOS INTEGRADOS

3o Ing. Telecomunicación.

Curso 2006-2007.

Tema 3-3

15: La figura muestra el “layout” de un transistor MOS, y una representación esquemática del

mismo en un punto de operación determinado. Obtenga los valores de gran señal del punto

de operación, dibuje el modelo de pequeña señal completo (incluyendo parásitos

capacitivos) y obtenga los valores de todos los elementos que aparecen en él.

0.5µm

sustrato pzona activa

polisilicio

implantación n+

2.4v

1.0v

2.0v

implantación p+

metal 1

0.5µm

contacto

16: Calcule todos los parásitos capacitivos de un inversor, a partir de su layout, en el punto de

operación quiescente (Vi=Vo). Previamente, dimensione los transistores para que ese

punto se corresponda con el centro del rango de polarización. Utilice geometrías mínimas

siempre que sea posible.

17: La figura muestra un inversor CMOS convencional. Calcule el

Mp

valor VQ de tensión a la entrada para el cual la tensión de salida

3.0/0.5

y la de entrada son iguales. A continuación, considere el

Vo

siguiente conjunto de valores para la tensión de entrada: {VSS, Vi

(VSS+VQ)/2, VQ, (VDD+VQ)/2, VDD}. Construya una tabla en

CL

Mn

la que cada columna corresponda a la situación de DC (punto de

3pF

1.0/0.5

operación) correspondiente a la aplicación de cada uno de estos

valores de Vi. En filas consecutivas vaya indicando las

siguientes características o valores, para cada columna (indique las unidades empleadas en

una columna adicional): la región de operación de cada transistor, el valor de la tensión de

salida Vo, el valor de la intensidad que circula por los transistores IB, y los valores de todos

los elementos del modelo de pequeña señal de los dos transistores, es decir, los valores de

gmp, gsdp y gmbp, los valores de gmn, gsdn y gmbn, los valores de Cgsp, Cgdp, Csbp, Cdbp y

Cgbp, y los valores de Cgsn, Cgdn, Csbn, Cdbn y Cgbn. NOTAS: debe planificarse bien para

no repetir cálculos innecesariamente (ciertos resultados intermedios son muy útiles). Debe

indicar las expresiones empleadas en los cálculos. Las áreas y perímetros de las regiones

de difusión debe estimarlas en la forma habitual: en base a la mínima “anchura” de una

región de difusión contactada (MDW).

18: La figura muestra un inversor CMOS típico, al cual se le fijan

Mp

tanto el valor de tensión a la entrada como a la salida, usando

Iout

sendas fuentes de tensión. Las longitudes de ambos transistores

y la anchura del nmos son las mínimas permitidas por la

tecnología. La anchura del pmos es la necesaria para hacer que Vin

Vout

Mn

el umbral del inversor se encuentre en el centro del rango de

polarización, es decir, en 0v. A este valor (0v) fijamos la tensión

de entrada Vin. Consideramos tres puntos de operación diferentes, definidos por tres valores

Departamento de Electrónica y Electromagnetismo. Escuela Superior de Ingenieros.

Universidad de Sevilla.

Problemas de CIRCUITOS INTEGRADOS

3o Ing. Telecomunicación.

Curso 2006-2007.

Tema 3-4

diferentes de la tensión de salida Vout: a) Vout = VSS+0.3v, b) Vout = 0v, c) Vout = VDD 0.3v. Para cada uno de los puntos de operación, calcule las intensidades de gran señal de

todos los dispositivos (transistores y fuentes de tensión), y todos los parámetros de pequeña

señal a frecuencias bajas y medias de ambos transistores.

19: Dibujar cualitativamente la forma de VC(t) cuando VG conmuta de

VG

VSS a VDD, en los siguientes casos:

a) VA = VSS, VC(0) = VDD

VA

VC

b) VA = VDD, VC(0) = VSS

Sobre la forma de onda, indicar la región de operación del transistor

durante la evolución temporal, y dar expresiones (implícitas o explícitas) para las curvas dentro de cada región de operación, para los puntos de transición entre

regiones, y para los valores finales de VC. Considerar un modelo de primer orden para el

transistor, con transición directa entre inversión fuerte y corte. Indicar sobre las curvas la

zona en la que el transistor operaría en inversión débil o moderada durante la evolución si

considerásemos la existencia de estas regiones.

20: Calcule una expresión general para la frecuencia de transición de transistores de canal n y

de canal p, definida como la frecuencia a la que la magnitud de la ganancia en intensidad

en configuración de fuente común es igual a uno (se entiende que el transistor está en

saturación). Observe la dependencia con las geometrías y con el punto de polarización.

Determine las condiciones para maximizar dichas frecuencias, y calcule los valores

máximos correspondientes.

21: Dado un transistor nmos con una anchura W=5µm, calcule los valores máximo y mínimo

de las capacidades de sus regiones de difusión cuando las tensiones de los terminales varían

dentro del rango de polarización. Si apróximásemos el valor de la capacidad por su valor a

VR = 0, ¿cuál sería el máximo error relativo cometido?. Repita para un transistor pmos.

22: Considérese el circuito de la figura. El transistor tiene longitud mínima y el resto de las

geometrías que se indican. Obtener expresiones implícitas para las tensiones a la entrada y

a la salida del inversor, en función del tiempo. Utilice el modelo ideal del inversor y la

forma de VG que se muestran. ¿Cuál sería el efecto de la temperatura en el resultado?. No

considere el efecto sustrato ni el de modulación de la longitud de canal. El inversor tiene

su umbral en el centro del rango de polarización, y su impendancia de entrada es infinita

(Iin = 0). Desprecie la capacidad de entrada del inversor. Antes de la bajada de la tensión

de control de la llave, la entrada del inversor quedará fijada a la máxima tensión de paso de

la llave nmos.

1.5µm

VG(t)

VDD

VG(t)

t=0

1.5µm

Vo

VSS

Vo(t)

Vi

Vo

1.5µm

VDD

Vi

Polisilicio

Area Activa n+

23: Discutir procedimientos para obtener, a partir de resultados experimentales o de simulación

eléctrica con modelos precisos, los valores de los parámetros del modelo de nivel 1 para

diseño a mano.

Departamento de Electrónica y Electromagnetismo. Escuela Superior de Ingenieros.

Universidad de Sevilla.