Los Registros SFR del Banco 0

Anuncio

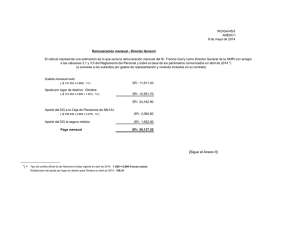

TEMA 5 LA MEMORIA DE DATOS MEMORIA RAM D.P.E. DESARROLLO DE PROYECTOS 1 Estructura De La Memoria Ram (1) La memoria de datos RAM está dividida en dos partes diferenciadas: 1.- Zona SFR o zona de Registros de Funciones eSpeciales 2.- Zona de Registros de Propósito General o zona GPR Ambas partes están organizadas en dos bancos de registros de 128 bytes cada uno aunque solo los primeros 80 bytes se encuentran implementados. Todos los registros tienen un tamaño de 1 byte D.P.E. DESARROLLO DE PROYECTOS 2 Estructura De La Memoria Ram (2) Los Bancos De Registros ¾ En la fig. podemos observar la disposición de los dos bancos de memoria, el primero va desde la dirección 0h hasta la 7Fh, mientras que le segundo lo hace desde la 80h hasta FFh. ¾ Dentro de cada uno de los bancos, y en las posiciones mas bajas se encuentran los SFR, en el banco 0, desde la dirección 0h hasta la 0Bh, y en el banco 1 desde la 80h hasta 8Bh. Estructura De La Memoria Ram (3) Los Bancos De Registros ¾ Como se puede verificar, la zona SFR posee un total de 24 registros, aunque dos no son accesibles (dir 07h y 87h), y algunos se encuentran duplicados en ambos bancos. ¾ La zona de GPR implementada dentro del banco 0 va desde 0Ch hasta 4Fh, que hace un total de 68 registros, ¾ La zona GPR del banco 1 está mapeada sobre el banco 0 por lo que , cuando se apunta a un registro general de este banco, se accede al mismo registro pero del banco 0. ¾ Para seleccionar el banco activo hay que programar el bit RP0 del registro de STATUS. RP0 = 0 ⇒ banco 0; D.P.E. DESARROLLO DE PROYECTOS RP0 = 1 ⇒ banco 1 4 Estructura De La Memoria Ram (4) Los Registros SFR del Banco 0 En la figura que sigue se dan los registros del banco 0 que componen su zona SFR. El registro cuya dirección es 07H no está implementado. Mientras que los siguientes están duplicados en el banco 1: INDF, PCL, STATUS, FSR, PCLATCH, INTCON. D.P.E. DESARROLLO DE PROYECTOS 5 Estructura De La Memoria Ram (4) Los Registros SFR del Banco 1 En la figura que sigue se dan los registros del banco 1 que componen su zona SFR. El registro cuya dirección es 87h no está implementado. Mientras que los siguientes están duplicados en el banco 0: INDF, PCL, STATUS, FSR, PCLATCH, INTCON. D.P.E. DESARROLLO DE PROYECTOS 6 Los Registros SFR (1) Seguidamente damos una descripción de los registros SFR mas utilizados, el resto de los registros se irán explicando según se haga preciso. Las claves utilizadas para los valores de los bits son: R Bit de lectura W Bit de escritura Valores tras un reset: - No implementado se lee 0 X Desconocido u No se modifica, mantiene el valor anterior q Su valor depende de cual fué la causa del reset D.P.E. DESARROLLO DE PROYECTOS 7 Los Registros SFR (2) Registro de STATUS (1) El registro STATUS, es un registro, que contiene una serie de banderas que indican si una cierta condición se ha producido tras la ejecución de la última instrucción y otras informaciones que se detallan a continuación. Dirección: 03h del banco 0 y 83h del banco1 Bit 0: C flag de acarreo en el octavo bit (R, W, X) 1: Acarreo en la suma y no se “debe” en la resta. 0: No acarreo en la suma y se debe en la resta Bit 1: DC flag de acarreo en el cuarto bit (R, W, X) 1: Acarreo en la suma 0: No acarreo en la suma En la resta al contrario, se utiliza en operaciones en BCD Los Registros SFR (3) Registro de STATUS (2) Bit 2: Z flag de cero (R, W, X) 1: El resultado de la última operación lógica o aritmética fue 0. 0: El resultado de la última operación fue <> de 0. Bit 3: PD flag Power Down (R, 1) 1: Tras conectar VDD, o al ejecutar CLRWDT 0: Al ejecutar la instrucción SLEEP Bit 4: TO flag Timer Out (R, 1) 1: Tras conectar VDD o ejecutar CLRWDT o SLEEP 0: Al desbordarse el timer del WDT Los Registros SFR (4) Registro de STATUS (3) Bit 5: RP0 Selección del direccionamiento directo (R,W, 0) banco para 0 ⇒ Banco 0 (00h-7Fh); 1 ⇒ Banco 1 (80h-FFh) Bit 6 : RP1 En este µ no se utiliza. Bit 7 : IRP En este µ no se utiliza. Tanto RP1 como IRP no deben usarse como bits de uso general para garantizar la compatibilidad con futuros PIC. D.P.E. DESARROLLO DE PROYECTOS 10 Los Registros SFR (5) Registro INTCON • Dirección: 0Bh del banco 0 y 8Bh del banco1 El registro INTCON, es un registro de lectura escritura, que contiene las habilitaciones para las diferentes fuentes de interrupción, así como las banderas que indican que una cierta causa de interrupción se ha producido. Tras un reset todas las interrupciones se prohíben. Bit 7: GIE Activación global de interrupciones (R, W, 0) 1: Permite todas las interrupciones no enmascaradas. 0: Todas las interrupciones están prohibidas. El resto de los bits de este registro se explicarán en el tema de interrupciones. Los Registros SFR (6) Registros INDF y FSR (1) • Dirección: INDF 0h del banco 0 y 80h del banco1 • Dirección: FSR 04h del banco 0 y 84h del banco1 El registro INDF, no es un registro físico, direccionando INDF, realmente se señala al registro cuya dirección está contenida en el registro FSR; FSR es un puntero. Ambos registros se utilizan en conjunto para realizar direccionamientos indirectos. Al no estar implementado INDF, su lectura dará todo 0. El valor de FSR tras el Power On Reset (POR) es XXh, mientras que para las otras causa de reset no modifica su valor. Los Registros SFR (7) Registros INDF y FSR (2) Ejemplo de direccionamiento indirecto facilitado por Microchip. Este programa pone a cero lo registros entre 20h y 2FH. ........ movlw 0x20 ;inicializo FSR que actuará de puntero OTRO movwf FSR ;el valor inicial de FSR=20h clrf INDF ;pon a 0 el registro señalado por FSR incf FSR ;FSR señala a la siguiente posición btfss FSR,4 ;control para ver si se ha llegado a 2Fh goto OTRO ; si no he llegado a 2Fh vete a OTRO ............. Los Registros SFR (8) Registros PCL y PCLATCH (1) • Dirección: PCL 02h del banco 0 y 82h del banco1 • Dirección: PCLATH 0Ah del banco 0 y 8Ah del banco1 Como ya se indicó en el tema de memoria de programas, su unión forma el Contador de Programas. PCL es un registro de lectura\escritura y su valor tras el reset es 00h. PCLATH solo tiene implementados los 5 bits de menor peso, siendo un registro esclavo del PC <12:8>, el contenido de PCLATH puede ser transferido al byte alto del PC, pero nunca al contrario. Su valor tras el reset es de todo 0. Los Registros SFR (9) Registros PORTA y TRISA (1) • Dirección: PORTA 05h del banco 0 • Dirección: TRISA 85h del banco 1 TRISA es el registro de configuración del PUERTO A. Poniendo en cualquier bit de TRISA un 1, hacemos que el bit correspondiente del PUERTO A quede configurado como una entrada. Poniendo a 0 un bit de TRISA, se configura el pin correspondiente como salida. Como el PORTA, TRISA solo tiene implementados los cinco bits de menor peso. Tras el reset TRISA toma el valor 1Fh, por lo que el puerto queda configurado con todos sus pines como entradas. Los Registros SFR (10) Registros PORTA y TRISA (2) PORTA es un registro que solo tiene implementados los cinco bits de menos peso. Y es el latch donde se escribe el valor que se desea enviar a los pines del PUERTO A. Cuando se lee del PUERTO A, se lee el estado de cada uno de los pines de dicho puerto, siempre y cuando estuviesen configurados como entradas. Cuando se escribe en el puerto, se escribe en el latch y hay que tener en cuenta que son escrituras del tipo “readmodify-write”. Tras el reset POR, el valor del PORTA es indeterminado, mientras que cualquier otro reset hace que no se modifique su valor D.P.E. DESARROLLO DE PROYECTOS 16 Los Registros SFR (11) Registros PORTB y TRISB (1) • Dirección: PORTB 06h del banco 0 • Dirección: TRISB 86h del banco 1 TRISB es el registro de configuración del PUERTO B, poniendo en cualquier bit de TRISB un 1, hacemos que el bit correspondiente del PUERTO B quede configurado como una entrada. Poniendo a 0 un bit de TRISB se configura el pin correspondiente del PORB como salida. Tanto el PORTB, como TRISB tienen un ancho de 8 bits. Tras el reset TRISB toma el valor FFh, por lo que el puerto queda configurado con todos sus pines como entradas. D.P.E. DESARROLLO DE PROYECTOS 17 Los Registros SFR (12) Registros PORTB y TRISB (2) PORTB es un registro de 8 bits. Y es el latch donde se escribe el valor que se desea enviar a los pines del PUERTO B. Cuando se lee del PUERTO B se lee el estado de cada uno de los pines de dicho puerto, siempre y cuando estuviesen configurados como entradas Tras el reset POR, el valor del PORTB es indeterminado, mientras que cualquier otro reset hace que no se modifique su valor D.P.E. DESARROLLO DE PROYECTOS 18 Los Registros SFR (13) Registro OPTION (1) • Dirección: 81h del banco1 El registro OPTION, es un registro de lectura escritura, que contiene bits de control para configurar el preescaler de TIMER0/WDT , la interrupción externa, el TIMER0 y las resistencias de pull-up del PORTB Independientemente de la causa del reset adquiere siempre el valor FFh. Bit 7: RBPU#: Bit de habilitación de las resistencias de Pull Up del puerto B (W, R, 1). 1: Desactiva las resistencias de pull-up (valor de reset) 0: Activa las resistencias de pull-up. Los Registros SFR (14) Registro OPTION (2) Bit 6: INTEDG: Bit de selección de flanco activo para las interrupciones externas RB0/INT (W, R, 1). 1: Flanco de subida (valor por defecto). 0: flanco de bajada". Bit 5: TOCS: Bit de selección de los impulsos a contar por TMR0 (contador/temporizador) (W, R, 1). 1: Pulsos introducidos a través de RA4/TOCKI (contador, valor por defecto) 0: Pulsos del reloj interno Fosc/4 (temporizador). D.P.E. DESARROLLO DE PROYECTOS 20 Los Registros SFR (15) Registro OPTION (3) Bit 4: TOSE: Bit de selección de flanco activo para RA4/TOCKI (TMR0 como contador). 1: Flanco de subida (valor por defecto). 0: flanco de bajada". Bit 3: PSA: Asignación del divisor del preescaler (W, R, 1). 1: El divisor de frecuencia (preescaler) se asigna a WDT (valor tras el reset). 0: El divisor de frecuencia se asigna a TMR0. Cuando el preescaler está asignado a WDT, el preescaler para TMR0 es 1:1. D.P.E. DESARROLLO DE PROYECTOS 21 Los Registros SFR (16) Registro OPTION (4) Bit 2:0 PS2, PS1, PS0: Bits de selección del rango con el que actúa el preescaler PS2 PS1 PS0 rango para TMR0 rango para WDT 0 0 0 1:2 1:1 0 0 1 1:4 1:2 0 1:8 1:4 0 1 0 1 1 1:16 1:8 1 0 0 1:32 1:16 1 0 1 1:64 1:32 1 1 0 1:128 1:64 1 1 1 1:256 1:128 Los Registros SFR (18) Registros EEDATA, EEADR, EECON1 y EECON2 La memoria EEPROM de datos, que incorpora el 16F84 es una memoria de lectura/escritura de 64 bytes y direcciones de la 0 a 3fh, Esta memoria no está mapeada en el espacio de registros especiales. Para operar en ella, es necesario utilizar los registros especiales: EECON1, EECON2, EEDATA y EEADR Dichos registros así como la memoria EEPROM se describirán con mas profundidad en un tema específico 23