A 12-bit Resolution, 200-MSample/second Phase Modulator for a

Anuncio

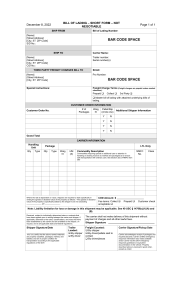

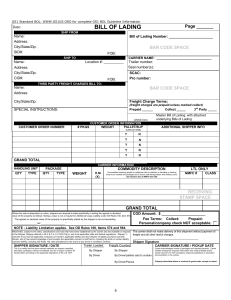

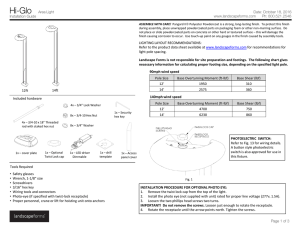

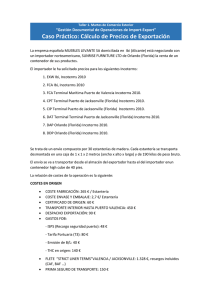

A 12-bit Resolution, 200-MSample/second Phase Modulator for a 2.5GHz Carrier with Discrete Carrier Pre-Rotation in 65nm CMOS Taylor W. Barton, SungWon Chung, Philip A. Godoy, and Joel L. Dawson Microsystems Technology Laboratories, Massachusetts Institute of Technology, Cambridge, MA 02139 Abstract— A digital-to-RF phase modulator based on a single current-steering DAC is presented, including a carrier pre-rotation scheme that prevents phase inaccuracy due to carrier feedthrough. The phase modulator has been fabricated in a standard 65-nm CMOS process and draws 1.9 mW from a 1-V supply. The modulator achieves 12-bit resolution at a measured 200 MSamples/second, state-of-theart performance in both resolution and sampling speed. It has sufficient speed to allow for oversampling to shape the output spectrum and therefore reduce filtering requirements, as demonstrated through a 32x oversampled 8-PSK signal at 6.25 MSymbols/second with under 6.1% EVM. Index Terms— Radio frequency integrated circuits, phase shifters, CMOS, phase modulation. cos(ωt) a φ [0 : 9] Current DAC 1−a sin(ωt) ±1 Sout (t) ±1 quadrant[0:1] Fig. 1. Block diagram for single-DAC phase modulator, excluding carrier pre-rotation. The phase-modulated output signal is Sout = ±a cos(ωt)±(1−a) sin(ωt), where coefficient 0 ≤ a < 1 is controlled by digital input φ[0 : 9]. I. I NTRODUCTION This paper presents a digital-to-RF phase modulator (DRFPM) that has both the speed and the accuracy required for demanding applications such as outphasing and PSK transmitters. Such transmitters place a heavy demand on the phase modulator. For example, an outphasing-type architecture as in [1] relies critically on precise phase control for highly linear modulation. At the same time, the phase modulator must handle a signal that is significantly bandwidth expanded due to the nonlinear transformation from an I/Q representation to amplitude/phase. The DRFPM presented in this work, with its 12-bit phase resolution and 200 MSample/second sample rate, demonstrates state-of-the-art performance in terms of sample rate, resolution, and power dissipation. It introduces a carrier pre-rotation scheme to overcome effects of carrier feedthrough and thereby extend the accuracy and operating range. II. T OPOLOGY A block diagram of the single-DAC topology is shown in Fig. 1. The phase modulator works on the principle of vector addition, where a signal with arbitrary phase is generated by summing weighted components of sine and cosine. Although in general this function can be performed with arbitrary coefficients a and b, with output Sout (t) = ±a cos(ωt) ± b sin(ωt), imposing the constraint that b = 1 − a has several advantages. With only one DAC required, area and power are nearly halved compared to a rotator scheme as in [1], as is the number of current 978-1-4244-8292-4/11/$26.00 ©2011 IEEE sources requiring strict matching. Amplitude variation in √ the output is limited to a factor of 1/ 2 within full scale, and is removed with a limiter stage. This approach is related to those used in [2] and [3] to reduce the number of required current cells over the more conventional approach of [1]. The relatively high phase resolution of this work as compared to [2], [3] makes the area and power advantages of a single-DAC topology significant. The phase nonlinearity introduced by using a cos(ωt) and (1√− a) sin(ωt) instead of the conventional a cos(ωt) and ( 1 − a2 ) sin(ωt) is compensated for in our testing using a static lookup table. Modern transmitters increasingly rely on such digital assistance [1]. Here we exploit this trend to simplify the DRFPM and get higher speed and resolution for lower area and power consumption. A. Core Topology The current-steering DAC is implemented as shown in Fig. 2 using ten binary-weighted current sources that are created by the parallel combination of identical unit transistors. The combination of PMOS and NMOS devices allows the use of NMOS transistors for the critical switching at the carrier frequency, with PMOS devices selected for the relatively slow sample rate switching and static current generation. The current sources are steered by latched differential switches that establish the currents corresponding to a and b = 1 − a. The data switches and their drivers are scaled in area in a binary-weighted sense 512× 10 Data 256× bit 9 Latch Ia9 bit 8 Ib9 Ia8 cos clk I Ia3 Ib8 8× 1× bit 3 bit 0 Ib3 sin cos Ia0 Ib0 8× 8ILSB sin clk Q IIP sign I IIN IQP IQN Latch Latch sign Q output RL RL Fig. 2. Simplified schematic of the single-DAC DRFPM. Reducing the number of DACs from two reduces the power and area of this block by 50%. The output sinusoid is a sin(ωt) + (1 − a) cos(ωt), and amplitude variation is removed by the limiters. Ten bits are shown near the top of this figure. The remaining two bits are achieved through the sign of I and Q. by combining unit cells based on the buffer-latch-switch structure in [4]. The area scaling results in a matched voltage at the drain of the current sources, allowing a simple current mirror to be used because the data switches act like a cascode. Differential switches are driven by quadrature square waves at the carrier frequency to perform the multiplication of a cos(ωt) and (1 − a) sin(ωt). As with the data switches and latches, the multiplicity of the differential switch pairs is scaled corresponding to the current. The minimum size unit switching cell is used for the four least significant currents combined, then each higher bit uses a binary-scaled number of parallel unit switching cells. Scaling in this way reduces the total area cost as compared to simply using binary-scaled sizing for all bits. The resulting code-dependent difference in drain voltage for the four least significant bits has a limited effect on those current sources due to the cascode effect from the data switches. The current-mode outputs of the multiplying switches are summed. The sign of these now differential signals, and thus the quadrant of the output, is controlled by two control inputs and is selected using differential switches with cross-coupled outputs. Currents are combined and converted to voltages to produce a differential phase- modulated signal. A limiter maintains the phase (zerocrossing) information while normalizing the signal amplitude. B. Carrier Pre-rotation Due to carrier feedthrough and transistor leakage, it is difficult with any current-steering-based architecture to provide outputs directly aligned with the quadrature carrier signals, since the scaled vector coefficients a and (1 − a) can never be made zero. The resulting missing codes in output phase can limit the absolute phase accuracy. For the fabricated DRFPM a gap of 3.7 degrees was measured. The missing codes problem was solved by using two sets of quadrature signals at the carrier frequency. In this strategy, one set is delayed with respect to the other to function as a pre-rotated carrier. By thus providing two reference phases, any output phase can be produced so long as the output phase gaps do not overlap. Both carrier signals are generated on-chip from a differential source at twice the carrier frequency using the static 2:1 frequency divider shown in Fig. 3. The phase delay between the two sets of quadrature carrier signals is generated using inverter delays. A more well-controlled phase shift is not required as the precise amount of prerotation is not critical so long as it is greater than the total angle subtended by the missing codes. The inverter delay was chosen to give an D Q clk I Q D Q Q sel 2fc D Q Q D Q clk Q Q (a) 180◦ step command. Phase (Degrees) Fig. 3. LO generation and discrete pre-rotation. 360 270 180 Prerotated 90 0 Unrotated 0 1024 2048 Digital Code Word 3072 4096 Phase (Degrees) (a) Raw static curves. 360 (b) Carrier rotation step command 270 Fig. 5. DRFPM response to step command. A constant-phase 2.5GHz sinusoid is shown for reference. 180 90 0 0 1024 2048 Digital Code Word 3072 4096 (b) Combined LUT. Fig. 4. Transfer curves showing (a) un- and pre-rotated outputs and (b) combined LUT made up of eight segments of the curves in (a). Detail in (a) shows missing codes due to carrier feedthrough. approximately 45 degree phase shift under typical process conditions. III. M EASURED R ESULTS The DRFPM was fabricated in a 65-nm CMOS process, with an area of 0.26 mm2 . The static power consumption by the current sources for two DRFPMs is 1.9 mW from a 1-V supply. The static raw transfer curve is shown in Fig. 3(a), with the lower curve corresponding to unrotated phases, and the upper demonstrating carrier pre-rotation. The gaps at quadrant transitions are removed by the straightforward combination of eight segments of these two curves, giving the transfer curve of Fig. 3(b). The largest incremental phase transition was measured to be 0.99 degrees. Included on-chip to enable communication between the chip and the driving FPGA are LVDS receivers. To lower pin count we use serialized transmission, in which each LVDS receiver handles two interleaved channels. An error in the on-chip deserialization block prevents a full characterization above 200 MSamples/second. Thus the DRFPM’s speed is best observed from its step response as shown in Fig. 5. It can be seen that for the worst-case phase transition of 180 degrees, the output phase settles within 4 periods of the carrier, or 1.6 ns. This performance indicates that the fabricated circuit has the potential to perform at up to 625 MSamples/second. The carrier pre-rotation path, with its 1.4-ns step response as in Fig. 5(b), demonstrates similar performance. The benefit of using a high (32x) oversampling ratio in the baseband digital front-end before upconversion as a way to reduce filtering requirements has been demonstrated in [6]. The DRFPM in this work has an advantage over lower resolution phase modulators in that it can similarly exploit oversampling to push zero-order hold replicas to higher frequency. Fig. 6 shows the improvement of the spectrum of a 32x oversampled 6.25 MSymbol/second 8PSK signal compared to one without oversampling. Both (a) No oversampling. EVM=5.93% rms. (b) 32x oversampling. EVM=6.09% rms. Fig. 6. 8-PSK constellation and spectrum at 6.25 MSymbols/second with and without 32x oversampling. Measurement span is 97MHz and 2000 symbols. TABLE I C OMPARISON OF THIS WORK Parameter: This work JSSC’09 [1] JSSC’09 [2] PRIME’09 [3] MTT’06 [5] WITH STATE- OF - THE - ART. Its speed allows for oversampling to shape the spectrum and therefore reduce filtering requirements. The single 12bit plus 1 input control word and single-DAC topology reduces complexity, size, and power consumption as compared to conventional current-steering phase modulators. Carrier frequency Measured sample rate Phase resolution Process 2.5 GHz 200 MSPS 12 bits 65 nm 0.8-5GHz 50 MSPS 14 bits 90nm ACKNOWLEDGEMENT The authors wish to thank the TSMC University Shuttle Program for the fabrication of this design. 60 GHz 3.1-10.6 GHz 1.753.5GHz 2.5 GSPS 6 bits 90 nm 3.8 GSPS 4 bits 65 nm 500 MSPS 4 bits 0.18 µm Note: Power consumption figures are not available for refs. [1] and [2]. Power consumption is 2.78mW for ref [3], and 3.6mW for ref [5], compared with 1.9mW for this work. measurements were performed without using the carrier pre-rotation mode of the phase modulator; i.e. using a single transfer curve from Fig. 4(a). The comparison to the state-of-the-art in Table I shows that this work represents state-of-the-art performance in terms of its combination of sample rate and resolution. IV. C ONCLUSION A DRFPM has been shown to be capable of broadband modulation at a phase accuracy suitable for modern communications standards. The phase modulator’s 12-bit resolution gives it the precision necessary to meet the strict linearity requirements of modern standards. R EFERENCES [1] M. Heidari, M. Lee, and A. Abidi, “All-digital outphasing modulator for a software-defined transmitter,” IEEE J. Solid-State Circuits, vol. 44, no. 4, pp. 1260 –1271, April 2009. [2] C. Marcu, D. Chowdhury, C. Thakkar, J.-D. Park, L.-K. Kong, M. Tabesh, Y. Wang, B. Afshar, A. Gupta, A. Arbabian, S. Gambini, R. Zamani, E. Alon, and A. Niknejad, “A 90 nm CMOS low-power 60 GHz transceiver with integrated baseband circuitry,” IEEE J. Solid-State Circuits, vol. 44, no. 12, pp. 3434 –3447, Dec. 2009. [3] O. Casha, I. Greek, and F. Badets, “CMOS phase-interpolation DDS for an UWB MB-OFDM alliance application,” in Proc. Conf. on Ph.D. Research in Microelectronics and Electronics, 12-17 2009, pp. 200 –203. [4] J. Deveugele and M. Steyaert, “A 10-bit 250-MS/s binary-weighted current-steering DAC,” IEEE J. Solid-State Circuits, vol. 41, no. 2, pp. 320–329, Feb. 2006. [5] X. Yang and J. Lin, “A digitally controlled constant envelope phaseshift modulator for low-power broad-band wireless applications,” IEEE Trans. Microwave Theory Tech., vol. 54, no. 1, pp. 96 –105, Jan. 2006. [6] X. He, J. van Sinderen, and R. Rutten, “A 45nm WCDMA transmitter using direct quadrature voltage modulator with high oversampling digital front-end,” in Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2010 IEEE International, 2010, pp. 62 –63.