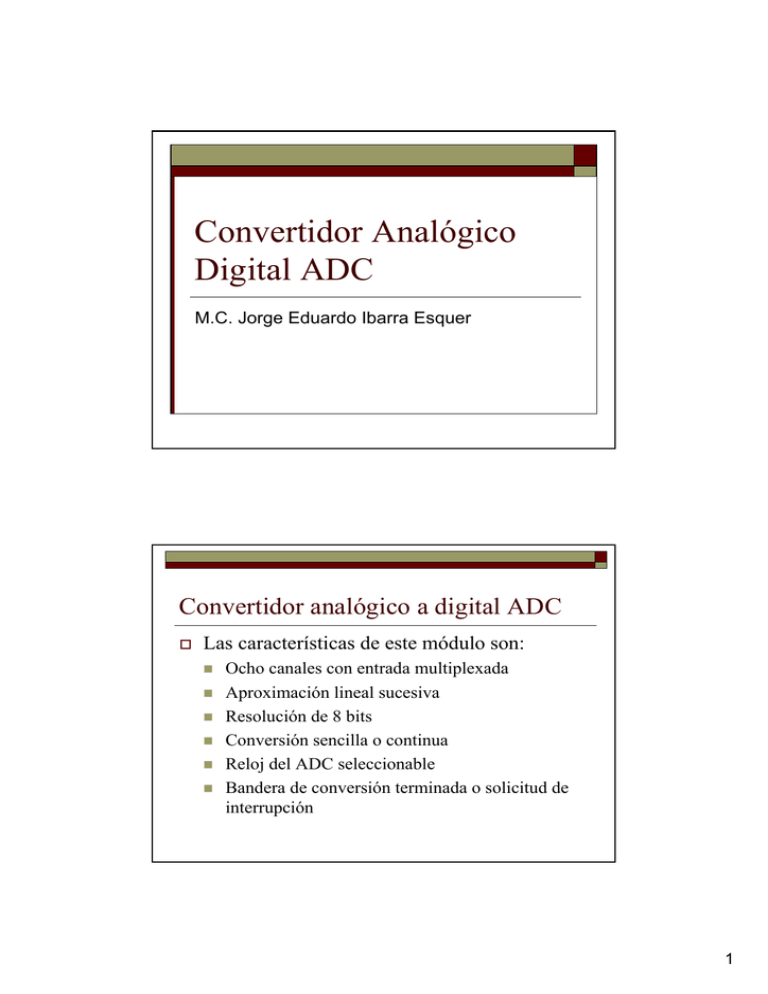

Convertidor Analógico Digital ADC

Anuncio

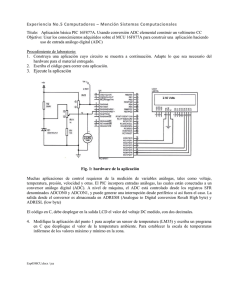

Convertidor Analógico Digital ADC M.C. Jorge Eduardo Ibarra Esquer Convertidor analógico a digital ADC Las características de este módulo son: Ocho canales con entrada multiplexada Aproximación lineal sucesiva Resolución de 8 bits Conversión sencilla o continua Reloj del ADC seleccionable Bandera de conversión terminada o solicitud de interrupción 1 Convertidor analógico a digital ADC El ADC proporciona 8 terminales para el muestreo de fuentes externas (PTB7/AD7 PTB0/AD0) Un multiplexor analógico permite al ADC seleccionar uno de los 8 canales como voltaje de entrada (ADCVIN) Una vez que se ha convertido el voltaje, el resultado se coloca en el registro de datos del ADC y activa una bandera o genera una interrupción 2 Terminales del ADC Las terminales del puerto B se comparten para ser utilizadas como los canales del ADC Los canales seleccionados para el ADC forzarán a sus terminales correspondientes a comportarse como entradas. El resto de ellas serán controladas por la lógica de E/S del puerto Terminales del ADC Escribir en el registro de datos del puerto o en el DDR, no afectará a ninguna terminal seleccionada para el ADC. La lectura de cualquiera de estas terminales regresará un 0 lógico 3 Conversión de voltaje Cuando el voltaje de entrada a un canal sea igual al voltaje de referencia alto VREFH, el resultado de la conversión será $FF Si el voltaje de entrada es igual al voltaje de referencia bajo VREFL, el resultado de la conversión será $00 Cualquier voltaje entre los de referencia, se convertirá utilizando una escala lineal Tiempo de conversión La conversión empieza después de escribir al ADSCR Una conversión tomará entre 16 y 17 ciclos del reloj del ADC. Los bits ADIVx y ADICLK debén asignarse para dar una frecuencia de 1MHz al reloj del ADC Tiempo de conversión = 16-17 ciclos del ADC Frecuencia del ADC 4 Modo de conversión contínua En este modo de operación, el registro se llenará con datos nuevos después de cada conversión. Los datos de la conversión anterior se sobreescribirán, hayan sido leídos o no Las conversiones continuarán hasta que se borre el bit ADCO Modo de conversión contínua Después de la primera conversión se activa el bit COCO/IDMAS, y permanece activo hasta la siguiente escritura del registro de estado y control del ADC o la siguiente lectura del registro de datos 5 Modo de conversión sencilla En este modo de operación, la conversión se inicia con una escritura al ADSCR Solamente se realiza una conversión después de cada escritura al ADSCR Interrupciones del ADC Cuando se encuentra activo el bit AIEN, el módulo del ADC es capaz de generar solicitudes de interrupción después de cada conversión Una interrupción se genera si el bit COCO/IDMAS tiene un 0 lógico Si están habilitadas las interrupciones, el bit COCO/IDMAS no se utiliza como bandera de conversión completa 6 Registro de estado y control del ADC Registro de estado y control del ADC COCO/IDMAS – Conversiones completas / Bit de selección de interrupción DMA Si el bit AIEN tiene un 0 lógico, este bit es de sólo lectura y se activa cada vez que se completa una conversión En el modo de conversión contínua, se activa después de la primer conversión Se borra al escribir en el ADSCR o leer el ADR 7 Registro de estado y control del ADC COCO/IDMAS – Conversiones completas / Bit de selección de interrupción DMA Si el bit AIEN tiene un 1 lógico, este bit se utiliza para seleccionar ya sea al CPU o al DMA para dar servicio a la solicitud de interrupción IDMAS=0 – Interrupción del CPU IDMAS=1 – Interrupción del DMA COCO=0 – Conversión incompleta COCO=1 – Conversión completa El microcontrolador GP20 no tiene un módulo de DMA Registro de estado y control del ADC AIEN – Bit de habilitación de la interrupción del ADC Cuando este bit está activo, se genera una interrupción al terminar una conversión La señal de interrupción se borra al leer el registro de datos o escribir en el registro de control 8 Registro de estado y control del ADC ADCO – Bit de conversión contínua del ADC Cuando está activo, el ADC realizará las conversiones de manera contínua y actualizará el ADR al terminar cada una de ellas Si su valor es un 0 lógico, solamente se realizará una conversión entre cada escritura al registro de control Registro de estado y control del ADC ADCH4-ADCH0 – Bits selectores del canal del ADC Con estos bits se forma un valor de 5 bits que nos permite seleccionar un total de 16 canales El módulo del ADC se desactivará si los 5 bits de selección tienen un 1 lógico 9 Registro de estado y control del ADC Registro de datos del ADC 10 Registro del reloj del ADC Registro del reloj del ADC ADIV2-ADIV0 – Bits preescaladores del reloj Estos bits forman un campo de 3 bits que selecciona el valor que el ADC utilizará para generar el reloj interno del ADC El reloj debe establecerse en aproximadamente 1MHz 11 Registro del reloj del ADC ADIV2-ADIV0 – Bits preescaladores del reloj Registro del reloj del ADC ADICLK – Bit selector de la entrada del reloj Selecciona ya sea el reloj del bus o la entrada CGMXCLK como la fuente del reloj para generar la señal de reloj del ADC ADICLK=1 Æ Reloj del bus ADICLK=0 Æ Reloj externo (CGMXCLK) 12