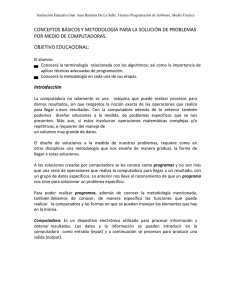

DISEÑO DE BLOQUES DE MEMORIA Procedimiento para el

Anuncio

Diseño de mapas de memoria DISEÑO DE BLOQUES DE MEMORIA La ampliación de componentes es una característica del diseño y en el caso de las memorias tiene dos objetivos: Incrementar el tamaño de las palabras. Incrementar el número de palabras de memoria. Un sistema basado en microprocesador tiene una capacidad de direccionamiento y anchura de palabra en función de las características del microprocesador de acuerdo al bus de direcciones y del de datos respectivamente. Siendo el bus de control, específico al microprocesador. De esta manera, la capacidad del sistema depende de: ⇒ 2n siendo n el nº de bits del bus de direcciones del µP − Direccionamiento del sistema − Ancho de palabra − Bus de control depende del µP, siendo las señales típicas para la memoria la de lectura ( R ) y la de escritura (W) ⇒m siendo m el nº de bits del bus de datos del µP Procedimiento para el diseño de un mapa de memoria de un sistema basado en microprocesador: 1. Detallar las necesidades del sistema en cuanto a direccionamiento, anchura de palabra y tipo de memoria a utilizar (RAM/ROM). 2. Determinar los circuitos integrados de que se dispone, tanto en longitud como en anchura de palabras y definir los que se necesitan. 3. Construir el mapa de memoria. 4. Determinar el tamaño de página y diseñar la tabla de direcciones y ocupación de cada circuito integrado. 5. Determinar la circuitería auxiliar necesaria para el control del circuito. 6. Dibujar el circuito completo de la memoria. Para analizar el procedimiento tomaremos como base el siguiente ejemplo: Diseñar el mapa de memoria de un sistema basado en microprocesador para el 8085 de INTEL (A0..A15, D0..D7), suponiendo que se necesitan 8K×8 de memoria ROM, 4K×8 de memoria RAM. Se disponen de circuitos integrados ROM de 2K×8 y circuitos integrados RAM de 2K×8 y que la memoria está situada a partir de la dirección $0 empezando por la ROM y colocando a continuación la RAM. 1. Detallar las necesidades del sistema en cuanto a direccionamiento, anchura de palabra y tipo de memoria a utilizar (RAM/ROM). 8K×8 de memoria ROM 4K×8 de memoria RAM 2. Determinar los circuitos integrados de que se dispone, tanto en longitud como en anchura de palabras y definir los que se necesitan. N º _ bits _ necesitados 8 K × 8 = 4 _ circuitos _ ROM = 2K × 8 N º _ bits _ por _ CI N º _ bits _ necesitados 4 K × 8 = 2 _ circuitos _ RAM Circuitos integrados RAM RAM = = 2K × 8 N º _ bits _ por _ CI Circuitos integrados ROM ROM = 3. Construir el mapa de memoria. IC0 (2K×8) IC1 (2K×8) IC2 (2K×8) IC3 (2K×8) IC4 (2K×8) IC5 (2K×8) Libre Libre ROM ROM ROM ROM RAM RAM Página 1 Diseño de mapas de memoria 4. Determinar el tamaño de página y diseñar la tabla de direcciones y ocupación de cada circuito integrado. Determinaremos los bits del bus de direcciones en función del tamaño total de la memoria: 8K _ ROM + 4 K _ RAM = 12 K 213 = 8192bytes ⇒ 2 = 16384bytes 14 214 = 16384bytes ⇒ bus de direcciones A0..A13 bus de datos D0..D7 El tamaño de página en este caso será de 2K ya que todos los circuitos integrados son de 2K 211 = 2048bytes ⇒ A0..A10 ⇒ ⇒ A11, A12, A13 2 = 8 páginas de las Bits de selección de página A11→ A13 cuales las 6 primeras se usan por los circuitos integrados y las dos últimas quedan libres. Tabla de direcciones 3 Selec. Página Dir hexadec. Agrup hexadecim. A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 1 1 1 1 1 1 1 1 1 1 1 0 1 1 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 1 1 1 1 1 1 1 1 1 1 1 1 0 1 0 0 0 0 0 0 0 0 0 0 0 1 0 1 1 1 1 1 1 1 1 1 1 1 1 $0000 $07FF $0800 $0FFF $1000 $17FF $1800 $1FFF $2000 $27FF $2800 $2FFF Cir. Integrado IC0 IC1 IC2 IC3 IC4 IC5 5. Determinar la circuitería auxiliar necesaria para el control del circuito. Como se puede observar el número de páginas es de 6, pero el mínimo que podemos controlar es de 8, es por lo que necesitaremos un decodificador de 3 a 8, de forma que las líneas del bus de direcciones del sistema A11, A12 Y A13 se conectarán a las entradas I0, I1 e I2 respectivamente y cada una de las salidas de O0 a O5 se conectarán a los Chip Select (CS) de cada los circuitos integrados de IC0 a IC5. Página 2 Diseño de mapas de memoria 6. Dibujar el circuito completo de la memoria. MEMORIA DE 8Kx8 DE ROM Y 4Kx8 DE RAM D[0..7] U1 36 1 2 5 6 9 8 7 10 11 29 33 39 35 RST-IN AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7 A8 A9 A10 A11 A12 A13 A14 A15 X1 X2 SID TRAP RST 5.5 RST 6.5 RST 7.5 INTR INTA ALE W\R\ R\D\ IO/M\ RST-OT CLKO SOD HLDA S0 S1 HOLD READY 12 13 14 15 16 17 18 19 21 22 23 24 25 26 27 28 A8 A9 A10 A11 A12 A13 A14 A15 D0 D1 D2 D3 D4 D5 D6 D7 3 4 7 8 13 14 17 18 11 1 U3 D1 D2 D3 D4 D5 D6 D7 D8 Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8 CLK CLR 2 5 6 9 12 15 16 19 A0 A1 A2 A3 A4 A5 A6 A7 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 IC0 8 7 6 5 4 3 2 1 23 22 19 18 20 21 74ABT273 . A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 O0 O1 O2 O3 O4 O5 O6 O7 9 10 11 13 14 15 16 17 D0 D1 D2 D3 D4 D5 D6 D7 ROM A0 8 A1 7 A2 6 A3 5 A4 4 A5 3 A6 2 A7 1 A8 23 A9 22 A10 19 18 20 21 C\E\ O\E\ VPP IC1 O0 O1 O2 O3 O4 O5 O6 O7 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 9 10 11 13 14 15 16 17 D0 D1 D2 D3 D4 D5 D6 D7 ROM A0 8 A1 7 A2 6 A3 5 A4 4 A5 3 A6 2 A7 1 A8 23 A9 22 A10 19 18 20 21 C\E\ O\E\ VPP IC2 O0 O1 O2 O3 O4 O5 O6 O7 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 9 10 11 13 14 15 16 17 D0 D1 D2 D3 D4 D5 D6 D7 9 10 11 13 14 15 16 17 D0 D1 D2 D3 D4 D5 D6 D7 ROM C\E\ O\E\ VPP 30 31 32 34 3 37 4 38 8085 A11 A12 A13 . 1 2 3 6 4 5 U4 A B C G1 G2A G2B 74F138 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 15 14 13 12 11 10 9 7 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 IC3 8 7 6 5 4 3 2 1 23 22 19 18 20 21 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 IC3 O0 O1 O2 O3 O4 O5 O6 O7 9 10 11 13 14 15 16 17 D0 D1 D2 D3 D4 D5 D6 D7 ROM C\E\ O\E\ VPP A0 8 A1 7 A2 6 A3 5 A4 4 A5 3 A6 2 A7 1 A8 23 A9 22 A10 19 18 20 21 IC4 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 C\E\ R/W\ O0 O1 O2 O3 O4 O5 O6 O7 RAM 9 10 11 13 14 15 16 17 D0 D1 D2 D3 D4 D5 D6 D7 A0 8 A1 7 A2 6 A3 5 A4 4 A5 3 A6 2 A7 1 A8 23 A9 22 A10 19 18 20 21 IC5 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 O0 O1 O2 O3 O4 O5 O6 O7 RAM C\E\ R/W\ A[0..15] Página 3 Diseño de mapas de memoria Diseñar el mapa de memoria de un sistema basado en microprocesador para el 8085 de INTEL (A0..A15, D0..D7), suponiendo que se necesitan 8K×8 de memoria ROM, 1K×8 de memoria RAM y 2 entrada/salida de 8 bits en el bus de direcciones. Se disponen de circuitos integrados ROM de 8K×1, circuitos integrados RAM de 1K×4 y de las correspondientes entrada/salida y que la memoria está situada a partir de la dirección $0 empezando por la ROM, colocando a continuación la RAM y por úlitimo las entradas/salidas 1. Detallar las necesidades del sistema en cuanto a direccionamiento, anchura de palabra y tipo de memoria a utilizar (RAM/ROM). 8K×8 de memoria ROM 1K×8 de memoria RAM 2 entrada/salida 2. Determinar los circuitos integrados de que se dispone, tanto en longitud como en anchura de palabras y definir los que se necesitan. N º _ bits _ necesitados 8K × 8 = = 8 _ circuitos _ ROM N º _ bits _ por _ CI 8K × 1 Circuitos integrados RAM RAM = N º _ bits _ necesitados = 1K × 8 = 2 _ circuitos _ RAM N º _ bits _ por _ CI 1K × 4 Circuitos integrados ROM ROM = IC8 IC7 IC6 IC5 IC4 IC3 IC2 IC1 3. Construir el mapa de memoria. ICO IC9 ROM (8K*8) RAM (1K*8) (E/S) (E/S) IC10 (E/S) IC11 (E/S) 4. Determinar el tamaño de página y diseñar la tabla de direcciones y ocupación de cada circuito integrado. Determinaremos los bits del bus de direcciones en función del tamaño total de la memoria: 8 K _ ROM + 1K _ RAM + 2 K _ E / S = 11K 213 = 8192bytes 2 = 16384bytes 14 ⇒ 214 = 16384bytes ⇒ bus de direcciones A0..A13 bus de datos D0..D7 El tamaño de página en este caso será de 1K ya que se puede elegir entre el tamaño mayor (8K , el menor 256Bytes (E/S) o el intermedio (RAM de 1K). La circuitería menos complicada y con un aprovechamiento relativamente óptimo se consigue con el valor intermedio (1K). 210 = 1024bytes ⇒ A0..A9 Bits de selección de página A10 A13 ⇒ A10, A11, A12, A13 ⇒ 2 4 = 16 páginas de las cuales las 11 primeras se usan por los circuitos integrados y las cinco últimas quedan libres. Página 4 Diseño de mapas de memoria Tabla de direcciones Selec. Página Dir hexadec. Agrup hexadecim. A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 1 1 1 1 0 0 X X X X X X X X 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 $0000 $1FFF $2000 $23FF $2400 $27FF $2800 $2BFF Cir. Integrado IC0 a IC7 IC8 + IC9 IC10 IC11 5. Determinar la circuitería auxiliar necesaria para el control del circuito. Como se puede observar el número de páginas es de 11, pero el mínimo que podemos controlar es de 16, es por lo que necesitaremos un decodificador de 4 a 16, de forma que las líneas del bus de direcciones del sistema A10, A11, A12 Y A13 se conectarán a las entradas I0, I1, I2 e I3 respectivamente y cada una de las salidas de O0 a O12 se conectarán a los Chip Select (CS) de cada los circuitos integrados de IC0 a IC11, teniendo en cuenta que como la ROM de 8Kx8 ocupa 8 páginas se deberán conectar las 8 primeras salidas a una puerta AND que conectará su salida al CS del integrado ROM. Página 5 Diseño de mapas de memoria 6. Dibujar el circuito completo de la memoria. MEMORIA DE 8Kx8 DE ROM, 1Kx8 DE RAM Y 2 E/S D[0..7] U1 36 1 2 5 6 9 8 7 10 11 29 33 39 35 AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7 A8 A9 A10 A11 A12 A13 A14 A15 RST-IN X1 X2 SID TRAP RST 5.5 RST 6.5 RST 7.5 INTR INTA ALE W\R\ R\D\ IO/M\ RST-OT CLKO SOD HLDA S0 S1 HOLD READY 12 13 14 15 16 17 18 19 21 22 23 24 25 26 27 28 A8 A9 A10 A11 A12 A13 A14 A15 D0 D1 D2 D3 D4 D5 D6 D7 U3 3 4 7 8 13 14 17 18 D1 D2 D3 D4 D5 D6 D7 D8 11 1 Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8 2 5 6 9 12 15 16 19 CLK CLR A0 A1 A2 A3 A4 A5 A6 A7 A010 A1 9 A2 8 A3 7 A4 6 A5 5 A6 4 A7 3 A825 A924 A10 21 A11 23 A12 2 74ABT273 20 22 . A10 A11 A12 A13 . 2 3 21 22 1 23 D1 D2 D3 D4 ST INH S0 S1 S2 S3 S4 S5 S6 S7 S8 S9 S10 S11 S12 S13 S14 S15 11 9 10 8 7 6 5 4 18 17 20 19 14 13 16 15 O0 11 D0 A010 A1 9 A2 8 A3 7 A4 6 A5 5 A6 4 A7 3 A825 A924 A10 21 A11 23 A12 2 20 22 CE OE 30 31 32 34 3 37 4 38 IC1 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 1 2 3 4 A010 A1 9 A2 8 A3 7 A4 6 A5 5 U9 8 5 6 11 12 4 5430 A7 3 A825 A924 A10 21 A11 23 A12 2 20 22 IC4 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 O0 O0 11 D1 A010 A1 9 A2 8 A3 7 A4 6 A5 5 A6 4 A7 3 A825 A924 A10 21 A11 23 A12 2 20 22 CE OE ROM 8K*1 8085 U8 IC0 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 IC2 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 D4 A010 A1 9 A2 8 A3 7 A4 6 A5 5 A6 4 A7 3 A825 A924 A10 21 A11 23 A12 2 20 22 CE OE IC5 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 O0 A0 10 A1 9 A2 8 A3 7 A4 6 A5 5 A6 4 A7 3 A8 25 A9 24 A10 21 A11 23 A12 2 20 22 11 D5 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 10 9 8 7 6 5 4 3 25 24 21 A11 23 2 A12 20 22 IC6 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 O0 11 D6 10 A1 9 A2 8 A3 7 A4 6 A5 5 A6 4 A7 3 A825 A924 A1021 A1123 A12 2 20 22 CE OE ROM 8K*1 IC3 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 O0 11 D3 11 D7 9 10 11 13 14 15 16 17 D0 D1 D2 D3 D4 D5 D6 D7 CE OE ROM 8K*1 ROM 8K*1 CE OE ROM 8K*1 11 D2 CE OE ROM 8K*1 11 O0 IC7 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 O0 CE OE ROM 8K*1 ROM 8K*1 74HC4515 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 8 7 6 5 4 3 2 1 23 22 18 20 IC8 O0 O1 O2 O3 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 CE R/W RAM 1K*8 9 10 11 13 D0 D1 D2 D3 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 8 7 6 5 4 3 2 1 23 22 18 20 IC9 O0 O1 O2 O3 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 9 10 11 13 D4 D5 D6 D7 A0 A1 A2 A3 A4 A5 A6 A7 8 7 6 5 4 3 2 1 18 20 CE R/W RAM 1K*8 IC10 A0 A1 A2 A3 A4 A5 A6 A7 O0 O1 O2 O3 O4 O5 O6 O7 9 10 11 13 14 15 16 17 D0 D1 D2 D3 D4 D5 D6 D7 A0 A1 A2 A3 A4 A5 A6 A7 8 7 6 5 4 3 2 1 18 20 CE R/W IC11 A0 A1 A2 A3 A4 A5 A6 A7 O0 O1 O2 O3 O4 O5 O6 O7 CE R/W 8255 8255 A[0..15] Página 6 Diseño de mapas de memoria 2.- Supóngase una memoria RAM de 1024 palabras ⋅ 16 bits/palabra construida empleando circuitos integrados de memoria RAM de 128 palabras ⋅ 8 bits/palabra. A fin de permitir el direccionamiento de las palabras de la memoria, el bus de direcciones: A) Tiene 10 líneas, 7 de ellas comunes a todos los módulos. B) Tiene 10 líneas, 3 de ellas comunes a todos los módulos. C) Tiene 10 líneas, todas ellas comunes a todos los módulos. D) Ninguna de las anteriores es verdadera. 1ª semana 3.- Se considera un procesador que dispone de 12 líneas de direcciones A11-A0. Para la construcción de su unidad de memoria se dispone de módulos de 2K palabras, utilizándose la línea A1 para la selección de cada módulo (A0 es la línea menos significativa). Indique cuál de las siguientes afirmaciones es verdadera: A) Las direcciones hexadecimales C89 y C8A se encuentran almacenadas en el mismo módulo de memoria. B) Las direcciones hexadecimales C89 y C8A se encuentran almacenadas en diferentes módulos de memoria. C) El módulo en que se encuentra almacenada una dirección de memoria queda determinado por el valor de A10. D) Ninguna de las anteriores es verdadera. 7.- Se considera un procesador que dispone de 12 líneas de direcciones A11-A0. Para la construcción de su unidad de memoria se dispone de módulos de 1K palabras, utilizándose las líneas menos significativas (A1-A0) para la selección de cada módulo. Indique cuál de las siguientes afirmaciones es verdadera: A) Las direcciones hexadecimales C89 y C8A se encuentran almacenadas en el mismo módulo de memoria. B) Las direcciones hexadecimales C89 y C8A se encuentran almacenadas en diferentes módulos de memoria. C) El módulo en que se encuentra almacenada una dirección de memoria queda determinado por el valor de D) Ninguna de las anteriores es verdadera. 2.- Un computador con 13 líneas de direcciones tiene una memoria de 3×211 palabras y utiliza entrada/salida localizada en memoria. ¿Cuál es el número máximo de periféricos que pueden conectarse, suponiendo que cada uno de ellos utiliza 16 direcciones? A) 211. B) 27 C) 2. D) Ninguna de las anteriores. Junio del 2000 2ª Semana 8.- Se considera un procesador que dispone de 12 líneas de direcciones A11-A0. Para la construcción de su unidad de memoria se dispone de módulos de 1K palabras, utilizándose las líneas más significativas (A11-A10) para la selección de cada módulo. En el mapa de memoria, la dirección base (primera dirección de cada módulo) en notación hexadecimal de los sucesivos bloques de memoria es: Solución: $00 $400 $800 y $C00 Septiembre del 2003 6.- Se quiere diseñar una memoria para un computador que tiene una arquitectura basada en palabras de 16 bits y un bus de direcciones de 20 líneas de manera que disponga de 500 Kpalabras de memoria RAM y 240 Kpalabras de memoria ROM. Sabiendo que se disponen de módulos de memoria RAM de 128 Kpalabras x 8 bits/palabra, 128 Kpalabras x 16 bits/palabra; y de módulos de memoria ROM de 128 Kpalabras x 8 bits/palabra, 128 Kpalabras x 16 bits/palabra, I. Si es posible realizar el diseño que se solicita. II. El menor número de módulos necesarios para realizar el circuito con las especificaciones requeridas es 4 módulos RAM de 128 Kpalabras x 16 bits/palabra y 2 módulos ROM de 128 Kpalabras x 16 bits/palabra. A) I si, II si B) I: si, II no C) I no, II si D) I no, II no Página 7 Diseño de mapas de memoria Junio del 2004 2ª Semana Se dispone de 3 módulos de memoria con entradas de selección activa a nivel bajo. Dos módulos son de 8K palabras y el tercero de 32 K palabras. Estos módulos de memoria van a estar direccionados por un procesador que posee un bus de direcciones con 16 líneas (A15-0). Se requiere que los circuitos de 8K ocupen las direcciones de memoria menores y las mayores, y que las palabras de direcciones sobrantes se repartan en dos áreas del mismo tamaño. A) (2 puntos) Proponga un mapa de memoria que utilice los tres módulos con las especificaciones indicadas anteriormente. Diseñe un circuito que realice ese mapa. B) (2 puntos) Indique el módulo de memoria y la posición en dicho módulo que se activa con cada una de las siguientes direcciones (A15-0, en hexadecimal):0123, 2345, 4567, 6789, 89AB, ABCD, CDEF, EF01. Solución: Este problema es similar a problema 2-6 del texto “Problemas de Estructura y Tecnología de Computadores”, 2ª edición. Se recomienda consultar la solución a este problema con el fin de facilitar la comprensión de las explicaciones dadas a continuación. A) Mapa de memoria y circuito. 16 Descomponemos las 64K direcciones del bus de direcciones (2 ) en grupos de 8K, cada uno de los cuales está definido por uno de los posibles valores de A15, A14 y A13. La Tabla 1 muestra la solución con las especificaciones dadas en el enunciado: el módulo de 32 K debe ocupar forzosamente las posiciones intermedias (ya que no se puede “partir” un módulo de memoria físicamente) para que, estando los dos módulos de 8K situados en las direcciones mayores y menores, las palabras de direcciones sobrantes se repartan en dos áreas del mismo tamaño. Como M1 y M2 son de 8K, para direccionar una palabra dentro de estos módulos se necesitan 13 líneas de dirección (a12-0). En el caso de M3, de 32K se necesitan 15 líneas (a14-0). Se supone que los tres circuitos tienen de señal de selección CSM 1 , _ CSM 2, _ CSM 3, A partir de la Tabla 1, se sigue que las señales de selección son: CSM 1 = A15 i A14 i A13 ⇒ CSM 1 = A15 + A14 + A13 CSM 2 = A15 i A14 i A13 ⇒ CSM 2 = A15 i A14 i A13 CSM 3 = ( A15 i A14 ) + ( A15 i A14 ) ⇒ CSM 3 = ( A15 + A14 ) + ( A15 + A14 ) Página 8 Diseño de mapas de memoria CSM 1 , _ CSM 2, _ CSM 3, a partir Se dan dos soluciones para la habilitación de los módulos de memoria con las señales de las funciones anteriores. La primera (Figura 1) utiliza un decodificador. La segunda (Figura 2) es un diseño a nivel de puertas. Figura 1. Lógica de selección de módulos utilizando un decodificador Figura 2. Lógica de selección de módulos utilizando puertas Las líneas de dirección de M1 y M2 (a12-0) se conectan directamente a las líneas A12-0. Para M3 se necesitan 15 líneas Ai. En principio hay dos soluciones (en todo caso además de A13-0 hay que utilizar A15 ó A14): a 14-0= A14-0 ó a14-0= A15A-13-0 Se elige la primera solución (Figura 3), pues es la que cubre el mapa de memoria. Figura 3. Lógica de direccionamiento B) A partir de las direcciones A15-0 que se nos indican se tendrán que deducir los valores de A15, A14 y A13 para determinar si se selecciona algún módulo y cuál es. También se tiene que analizar los valores de las líneas de dirección del módulo seleccionado (a12-0 para M1 y M2; a14-0 para M3) para determinar qué dirección interna es la que se activa. En la Tabla 2 se muestran los resultados de dicho análisis: Página 9