Arquitecturas Paralelas Parte A

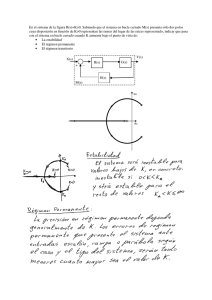

Anuncio

Universidad del País Vasco Facultad de Informática Dpto. de Arquitectura y Tecnología de Computadores Arquitecturas Paralelas Examen de Junio 18 – VI – 2003 El examen consta de dos partes, A y B. En la primera se trabajan conceptos básicos de la asignatura, y en la segunda se plantea un problema más largo. Evaluada cada parte en 10 puntos, la nota del examen será la mejor de: - considerando todo el examen 0,7 A + 0,3 B - considerando sólo la primera parte 0,8 A En todo caso, es necesario sacar más de 3 puntos de 10 en la parte A para aprobar la asignatura. Parte A 23 cuestiones — 2,5 horas — 7 puntos (u 8) Se trata de resolver las cuestiones que se plantean y, en su caso, escoger la respuesta adecuada de entre las que se ofrecen (rodear con un círculo). Utiliza para la respuesta el espacio asignado a cada pregunta; aunque no es necesario, si necesitas más, utiliza la parte trasera de la hoja. En todo caso, las respuestas deben ser precisas. Algunas preguntas valen 2 puntos (el número de la pregunta va en negrita) y otras 1 punto (el número en cursiva). En total, son 34 puntos. Las respuestas equivocadas no quitan puntos, pero sólo se tomarán en consideración las que provengan de una determinado cálculo o razonamiento; es decir, no se valorará simplemente el escoger una solución. En general, las respuestas se considerarán sólo como mal o bien. 1. Se ejecuta la operación entre vectores C = (A + 1) × (B + 2) en un procesador vectorial, cuyo reloj es de 500 MHz, y se obtienen los siguientes parámetros: N1/2 = 50 y R∞ = 750 Mflop/s. En base a ello, calcula el tiempo de ejecución de la operación anterior con vectores de 128 elementos. a. 474 ns b. 356 ns c. 306 ns d. 712 ns e. ninguna de ellas 2. En un determinado programa, el 80% de las operaciones se ejecutan en modo vectorial y el 20% restante en modo escalar. Para la longitud concreta de los vectores que se procesan, el rendimiento vectorial es de 800 Mflop/s, mientras que el cálculo escalar es 10 veces más lento (K128 = 10). Obtén el rendimiento real esperado (Mflop/s). a. 160 b. 656 c. 640 d. 286 e. ninguna de ellas 3. Completa la siguiente tabla de ejecución de un programa vectorial, en una máquina que permite encadenamiento de instrucciones. Las flechas de la tabla indican dependencias de datos entre instrucciones. instr. 1 instr. 2 instr. 3 instr. 4 t inicio 3 4 lat. UF. 3 5 4 6 1. dato 6+1 9+1 N. dato 6+N 9+N 4. Analiza este bucle y dibuja su grafo de dependencias. do i = 1, 100 (1) A(i) = B(i-1) + B(2i+3) (2) B(2i+1) = C(i+1) enddo 5. Escribe el código vectorial para la parte que consideres vectorizable del bucle anterior, incluyendo los registros VL y VS. A y B indican la dirección del primer elemento, el 0, de cada vector. 6. Analiza las dependencias del siguiente bucle, en el que las matrices son de tamaño NxN y están almacenadas por filas. En base a ello, puede concluirse que: do i = 0, N-2 do j = 0, N-1 A(i+1, j) = A(i+1, j+1) + B(i, j) B(i+2, j) = C(i, j) + 3 enddo enddo a. el bucle no puede vectorizarse entero, pero si cada instrucción por su parte, haciendo fisión. b. sí se puede vectorizar, y el paso (stride) de los vectores debe ser 1. c. sí se puede vectorizar, y el paso de los vectores debe ser N. d. dadas las dependencias en filas y columnas, lo más eficiente es vectorizar por diagonales (sin dependencias). e. ninguna de las respuestas anteriores es correcta. 7. Una máquina SMP de 3 procesadores utiliza el protocolo MSI para mantener la coherencia. Indica qué acción debe producirse para que se efectúe una transición M → S en un bloque dado, y completa las dos tablas con datos que reflejen dicha transición (las tablas representan el contenido y estado de un determinado bloque de dos palabras en las tres caches y en memoria principal). palabra 1 palabra 2 estado palabra 1 palabra 2 MC(P0) MC(P1) MC(P1) M MC(P2) MP estado MC(P0) S MC(P2) 3 4 situación inicial MP acción situación final 8. Una determinada aplicación se ejecuta en dos procesadores y tiene el siguiente comportamiento: P1 wr A 20 veces P1 wr B 10 veces P2 rd B P2 rd A Las variables A y B comparten el mismo bloque, que inicialmente está cargado en ambos procesadores. Las palabras son de 8 bytes y los bloques son de 8 palabras. Calcula el tráfico de datos que se producirá al ejecutar el programa, si el protocolo de coherencia es (a) de invalidación (b) de actualización. 9. Un procesador dispone de instrucciones LL/SC para efectuar operaciones de sincronización. Escribe las funciones de lock (entrada a una sección crítica) y unlock (salida) utilizando la técnica de tickets / turno. 10. En relación a la instrucción Test&Set, a. Test-and-Test&Set es una instrucción atómica que reduce el tráfico generado en la entrada a una sección crítica cuando hay alta contención. b. temporizar los intentos de entrada a una sección crítica (back-off) siempre reduce los tiempos de espera en la entrada. c. en casos de baja contención, la mejor solución es temporizar los intentos de entrada a la sección crítica con un tiempo de espera de tipo exponencial. d. Test-and-Test&Set reduce el tráfico generado a la entrada de una sección crítica porque reduce el número de invalidaciones de bloques de cache. e. todas las respuestas son correctas. N −1 11. Se reparte entre 4 procesos la ejecución de la siguiente operación: B(i ) = A(i ) × ∑ A( j ) . j =0 Se quiere ejecutar en paralelo tanto la operación de suma de los elementos del vector como la actualización de todos los elementos del vector B (con N = 4000 elementos). Escribe (alto nivel) el código que ejecutará el proceso 0, incluyendo las funciones de sincronización adecuadas. Supón que el scheduling es estático y que el trozo de vector que procesa el proceso 0 va de 0 a 999. 12. La distancia media y el diámetro (d / D) de una red Omega de 16 procesadores son: a. 3 / 4 b. 4 / 4 c. 2 / 4 d. 3 / 3 e. ninguna de ellas 13. Los enlaces de dicha red son de 4 Gbit/s; por tanto, el throughput máximo en la red podría alcanzar: a. 12 Gbit/s b. 64 Gbit/s c. 128 Gbit/s d. 32 Gbit/s e. ninguna de ellas 14. Para el caso de una red Omega de 8 procesadores, la permutación Pi → P(i+2) mod 8 a. no puede efectuarse sin conflictos. 0 0 b. no puede efectuarse sin conflictos, pero podrían usarse 1 1 nodos intermedios. 2 2 c. no puede efectuarse sin conflictos, pero podrían usarse 3 3 bufferes. 4 4 5 5 d. puede efectuarse sin conflictos, pero no es conveniente 6 6 por cuestiones de eficiencia. 7 7 e. ninguna de las respuestas anteriores es correcta. 15. Se envía un paquete de 64 bytes (1 flit de cabecera, flits de 8 bits) a un nodo a distancia 8. El tiempo de transmisión en la red, en condiciones de tráfico 0, ha sido de 300 ns. Procesar el paquete en cada router intermedio cuesta 2 ns. Calcula la velocidad de transmisión de los enlaces de la red, si la transmisión ha sido en modo cut-through. a. 0,5 Gbit/s b. 4 Gbit/s c. 14,4 Gbit/s d. 2 Gbit/s e. ninguna de ellas 16. Las características más deseables de la red de comunicación de un sistema paralelo son: a. latencia alta para paquetes largos y corta para paquetes cortos, junto con un throughput lo más bajo posible en ambos casos. b. baja latencia y alto throughput, en general. c. latencia y throughput proporcionales a la distancia, es decir, escalables. d. capacidad de mantener un nivel de tráfico proporcional a la latencia e independiente del throughput. e. todas las respuestas son correctas. 17. Sobre encaminamiento adaptativo: a. en condiciones de tráfico nulo, ofrece mejores resultados que el encaminamiento estático. b. permite detectar fallos en la red. c. es más costoso de implementar en cada router. d. sólo es adecuado para topologías que no presenten ciclos, como las mallas o los árboles. e. todas las respuestas son correctas. 18. El procesador P1 de un MPP tipo Origin 2000 de 4 procesadores ejecuta una operación de lectura en una variable que no tiene en la cache, y que corresponde al espacio de memoria sito en P2. Dibuja en el esquema cómo se resuelve el problema indicando los mensajes que se envían y de qué tipo son. Completa las tablas indicando el estado por el que pasará el bloque. 1. Rd P1 P2 P1 P2 P3 P4 en memoria cache I I I M estado inicial P3 P4 en el directorio en MP (en P2) estado bits de presencia estado final inicial final 19. Un procesador de un sistema NUMA-Q tiene un bloque en la cache en estado head–dirty. El propio procesador efectúa una escritura en una variable de dicho bloque. Las acciones a realizar son: a. b. c. d. e. avisar al home para que pase a gone (como consecuencia de la escritura) y efectuar Purge. hacer simplemente Purge. Roll-out, List Construction y Purge. Roll-out, List Construction, avisar al home para que pase a gone, y Purge. ninguna de las respuestas anteriores es correcta. 20. El estado final del bloque, en cache y en memoria principal, será: a. b. c. d. e. only–dirty / home head–dirty / gone only–dirty / fresh head–fresh / fresh ninguna de las respuestas anteriores es correcta. 21. Paraleliza el siguiente bucle sin utilizar funciones de sincronización. do i = 1, 100 (1) A(i) = C(i-1) + 1 (2) C(i) = B(i) * 2 (3) D(i) = C(i) + 3 enddo 22. Paraleliza el siguiente bucle de la manera más eficiente posible; caso de ser necesario, utiliza contadores para sincronizar. do i = 1, 100 (1) A(i+15) = C(i) + 1 (2) B(i) = B(i) + 1 (3) C(i+15) = A(i) * 2 enddo 23. Escribe código paralelo para el siguiente bucle, utilizando planificación dinámica por trozos de tamaño 4 (chunk scheduling). do i = 1, 1000 realizar_cálculo_iteración(i) enddo /* una función o procedimiento */ El bucle citado se ejecuta entre 5 procesadores. Todas las iteraciones son independientes entre sí, y, en media, el coste de una operación de planificación es un 50% del coste del cálculo de cada iteración. Sin considerar otros problemas, ¿qué factor de aceleración (speed-up) puede esperarse al ejecutar el bucle? a. 6,1 Parte B b. 4,4 c. 5 d. 3,3 e. ninguna de ellas 1 hora — 3 puntos Un multiprocesador de memoria compartida está compuesto por 64 procesadores que utilizan un hipercubo como red de comunicación. Cada procesador dispone de 2 MB de memoria principal y 256 kB de memoria cache, con bloques de 128 bytes. La coherencia de los datos se mantiene mediante un directorio distribuido en las caches (tipo NUMA-Q). En un momento determinado, el procesador P7 efectúa una escritura en una variable que no tiene en la cache, y que corresponde al espacio de memoria asignado a P32. Dos copias de dicho bloque se encuentran en P24 (head/fresh) y P56 (tail/valid). 1. Calcula el tamaño total, por nodo, que ocupa el directorio en el sistema. Los estados de los bloques ocupan 2 bits en MP y 6 bits en MC. Explica de manera detallada mediante un grafo cómo se resuelve el fallo en cache en P7 en lo que al mantenimiento de la coherencia respecta. Indica claramente los mensajes que se intercambian, su contenido y los cambios de estados. 3. Tomando en cuenta el mensaje inicial que se dirige desde P7 al directorio, indica los routers intermedios por los que pasará dicho mensaje. El encaminamiento es DOR (de mayor a menor dimensión). Para ese mensaje, y en la hipótesis de que pudiera utilizarse encaminamiento adaptativo, calcula cuántos caminos diferentes hay en la red para poder ir desde el origen (P7) al destino (directorio). 4. Calcula el tiempo necesario para completar la operación en P7. Para ello, ten en cuenta los siguientes datos: - comunicación: store-and-forward - enlaces de la red de comunicación y flits de los paquetes de 1 byte - velocidad de transmisión entre routers: 4 Gbit/s - tiempo de procesado en routers intermedios: 5 ns - longitud de los paquetes: con un bloque de datos, 132 bytes; resto: 4 bytes - tiempo para responder a un mensaje en los nodos destino: 50 ns - tráfico nulo en la red Considera ahora que la red no está vacía; de hecho, cada nodo está inyectando en la red 200 500 MB por segundo. 5. Calcula el tráfico máximo (aleatorio) que puede inyectar cada nodo de la red (MB/s) y, a partir de ese dato, el % del tráfico máximo que se está inyectando en ese momento. La gráfica adjunta indica cómo se incrementa la latencia de un paquete con el tráfico. En base a la mima, obtén el incremento esperado en el tiempo de comunicación debido al tráfico, y, finalmente, el tiempo total de la operación en P7. latencia (ns) 2 400 300 200 0 10 20 30 % tráfico máximo 40