Desp - 2

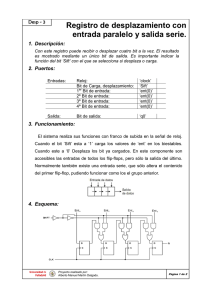

Registro de desplazamiento con

Entrada serie y Salida paralelo.

1. Descripción:

Este registro trabaja con 4 bits donde sólo la entrada del primer flip-flop y la

salida del último son accesibles externamente. Se emplean como líneas de

retardo digitales y en tareas de sincronización.

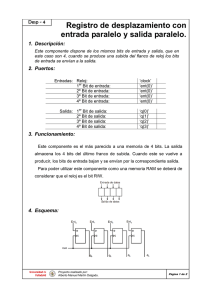

2. Puertos:

Entradas: Reloj:

Bit de entrada:

Salida: 1erBit de salida:

2º Bit de salida:

3º Bit de salida:

4º Bit de salida:

‘clock’

‘ent’

‘q0’

‘q1’

‘q2’

‘q3’

3. Funcionamiento:

El sistema esta formado con la combinación en serie de flip-flop D. El

sistema con cada subida de reloj adquiere un valor del bit ‘ent’ desplazando

los bit almacenados, (en este caso 4 bit’s). La salida muestra el valor de los

cuatro biestables a la vez.

4. Esquema:

Universidad de

Valladolid

Proyecto realizado por:

Alberto Manuel Martín Delgado.

Página 1 de 2

5. Ejemplo:

En el registro de desplazamiento se introduce tan sólo un bit en el

segundo periodo de reloj. Este va recorriendo cada una de las

salidas en los distintos flancos de subida de ‘clock’.

6. Cuestiones:

•

•

Propón algún ejemplo de la vida real en el que se utilize este tipo de

registro.

Diseña este registro de desplazamiento con biestables JK.

Universidad de

Valladolid

Proyecto realizado por:

Alberto Manuel Martín Delgado.

Página 2 de 2

0

0