Apuntes para el diseño de un amplificador multietapas con TBJs

Anuncio

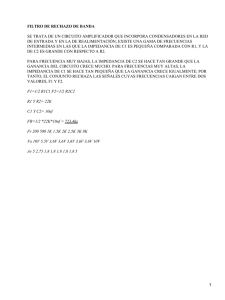

Apuntes para el diseño de un amplificador multietapas con TBJs Autor: Ing. Aída A. Olmos Cátedra: Electrónica I - Junio 2005 - Facultad de Ciencias Exactas y Tecnología UNIVERSIDAD NACIONAL DE TUCUMAN Diseño de un amplificador multietapas con TBJ Para explicar el diseño de un amplificador multietapas de audio, se planteará un problema: Se desea amplificar la señal de salida de auriculares de un discman para excitar parlantes. Para ello se usará un pre-amplificador de audio, el que excitará una etapa amplificadora de potencia. Se solicita el diseño de la etapa preamplificadora, la que deberá tener las siguientes características: Amplitud de la señal de entrada 50 [mV Ganancia de tensión Av ≥ 100 Impedancia de entrada Zin ≥ 5 KΩ Impedancia de salida Zout≤ 50Ω Frecuencia de corte inferor fL< 20Hz Frecuencia de corte superior fH>30 KHz Resolución: Como se necesita una ganancia mayor a 100, seguramente se necesitará más de una etapa para lograrlo, puesto que los amplificadores de ganancia grande son inestables. Por este motivo, se debe pensar en colocar dos etapas idénticas en cascada para lograr que la ganancia total sea mayor a 100, como lo solicitado, y una tercera etapa cuya impedancia de salida sea chica. Entonces, el diagrama de bloques total será: Elección de la fuente de alimentación: Para comenzar con el diseño se elegirá el valor de la tensión de la fuente de alimentación, con el siguiente criterio: Como la señal que excitará el amplificador es de 50mV y se solicita que la ganancia sea de 100, entonces el valor de pico de la señal de salida será: 100 x50 10−3 [V ] = 5 [V ] ; La tensión sinusoidal de salida, se desarrollará alrededor del punto de polarización VCE, el límite superior estará dado por el valor de VCC y el límite inferior por la tensión de saturación de colector – emisor VCE SAT. Esto se puede observar en la figura de abajo: AAO Electrónica I - Página 2- FACET-UNT En base a lo arriba descrito, entonces la tensón de fuente deberá ser mayor o igual que el doble de la tensión de pico. O sea : VCC ≥ 2 x5 [V ] ≥ 10 [V ] Por lo tanto se adopta: VCC = 12 [V ] Cálculo de la primera etapa A continuación se elige una configuración de amplificador. Se propone: Esta configuración es elegida por sus conocidas características de estabilidad y linealidad. Las características principales de esta configuración son: Ganancia chica e impedancia de entrada y de salida grande. AAO Electrónica I - Página 3- FACET-UNT Para comenzar el diseño de la etapa amplificadora propuesta, se elegirá el elemento activo. Para ello se tendrá en cuenta el rango de frecuencia en el que debe trabajar. En base a ello se elige el BC548B, cuyos parámetros son: β = hfe = 330, hie = 3200Ω, hre = 0; 1/hoe= 0Ω. A continuación se adoptará: VRC = 6[V]; para garantizar máxima excursión de salida IC = 5 [mA]; ya que IC máx = 200[mA] según hojas de dato Con estos dos valores se calcula R3 : R3 = VR3 = 1.2K Ω IC Cálculo de la ganancia de la primera etapa Como se solicita que la ganancia total del pre-amplificador es de 100 y se conoce que el tipo de configuración elegida es muy estable pero su ganancia no es muy grande, entonces, se deberá poner dos etapas idénticas en cascada, para que ganen como mínimo 100 entre ambas. Por lo tanto cada una de ellas, debe ganar como mínimo 10 veces o 20dB. Se calcula la ganancia de esta etapa. Para ello se dibuja el modelo para pequeñas señales: En él se puede ver que: VS = ib . hie + ie . R4 = ib . hie + (1 + h fe ) . ib . R4 = ib . hie + (1 + h fe ) . R4 VS ≈ ib . hie + h fe . R4 Esta aproximación: 1 + h fe ≈ h fe ; se puede realizar ya que hfe >>1 VO = iC . R3 = h f e . ib . R3 AAO Electrónica I - Página 4- FACET-UNT (1) AV = −iC . R3 ib . hie + h fe . R4 = −ib . h fe R3 ib . hie + h fe . R4 = − h fe R3 hie + h fe . R4 ≈− R3 R4 Por lo tanto, se adopta: AV = − R3 R > −10 ⇒ R4 < 3 10 R4 ⇒ R4 = 100Ω A continuación se plantea la malla externa: (2) VCC = I p . ( R1 + R2 ) I p ≥ 10. I B I p ≥ 10. IC β ≥ 151.5 [ µ A] Como: I p R2 = VBE + I C R4 reemplazando por el valor de Ip, se obtiene: R2 ≤ 8580Ω , por lo tanto adopto R2 = 7200Ω Reemplazando en (2) se obtiene: R1 = 72000Ω Esta etapa debe excitar a otra etapa idéntica por lo tanto el modelo es: AAO Electrónica I - Página 5- FACET-UNT Como se observa, la impedancia de entrada de la segunda etapa es la carga de la primera y por lo tanto influirá en el cálculo de la ganancia de la primera etapa, ya que se pone en paralelo con la resistencia que está en colector R3. Al realizar el modelo híbrido de la primera etapa cargada, este queda: Por esto, es imprescindible calcular la impedancia de entrada de la segunda etapa, pero como la primera y la segunda etapas son idénticas: Zi1= Zi2. Del modelo híbrido: Vs is ( R1 // R2 //( hie + (1 + h fe ) R4 )) Zi = = is is Reemplazando por los valores correspondientes, se obtiene: Zi = 5700Ω Como se dijo, esta impedancia, se pone en paralelo con R3 y la ganancia de la primera etapa queda: R // Z i AV =≈ − 3 R4 Al realizar los cálculos: AV =≈ −9.9 Cálculo de la segunda etapa La segunda etapa, será excitada por la salida de la primera etapa. A esta, no es necesario calcularla ya que será idéntica a la primera, pero la ganancia será distinta por que la carga de esta etapa es distinta, a ello se volverá luego de diseñar la tercera etapa. Cálculo de la tercera etapa AAO Electrónica I - Página 6- FACET-UNT La tercera etapa debe proporcionar una impedancia de salida baja, su ganancia no es importante ya que el requisito de ganancia será cumplido por la primera y la segunda etapa. Por esto se elige la siguiente configuración: Para el diseño de esta etapa, se trabajará con el mismo elemento activo que en las anteriores. Se adopta: VCE = 6[V] IC =5 [mA] R7 = 1200Ω Se plantea una malla: VR 6 = VBE + VR 7 = 0.7 + 6 = 6.7[V ] Como las corrientes de colector son iguales en las tres etapas, las corrientes de polarización también los serán: R6 = R5 = VR 6 = 44 KΩ Ip VCC −V R 6 = 35 KΩ Ip Una vez calculados los componentes del circuito es necesario calcular la impedancia de entrada, para recalcular la ganancia de la etapa 2, y la impedancia de salida a fin de verificar lo solicitado. Para el cálculo de la ganancia de tensión y de la impedancia de entrada, se realiza el modelo del circuito: AAO Electrónica I - Página 7- FACET-UNT Cálculo de la ganancia de tensión: Av 3 = (1 + h f e )ib R7 Vo = ≅1 VS hie + (1 + h fe ) R7 ib [ ] Cálculo de la impedancia de entrada: Z i 3 = R5 // R6 //[hie 3 + (1 + h fe ) R7 Z i 3 = 13.4 KΩ Cálculo de la impedancia de salida: Para ello, se coloca un generador VO en la salida, de amplitud conocida y se cortocircuita la entrada ya que en ese nodo había un generador de tensión. Zo = Vo Io io = ib + ie + ib h fe Vo = ib .hie 3 = ie .R7 Reemplazando en io: io = (1 + h fe + hie 3 )ib R7 Reemplazando en Zo: AAO Electrónica I - Página 8- FACET-UNT h R7 ie 1+ h ib .h ie fe Zo = = hie h 1 + h fe + ie ib R7 + 1 + h fe R7 Calculando: Z o = 9.7Ω Por lo tanto se verifica lo solicitado en el enunciado Cálculo de la ganancia total: Con el valor de la impedancia de entrada de la tercera etapa se calcula la ganancia de la etapa 2. Se recuerda que este es caso es idéntico al planteado para el cálculo de la ganancia de la etapa 1. AV 2 = − R3 // Z i 3 R4 AV 2 = −11 Por lo tanto la ganancia total del pre-amplificador será: AV = AV 1 . AV 2 . AV 3 = 108.9 = 40.74dB Se observa que se cumple con el requisito de ganancia. Cálculo de los capacitores de desacople Para el capacitor de entrada el circuito que se ve es: Cs y Zi1 configuran un filtro pasa alto, que la señal senoidal Vs debe pasar. La característica aproximada de este filtro es: AAO Electrónica I - Página 9- FACET-UNT Como se dijo, VS es una señal senoidal cuyas frecuencias están comprendidas entre 20 Hz y 30 KHz. Debido a la respuesta del filtro las frecuencias altas no tendrán problema en sobrepasarlo, pero las bajas sí. Por ende, se debe diseñar el filtro para que la mínima frecuencia pase, o sea: f mín ≥ f c donde fmín=20 Hz Como: τ c= CS .Zi1 = Entonces: Cs ≥ Se adopta: 1 ωc 1 2 π Z i1 f mín Cs = 10 µF El capacitor de desacople, ubicado entre las etapas 1 y 2 será de idéntico valor al ya calculado, por que Zi1= Zi2. El capacitor de desacople ubicado entre las etapas 2 y 3 también será igual. Con esto concluye el diseño del preamplificador. El circuito total queda: AAO Electrónica I - Página 10- FACET-UNT 2.2.- Excite el circuito con una señal senoidal Vs = 0.05 [V] y frecuencia de 1 KHz. Obtenga la curva AV vs f. Verifique el rango de frecuencia en el que el amplificador puede operar. Al realizar el barrido en frecuencia del pre-amplificador se obtienen los siguientes gráficos: En el gráfico de amplitud se observa que: La ganancia es de 40 dB en la zona de planicie Los puntos de media potencia (-3dB) están en aproximadamente en 5Hz y 2MHz, los que determinan el ancho de banda. Dentro de este rango no existirá distorsión de frecuencia. AAO Electrónica I - Página 11- FACET-UNT En el gráfico de fase, se observa que la fase es de 360º, en el intervalo de 40 Hz a 400 KHz. Quienes determinan el ancho de banda son principalmente los capacitores de desacople y el elemento activo. Para analizar la influencia de los capacitores se cambiarán en el circuito por otros de menor valor. Si se cambia el capacitor de entrada por uno de valor 1µF, se obtiene: En el gráfico de ganancia se observa que la frecuencia de corte inferior aumentó a 30Hz, mientras que la de corte superior se mantiene en 2 MHz. En el gráfico de fase se ve que la fase es de 360º desde los 300Hz hasta los 400 KHz aproximadamente. En ambos gráficos la variación se dio en las frecuencias inferiores. Si se realiza una variación de este capacitor desde 0.1µF a 10µF, se obtiene: AAO Electrónica I - Página 12- FACET-UNT Se nota en el gráfico de ganancia que cuanto menor es el capacitor de entrada mayor es la frecuencia de corte inferior, mientras que la frecuencia de corte superior no sufre modificaciones puesto que ésta es fijada por el elemento activo. Si se cambia además los otros dos capacitores, de acople, por 1µF, y se mantiene el de entrada en 10µF, se obtiene: Se observa que el valor de estos, influye de la misma manera que el capacitor de entrada, aumentando el valor de la frecuencia de corte superior y por lo tanto disminuyendo el ancho de banda. 2.3.- Calcule y mida los valores de Zin y Zo. Los cálculos de impedancia de entrada y de salida se realizaron en los puntos anteriores. Los valores calculados fueron: Zi = 5700Ω y Z o = 9.7Ω Si se realiza un gráfico de la impedancia de entrada en función de la frecuencia, se logra: AAO Electrónica I - Página 13- FACET-UNT Loas valores obtenidos son próximos a los calculados. Si se cambian los capacitores por otros de valor 1µF, la gráfica cambia de la siguiente manera: Donde se ve, que la impedancia cambió en el rango de las frecuencias bajas. En cuanto a la impedancia de salida, el gráfico es: Se observa que efectivamente esta es pequeña, del orden de los 9Ω, según lo medido y en concordancia con lo calculado. AAO Electrónica I - Página 14- FACET-UNT