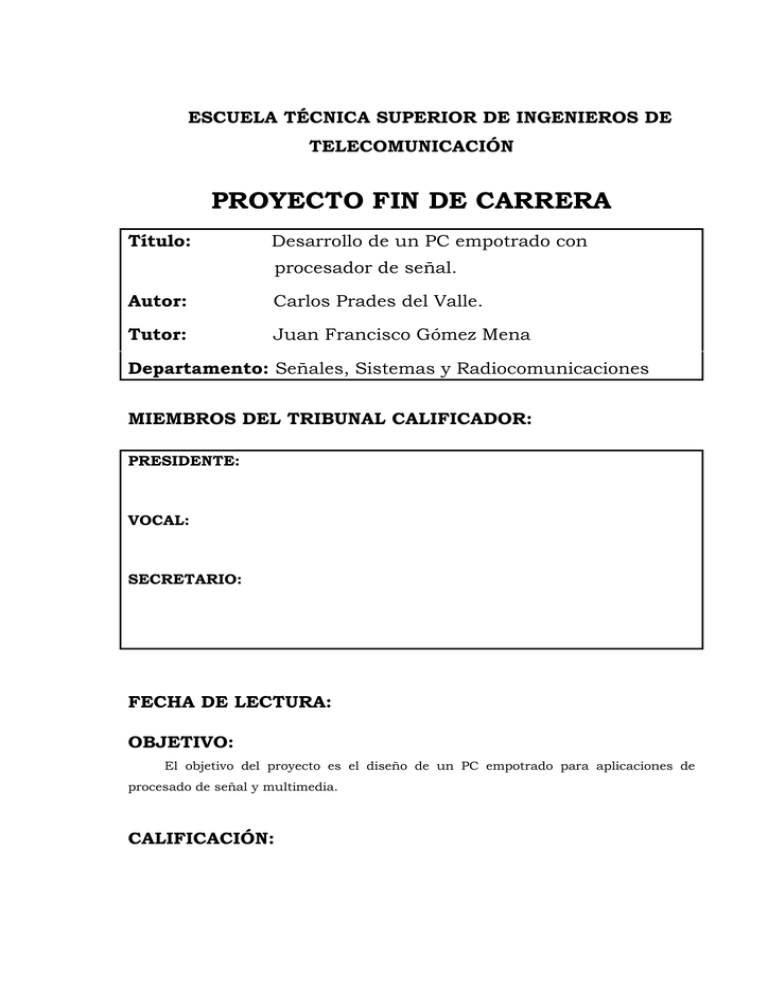

Desarrollo de un PC empotrado con procesado de señal

Anuncio