Ecuaciones Transistor MOS

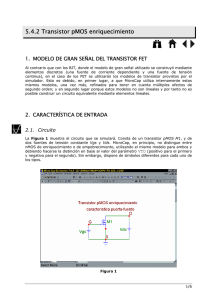

Anuncio

Ecuaciones Transistor MOS Rev. 1.0, Fernando Silveira, Mayo 2008 Parámetros generales: µ: Movilidad de los portadores (electrones para nMOS y huecos para pMOS) Cox: Capacidad del óxido por unidad de área (igual a εox/tox, siendo εox la constante dieléctrica del óxido y tox el espesor del óxido) W: ancho del canal L: largo del canal β = μ.Cox . W L Vt0: tensión umbral a tensión source sustrato nula δ: parámetro de linealización del efecto de sustrato; ((1+δ) también es denominado λ y n). Electrónica 1 – Facultad de Ingeniería – Universidad de la República Página 1 de 6 Ecuaciones Referidas al Sustrato, transistor nMOS Variables: VG: tensión gate – sustrato VS: tensión source – sustrato VD: tensión drain – sustrato ID: corriente drain – source Magnitudes auxiliares: VP: tensión de “pinch‐off” (también denominada tensión de saturación VDSAT) dada por: VP = VG − Vt 0 1+ δ Zona de Corte: I =0 D Condición: VS ≥ VP ⇔ VG ≤ Vt 0 + (1 + δ ).VS ) Zona Lineal: (1 + δ ) 2 2 ⎤ I = β ⎡(V − V )( D ⎢⎣ G t 0 . VD − VS ) − 2 VD − VS ⎥⎦ ( ) Condiciones: VS < VP ⇔ VG > Vt 0 + (1 + δ ).VS ) VD < VP Zona Saturación: ID = β 2(1 + δ ) (VG − Vt 0 − (1 + δ ).VS )2 Condiciones: VS < VP ⇔ VG > Vt 0 + (1 + δ ).VS ) VD ≥ VP Electrónica 1 – Facultad de Ingeniería – Universidad de la República Página 2 de 6 Ecuaciones Referidas a la Source, transistor nMOS Variables: VGS: tensión gate – source VSB: tensión source – sustrato VDS: tensión drain – source ID: corriente drain – source Magnitudes auxiliares: Vt : tensión umbral con tensión source sustrato VSB , dada por: V t = Vt 0 + δ .VSB VDSSAT: tensión de saturación drain source dada por: VDSSAT = VGS − Vt 1+ δ Zona de Corte: I =0 D Condición: VGS ≤ Vt Zona Lineal: I = β ⎡(V − V ).V − (1 + δ ) V 2 ⎤ D t DS DS ⎥ ⎢⎣ GS 2 ⎦ Condiciones: VGS > Vt VDS < VDSSAT Zona Saturación: ID = β 2(1 + δ ) (VGS − Vt )2 Condiciones: VGS > Vt VDS ≥ VDSSAT Electrónica 1 – Facultad de Ingeniería – Universidad de la República Página 3 de 6 Transistor pMOS En un transistor pMOS en conducción todas las tensiones tienen signo contrario al caso del nMOS (VG, VD, Vs, VGS, VDS, VSB) y también la corriente ID pues ésta circula en sentido contrario (de source a drain) al caso del nMOS. La tensión umbral Vt0 es negativa. Una manera sencilla de obtener las ecuaciones del transistor pMOS es usar las del transistor nMOS invirtiendo las tensiones involucradas (como se muestra en la tabla siguiente) y considerando para Vt0 el valor absoluto. De esta manera se obtendrá una corriente ID positiva que representa a la corriente de source a drain. Variable usada en ecuaciones nMOS Variable a usar en su lugar para obtener las ecuaciones del transistor pMOS a partir de las ecuaciones del transistor nMOS VG=VGB VG=VBG VS=VSB VS=VBS VD=VDB VD=VBD VGS VSG VDS VSD VSB VBS Tabla 1 Utilizando este criterio se escriben a continuación las ecuaciones del transistor pMOS Electrónica 1 – Facultad de Ingeniería – Universidad de la República Página 4 de 6 Ecuaciones Referidas al Sustrato, transistor pMOS Variables: VG: tensión sustrato‐gate (VBG) VS: tensión sustrato‐source (VBS) VD: tensión sustrato ‐drain (VBD) ID: corriente circulando de source a drain Magnitudes auxiliares: Vt0: valor absoluto de la tensión de umbral para VBS = 0. VP: tensión de “pinch‐off” (también denominada tensión de saturación VDSAT) dada por: VP = VG − Vt 0 1+ δ Con estas definiciones valen las mismas ecuaciones que para el transistor nMOS. Electrónica 1 – Facultad de Ingeniería – Universidad de la República Página 5 de 6 Ecuaciones Referidas a la Source, transistor pMOS Variables: VSG: tensión source – gate VBS: tensión sustrato – source VSD: tensión source – drain ID: corriente circulando de source a drain Magnitudes auxiliares: Vt0: valor absoluto de la tensión de umbral para VBS = 0. Vt : tensión umbral con tensión sustrato – source VBS , dada por: V t = Vt 0 + δ .VBS VSDSAT: tensión de saturación source‐drain dada por: VSDSAT = VSG − Vt 1+ δ Con estas definiciones valen las mismas ecuaciones que para el transistor nMOS, cambiando las variables según se muestra en la Tabla 1. Zona de Corte: I =0 D Condición: VSG ≤ Vt Zona Lineal: I = β ⎡(V − V ).V − (1 + δ ) V 2 ⎤ D SD ⎥ ⎢⎣ SG t SD 2 ⎦ Condiciones: VSG > Vt , VSD < VSDSAT Zona Saturación: ID = β 2(1 + δ ) (VSG − Vt )2 Condiciones: VSG > Vt VSD ≥ VSDSAT Electrónica 1 – Facultad de Ingeniería – Universidad de la República Página 6 de 6