¿QUÉ ES LA MEMORIA CACHÉ?

Anuncio

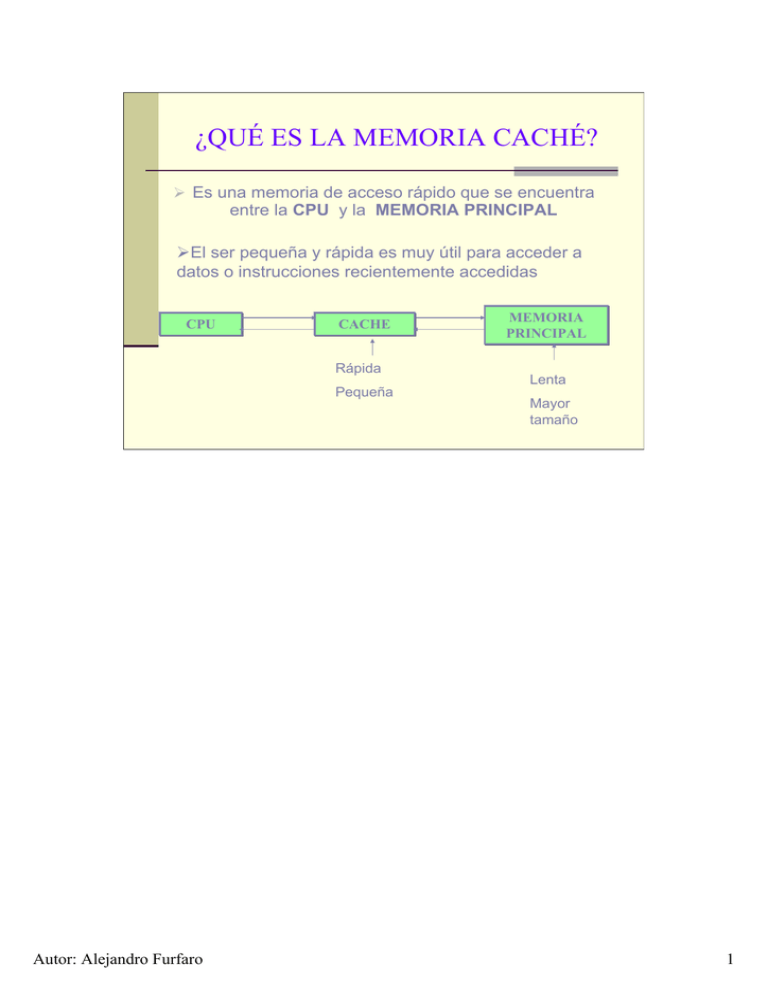

¿QUÉ ES LA MEMORIA CACHÉ?

¾ Es una memoria de acceso rápido que se encuentra

entre la CPU y la MEMORIA PRINCIPAL

¾El ser pequeña y rápida es muy útil para acceder a

datos o instrucciones recientemente accedidas

CPU

CACHE

Rápida

Pequeña

Autor: Alejandro Furfaro

MEMORIA

PRINCIPAL

Lenta

Mayor

tamaño

1

Principio de localidad de

referencia

LOCALIDAD

TEMPORAL

MUY PROBABLE

REPETIR

INSTRUCCIONES

Autor: Alejandro Furfaro

LOCALIDAD

ESPACIAL

MUY PROBABLE

EJECUTAR

INSTRUCCIONES

CERCANAS

2

Ejemplo de localidad espacial

Autor: Alejandro Furfaro

Principio de localidad espacial:

espacial Si un ítem es referenciado, es

altamente probable que se referencie a los ítems vecinos a éste.

Ejemplo: Algoritmo de convolución

for (i = 0 ; i < 256 ; i++ ){

suma = 0.0f;

for (j = 0 ; (j <= i && j < 256) ; j++)

suma += v0[i-j] * v1[j];

fAux[i] = suma;

}

i, j, suma, se utilizan a menudo. Por lo tanto si se mantienen en el

cache, el tiempo de acceso a estas variables por parte del procesador

es óptimo.

3

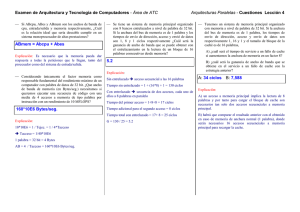

Cómo se realiza una operación

Lectura de Memoria

Inicio

CPU envía señal

de lectura

Hit!!

Busca ítem

en cache

Busca ítem en

cache y envía a

la CPU

Miss

Busca ítem en

memoria del

sistema

Escribe ítem en

el cache

Actualiza

directorio cache

Envía ítem a la

CPU

Fin

Autor: Alejandro Furfaro

4

¿Qué es el hit rate?

El tamaño de la memoria cache debe ser:

Suficientemente grande para que el procesador resuelva la

mayor cantidad posible de búsquedas de código y datos en

esta memoria asegurando una alta performance

Suficientemente pequeña para no afectar el consumo ni el

costo del sistema.

Se dice que se logra un hit cuando se accede a un ítem (dato o

código) y éste se encuentra en la memoria cache.

En caso contrario, se dice que el resultado del acceso es un

miss.

Se espera un hit rate lo mas alto posible

hit rate =

Autor: Alejandro Furfaro

Cantidad de accesos con presencia en Memoria Cache

Cantidad total de accesos a memoria

5

Práctica

¿Cómo se mide la efectividad de la caché?

Tiempo medio de acceso a la memoria

Tacceso=Tacceso cachePacierto + Tacceso MP(1-Pacierto)

Ejemplo:

Dados

Tacceso MP=500ηs ; Tacceso cache=50ηs; Pacierto=0.99

Caculo el tiempo de acceso con cache

Tacceso=50 ηs* 0.99 + 500 ηs *0.01= 54.5 ηs

¿Es efectivo que tenga cache?¿Mejora?

¿En cuánto?

Indice de mejora= 54.5 ηs / 500 ηs = 9.19

Autor: Alejandro Furfaro

6

Estructura de Memoria Cache y

Memoria Principal

Línea: Elemento mínimo de palabra de datos

dentro del cache. Corresponde a un múltiplo del

tamaño de la palabra de datos de memoria.

Razón: Cuando se direcciona un ítem en

memoria generalmente se requerirá de los ítem

que lo rodean (Principio de vecindad espacial)

Autor: Alejandro Furfaro

7

Tranferencias

Cpu

(bytes)

palabras

Cache

Divida en lílíneas

Bloque

Memoria Principal

Está

Está divida en bloques

Qué se transfiere cpu-cache y entre cache-memoria principal

Autor: Alejandro Furfaro

8

Mapeo

Dado que hay muchas menos líneas en

cache que en memoria principal es necesario

un algoritmo para mapear bloques de

memoria principal en líneas de cache.

La elección de la forma de mapeo la impone

la manera en que la cache esá organizada.

Autor: Alejandro Furfaro

9

Organización de MEMORIA CACHE

Mapeo directo

Asociativa

Asociativa por conjuntos

A continuación se verán cada técnica seguida de un

ejemplo especifico, que tiene los siguientes

elementos:

Cache de 64 KB

Los datos son transferidos desde la memoria principal y la

cache en bloques de 4 bytes cada transferencia. (Entonces la

cache esta organizada en 2^14 lineas de 4 bytes )

La memoria principal consiste en 16 MB, con direccionamiento

a byte, 2^24 direcciones. O sea direcciones de 24 bits.

Autor: Alejandro Furfaro

10

Correspondencia Directa o Mapeo Directo

Esta es la técnica más simple

En cada linea pueden alojarse 4 palabras, en cada bloque de memoria principal

hay 4 palabras.

El mapeo se expresa i= j mod m

Donde i= nro de linea de cache; j bloque de memoria principal, m nro de lineas

de la cache.

Autor: Alejandro Furfaro

11

Ejemplo Cache Mapeo Directo

Autor: Alejandro Furfaro

12

ASOCIATIVA

Autor: Alejandro Furfaro

13

EJEMPLO: ASOCIATIVA

Autor: Alejandro Furfaro

14

ASOCIATIVA POR CONJUNTOS

DE N VIAS

Autor: Alejandro Furfaro

15

EJEMPLO:

Autor: Alejandro Furfaro

16

Políticas

Si el bloque está

está en

caché

caché

Si el bloque no está

está en

caché

caché

Traerlo de Memoria Principal

HIT

Polí

Política de ubicació

ubicación

F. de correspondencia

Polí

Política de sustitució

sustitución

¿Donde se ubica?

Si la caché

caché está

está llena

¿Dónde se ubica?

Es una escritura

Autor: Alejandro Furfaro

17

Políticas de sustitución

Algoritmos de reemplazo del contenido de la

memoria cache

LRU: Least Recently Used.

Autor: Alejandro Furfaro

Se corresponde con el principio de vecindad

temporal.

LFU: Least Frecuently Used

FIFO

18

Recomendados

Stalling, William. Computer Organization and

Architecture. Fifth edition. Prentice Hall.

Tanenbaum, Andrew S. Organización de

computadoras : un enfoque estructurado (4ª

Ed) Prentice Hall; 2000

Autor: Alejandro Furfaro

19