ArqSpartan3_TC_2016.pdf

Anuncio

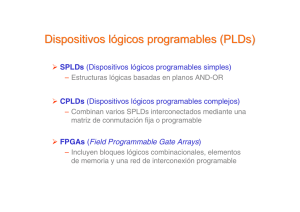

Departamento de Sistemas e Informática Arquitectura Spartan 3 2016 Evolución de los Dispositivos Lógicos Reconfigurables Primera generación: PLD -PLA (Programmable Logic Array) -PAL (Programmable Array Logic) -GAL (Generic Array Logic) Segunda generación: -CPLD (Complex Programmable Logic Device) Tercera generación: -FPGA (Field Programmable Gate Array) Estructura básica de la PLA Plano AND programable Plano OR programable Estructura básica de la PAL Plano AND programable Estadisticamente : mayoría de las funciones lógicas ocho implicantes primos esenciales reducción del chip Plano OR fijo menos capacidades parásitas más velocidad Una Gal es básicamente … PAL reemplazando el fusible por una celda CMOS eléctricamente borrable registros buffers 3 estados CPLD (dispositivo de lógica programable complejo) Consiste, esencialmente, de una serie de GALs, interconectados por una matriz de interconexión programable. CPLD (Complex Programmable Logic Device) Principales característica de un CPLD Utiliza tecnología E2PROM Bloques idénticos (Logic Blocks) para generar una función combinatoria con posibilidad de salida registrada. Matriz compleja de interconexión (PIM) con gran flexibilidad en la configuración interna Interface serie especial con propósitos de programación y test en fabrica y por el usuario. Implementación de lógica de baja a mediana complejidad Densidad Baja a Media Bajo costo, retardos predecibles, bajo consumo. (vs. FPGA) FPGA (Field Programmable Gate Arrays) Hoy día, es un arreglo de un conjunto de elementos: • Bloques de entrada/salida • Bloques lógicos • Memorias • Microprocesadores • Gestores de reloj • Multiplicadores • DSP • Interconexión reconfigurable • Otros FPGA: ideas básicas FPGA Componente estándar re-reconfigurable por el usuario. Esto implica: Interconexión reconfigurable. Función lógica reconfigurable. E/S reconfigurable. Tres tipos de FPGA No volátil, programable una vez (anti fusible) No volátil, reprogramable (flash). Volátil (SRAM) FPGA: ideas básicas … bloques lógicos “islas” rodeados por un “mar” de interconexiones programables. FPGA: ideas básicas CLB CLB Slew Rate Control Switch Matrix D CLB Input Buffer Interconexión programable C1 C2 C3 C4 H1 DIN S/R EC S/R Control DIN G Func. Gen. SD F' H' EC RD 1 F4 F3 F2 F1 H Func. Gen. F Func. Gen. Y G' H' S/R Control DIN SD F' D G' Q H' 1 H' K Q D G' F' Vcc Output Buffer CLB Q G4 G3 G2 G1 Q Passive Pull-Up, Pull-Down EC RD X Configurable Logic Blocks (CLBs) D Delay I/O Blocks (IOBs) Pad Ventajas de las FPGA ► Son dispositivos reconfigurables. ► Bajo costo respecto a los ASIC (Application-Specific Integrated Circuit: Circuito a medida) ► Son útiles para realizar prototipos que luego serán llevados a ASIC. ► Al ser circuitos cableados, la “ejecución” de cada bloque es en paralelo, logrando altas velocidades de proceso. ► Permite diseños con particiones software/hardware ► Posibilidad de reconfiguración dinámica ► Mayor potencia operacional que los CPLD Más regular que el CPLD La estructura de un FPGA cPLD Diseños que manejan mayor cantidad de registros y transferencias de datos Implementan más eficientemente diseños con una parte combinacional más compleja Arquitectura Spartan (CLB) (IOB) Elementos básicos de la FPGA (Xilinx)- CLB Configurable Logic Block (CLB) Slice Logic Cell (LC) Elementos básicos de la FPGA (cont.) Logic Cell (LC) LC - LUT (Look Up Table) de 4 entradas - Multiplexor - Registro (Flip flop) Elementos básicos de la FPGA (cont.) LUT: Look Up Table Retardo constante, independiente de la función implementada Elementos básicos de la FPGA (cont.) Un Slice integra dos LC El Slice comparte algunas señales: – Clock – Clock Enable – Set/Reset La LUT se implementa con una memoria SDRAM, entonces se puede usar: – Como una LUT de 4 entradas – Como Memoria de 16x1bit – Como registro desplazamiento de 16 bits CLB-(Configurable Logic Block ) 2 Slice 1 CLB (Spartan 2) Funciones de 5 entradas implementadas con 2 LUTs Cada “slice” del CLB Slice puede implementar cualquier función de 5 entradas. Las funciones lógicas son mapeadas en las dos LUTSs. El multiplexor F5 selecciona una LUT A4 A3 LUT ROM RAM D A2 A1 WS DI F5 0 F4 X4 A4 F3 X3 A3 F2 X2 A2 F1 X1 A1 BX nBX BX 1 0 X5 WS DI D LUT ROM RAM 1 F5 GXOR G X Funciones de 5 entradas implementadas con 2LUTs X5 X4 X3 X2 X1 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 1 1 0 0 1 0 0 0 0 1 0 1 0 0 1 1 0 0 0 1 1 1 0 1 0 0 0 0 1 0 0 1 0 1 0 1 0 0 1 0 1 1 0 1 1 0 0 0 1 1 0 1 0 1 1 1 0 0 1 1 1 1 1 0 0 0 0 1 0 0 0 1 1 0 0 1 0 1 0 0 1 1 1 0 1 0 0 1 0 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1 0 0 0 1 1 0 0 1 1 1 0 1 0 1 1 0 1 1 1 1 1 0 0 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1 Y 0 1 0 0 1 1 0 0 1 0 0 1 1 1 1 1 0 0 0 0 0 0 0 1 0 1 0 1 0 1 0 0 LUT OUT LUT Sólo algunas funciones de cinco entradas … x1 x2 x3 x4 x5 y 0 0 - - 0 1 0 1 - - 0 1 1 0 - - 0 0 1 1 - - 0 1 - - 0 0 1 0 - - 0 1 1 0 - - 1 0 1 1 - - 1 1 1 1 x5 x1 x2 x3 x4 23 0 1 y Escalado de muxs en Spartan 3 Cada slice tiene un F5Mux y un FiMux (éste puede funcionar como F6/7/8Mux) Interconexión Tipo de líneas de interconexión: 1.Líneas de propósito general 2.Líneas directas 3.Líneas largas Líneas de propósito general Conjunto de líneas horizontales y verticales conectadas a una matriz de interconexión. Matriz de interconexión Líneas directas • Líneas de conexión directa entre bloques. • Implementación eficiente de redes entre CLBs e IOBs adyacentes. • Introducen retardos mínimos y no usan recursos generales Líneas largas •Líneas que atraviesan la FPGA de arriba abajo y de izquierda a derecha. • Permiten un fan-out elevado. •Acceso de una señal a un punto distante, con menos retardos que las conexiones de propósito general. • Líneas dedicadas. Recurso escaso, dedicadas para señales críticas ( reloj o señales de inicialización globales). Spartan 3 Spartan 3 4 Slice 1 CLB Un Configurable Logic Block (CLB) integra cuatro slices Configurable Logic Block (CLB) SLICEL: sólo lógica SLICEM: lógica y memoria Jerarquía de bloques Jerarquía de conexiones Local Routing comunica slices dentro del CLB y con otros CLB’s cercanos. La estructura básica de un SLICEL es de 2 LUTs de 4 entradas seguidos por 2 flip-flops D La estructura básica de un SLICEM es como SLICEL pero las LUTs se pueden utilizar como RAM o como un registro de desplazamiento. Familia Spartan 3 FAMILIAS DE SPARTAN 3 • Plataforma Spartan-3 – Alta densidad y cantidad de pines • Plataforma Spartan 3A- I/O optimizada • Plataforma Spartan 3E- Lógica optimizada •Plataforma Spartan 3AN – Con memoria no volátil flash •Plataforma Spartan 3ADSP – Con DSP dedicados Datos característicos de la Spartan-3E Características generales de la S-3 Dispositivos con capacidades entre 50K y 4M de puertas equivalentes (XC3S50, XC3S200, XC3S500, XC3S1000, XC3S1500 y XC3S4000) (la del laboratorio 500 K) Hasta 1.28Mbits de BlockRAM ( 360K) Rango de E/S: desde 124 a 784 pines para cada dispositivo (320) Gestión digital del reloj (DCM) Multiplicadores empotrados de 18x18bits para soportar aplicaciones de procesado de señal de altas prestaciones Soporte de núcleos procesadores como soft IPs (Xilinx 32-bit MicroBlaze y 8-bit PicoBlaze) Densidades de hasta 74.880 de celdas lógicas ( 10476) Frecuencia máxima de reloj de 326 MHz ( 50 MHz) Tasa de transferencia de hasta 622Mb/s ( 100 Mb/s), soporte de diferentes especificaciones estándares de E/S (LVDS, DCI, DDR) Lógica JTAG compatible con los estándares IEEE Cinco elementos funcionales programables Bloques de entrada/salida (Input/Output Blocks – IOBs) Bloques Lógicos configurables (Configurable Logic Blocks – CLBs) Bloques de memoria RAM (Block RAM) Bloques de multiplicación (18 bits x 18 bits) Gestores digitales de reloj (Digital Clock Managers – DCMs) Bloques de entrada/salida (IOB) Soportan flujo bidireccional Salidas configurables como TRI-STATE. Tienen una opción de inversión. Admiten transmisión de doble tasa de datos (DDR) Resistencias de Pull-Up y de Pull-Down programables Circuito de retención (Keeper) del último nivel lógico (cuida que el bus no flote cuando todos los drivers-Z se desconectan) Soportan 17 estándares de señales y 6 de señales diferenciales Control Digital de Impedancia (DCI) para coincidir con las impedancias de las líneas que llegan a la FPGA Posibilidad de registrar salida y/o entradas •Los pines en la Saprtan 3E se agrupan en cuatro bancos de I/O, en correspondencia con los lados del dispositivo •Cada banco tiene potencias y tensiones de referencia independiente en los pines. •La ubicación de los pines debe ser compatible con el banco seleccionado Digital Clock Manager (DCM) Delay-Locked Loop (DLL) : eliminación de sesgo (skew) Sintetizador Digital de Frecuencia (DFS) : divide/multiplica frecuencia Desplazador de fase (PS) : desfasa frecuencia El DCM realiza básicamente tres funciones: Eliminación del skew del reloj (desfasaje del reloj por retardo del ruteo). El flanco activo llega simultáneamente a todas las entradas de reloj de los elementos en la FPGA Síntesis de frecuencia. Puede generar, a partir de la señal de reloj de entrada, diferentes relojes de salida. Multiplica o divide por M/N. Con M = 2 a 32 y N = 1 a 32 Corrimiento de fase. El DCM puede producir desfasajes controlados de la señal de reloj Delay-Locked Loop (DLL) Delay-Locked Loop (DLL) T Δt T- Δt Bloques dedicados de memoria RAM 20 bloques de 18 Kbits de memoria RAM Relación de aspecto (bus datos vs. bus direcciones) de cada bloque configurable Estructura de doble puerto (líneas de control, de datos y de reloj independientes para c/puerto) Multiplicadores dedicados 20 multiplicadores embebidos de 18 bits de entrada y 36 bit de salida Aceptan datos en complemento a dos (18 bits con signo, 17 sin signo) Cada bloque de RAM tiene un multiplicador inmediatamente colocado y conectado Microprocesadores embebidos Combinando los bloques de lógica tradicional (lógica cableada) con microprocesadores embebidos y periféricos relacionados completa un SoC (Sistema en un chip) Virtex-II PRO y Virtex-4 incluyen uno o más procesadores en core hard (PowerPC) Alternativa, Spartan3 procesadores en core soft (PicoBlaze, MicroBlaze) ¿….?