Test del trabajo 2

Anuncio

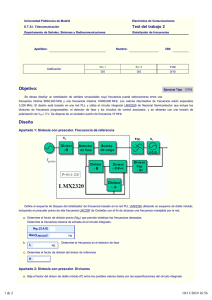

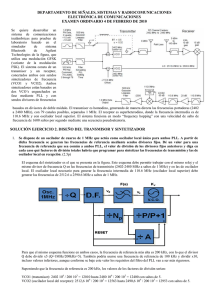

Universidad Politécnica de Madrid Electrónica de Comunicaciones E.T.S.I. Telecomunicación Test del trabajo 2 Departamento de Señales, Sistemas y Radiocomunicaciones Sintetizador de frecuencias Apellidos: Nombre: Calificación DNI: Sec. 1 Sec. 2 Total 0/5 0/5 0/10 Objetivo: Ejercicio Tipo 799588 Se desea diseñar un sintetizador de señales sinusoidales cuya frecuencia pueda seleccionarse entre una frecuencia mínima 15808,000 MHz y una frecuencia máxima 16464,640 MHz. Los valores intermedios de frecuencia están separados 24,320 MHz. El diseño está basado en una red PLL y utiliza el circuito integrado LMX2320 de Nacional Semiconductor que incluye los divisores de frecuencia programables, el detector de fase y los circuitos de control asociados, y se alimenta con una tensión de polarización de Vcc= 3 V. Se dispone de un oscilador patrón de frecuencia 160 MHz Diseño Apartado 1: Sintesis PLL con mezclador. Frecuencias de referencia Teniendo en cuenta la frecuencia más alta de trabajo del integrado sintetizador LMX2320, defina el esquema de bloques de un sintetizador que incluya en el lazo de enganche de fase un conversor de frecuencia con una frecuencia de oscilador fija. a. Proponga una frecuencia para el oscilador fijo del conversor (Fol), inferior a la frecuencia de salida. Determine la frecuencia máxima de entrada en el circuito integrado. FOL Max(fLMX2320) b. fr Determine la frecuencia en el detector de fase c. Determine el factor de división del divisor de referencia R Apartado 2: Sintesis PLL con mezclador. Divisores de frecuencia a. Elija el factor del divisor de doble módulo (P) entre los posibles valores dados por las especificicaciones del circuito integrado 1 de 2 10/11/2010 16:56 P [64,128] b. Determine los factores de división de los divisores programables A y B (N=P×B+A) para las tres frecuencias de diseño (mínima, media y máxima) fo 15808,00 MHz 16124,16 MHz 16464,64 MHz N A [0,1...127] B [3,4...2047] 2 de 2 10/11/2010 16:56