T527.pdf

Anuncio

ESCUELA POLITÉCNICA NACIONAL

DISEÑO Y CONSTRUCCIÓN DEL MEDIDOR DIGITAL DEL

FACTOR DE POTENCIA UTILIZANDO MICROPROCESAD.OR

TESIS PREVIA A LA OBTENCIÓN DEL TITULO DE

IN.GENIERO EN ELECTRÓNICA Y TELECOMUNICACIONES-

QUITO - ABRIL - 1 .983

"VI***

C E R T I F I C A C I Ó N :

Certifico que el presente

trabajo

ha sido realiza-

do bajo mi dirección por

el Sr .^Ay^reitHLo Andrade .

G.

A mi esposa

e hijos.

Í N D I C E

Pac

.,.,..,.,,,„

CAPITULO I.-

1

MÉTODO EMPLEADO EN LA MEDICIÓN DEL FACTOR

DE.POTENCIA

1 ..1. Definición del Factor de Potencia

1 .2

3

Instrumentos para la-medición del Factor de Poten-

cia

1 .3

........

5

'.

Procedimiento utilizado' para la obtención del- Factor Potencia..

,

5

CAPITULO II.- DISEÑO DEL MEDIDOR DIGITAL .DEL FACTOR DE

.'

2 .1

. ' POTENCIA

Diagrama de Bloques .

-..-..

7

2. 2

Lector de Corriente

8

2. 3

Lector de Voltaje

8

2. 4

2.5

2.6

Filtro .de Armónicos

*

Detector de Cruce por cero

'. .

15

Rectificador de precisión de onda completa

2.7

Conversor análogo digital

2.8

Microprocesador

2.9

Decodi-f icador- de direccionarniento

2.10. EPROM. . , . .'

2.11

9

19

.-

.

•

• 27

:....,.

.........

- . .31

-. '

34

Unidad de adaptación e interfase con periféricos

'2.11 .1 Descripción del

23

PÍA

'2.11 .2- Programación del PÍA'

2.11 .3 Aplicación en. el circuito

.'.

'

'; . . .

35

-

35

'.

38

.'

40

Pac

2.12

D1SPLAY

'

2.13

Fuente de Poder

CAPITULO III.-

•. . . .

. . .•

•

41

,

43

SOFTWARE DEL SISTEMA

3.1

Diagramas de flujo

45

3.1

3 - 1 . 1 Diagrama de Flujo para inicialización..

45

3 .1 .'2 Diagrama de Flujo de IRQ "-..

49

-

•. .

3.1.3 Diagrama de Flujo para NMI .."

•' 58

3 . 1 . 4 Diagrama de Flujo para cálculo de

:

( I p e I2

F

)

'

-

1F

H -I

2

'

' \n~~r

'63

3 . 1 - 5 Diagrama del Flujo para calculo de N-£ I

66

3.1..6 Diagrama'de Flujo para cálculo de .

\ i2

Ak I2

.. 1 F /

-.:...

. F

71

3.. 1 > 7 Diagrama de Flujo para cálculo del fac"• *

tor

de potencia en binario. . .'

•

74

3.1 .8 Diagrama de Flujo para convertir el resultado binario del factor de potencia,

en un valor BCD

.

77

3.'1 -9 Diagrama de .Flujo'para colocar en el

• '

DISPLAY el factor de potencia. . .3.2

80

Distribución de la RAM

CAPITULO IV--

.

83

EXPERIMENTACIÓN Y RESULTADOS

4.1

Procedimiento ... .

4.2

Construcción de la parte análoga

4-2.1 Filtros de 60 y 400

-.". ...'...

HZ

87

87

".

' 4.2.2 Detector de cruce por cero . . .'

.'. .

'

4-2.3 Rectificador de precisión de onda completa-

87

90

91

Pac

4-3

Construcción de la parte digital.

4- 4

Resultados

_. . .;

,

..

.

'

.. .

93

CAPITULO V.-

CONCLUSIONES 'Y RECOMENDACIONES

ANEXO No . 1

Desarrollo del Programa.

......

1 03

Diagrama General del Sistema

......

123

ANEXO No. 2.

. •

BIBLIOGRAFÍA."

, ...

92

100

Hojas de datos de los elementos, utiliza

.dos en. el Sistema

........,,, '

............

1 26

139

I N T R O D U C C I Ó N

Partiendo de el estudio "Factor de Potencia en circuitos con

Tiristores", Re£. (1), se planteó la necesidad de disponer de un sistema para la medición.del factor de potencia en cir_

cuitos en los que se tiene voltaje de la fuente puramente si_

nusoidal y corriente de forma arbitraria (la corriente sinusoidal es un caso particular), pero con periodicidad similar

a la del voltaje de la fuente.

,

Por la naturaleza de las señales .a pro.cesarse, el sistema" consta de parte análoga y digital, empleándose para el diseño de la primera amplificadores operacionales en circui'tos integrados, elementos que resultan- adecuados para el presente trabajo, tomando en cuenta que las frecuencias de las señales son bajas •-( 60 y 400 Hz).

.

La parte digital basa su operación en el microprocesador, el

mismo que'de acuerdo con el programa que se encuencra en .la

EPROM (memoria eléctricamente programable de lectura, única mente), realiza el control de los diferentes elementos del —

sistema y además procesa la información entregada por la par_

te análoga,' para la obtención del factor de potencia..

El presente trabajo se desarrolla en la siguiente forma:

En el primer capitulo se explica el fundamento-matemático

y

el procedimiento utilizado para la obtención del factor de -•'

potencia.

^^^*^^^^^^^'-^l^^f(^

E.n;-.el segundo capítulo se presenta el diagrama de. bloques, e'l

desarrollo teórico y diseñó de cada 'una de las. partes del sis_

tema. ' '

En el tercer _ capítulo se analizan cada uno de los diagramas de flujo empleados para el cálculo del factor de potencia.

En el cuarto capítulo se encuentra el. procedimiento utilizado

para-la construcción de el medidor del factor 'de potencia y los resultados obtenidos en la construcción de cada uno de

los -..bloques y del medidor en conjunto.

Sn el quin-to capítulo se presentan ' las conclusiones y Ia3 __ i

recomendaciones.

•

..

-

.

.

• .

1.

MÉTODO EMPLEADO EN LA MEDICIÓN DEL FACTOR/ DE POTENCIA

1.1. T- DEFINICIÓN DEL FACTOR DE POTENCIA

Independientemente de las formas de'onda, factor de potencia-es la relación que existe entre la potencia activa y la poten

cia

aparente-, -en un circuito . eléctrico.

'' . .'

FACTOR DE -POTENCIA •= fp = Potencia 'media (1.1)

. Potencia aparente •

D-e acuerdo 'coh los resultados obtenidos, ver Ref . (1) , el

fac_

tor'vtLe-. -potencia en circuitos con voltaje de •ifu.e&t'e . sinusoidal

y -onda de corriente arbitraria, e s : '

fp. = g . c o s 63. (-1.2)

/ 9

L/

Donde:

•Ig = -=^

Representa el contenido,.gue tiene la fuente de

componente de frecuencia fundamental, denomina,

da.aunque en forma no muy -Correcta FACTOR DE DISTORCION.

eos

'

FACTOR DE DESPLAZAMIENTO .'•( 9_

-

es el defas.aje-

entre la onda de voltaje y la 'componente funda-

mental de la corriente).

1.2.

INSTRUMENTOS PARA LA MEDICIÓN DEL FACTOR DE POTENCIA.-

Los sistemas .conocidos como medidores del factor de potencia,

miden únicamente la diferencia de fase entre voltaje y co

-

rriente, y después despliegan el"resultado en términos del coseno de este- ángulo.

El movimiento electrodinámico es utilizado como el mecanismo

sensor de la gran mayoría de medidores de el factor de poteri

cía.

1.3-

•

•

PROCEDIMIENTO UTILIZADO PARA LA OBTENCIÓN DEL FACTOR POTENCIA.-

De la ecuación 1.2 se desprende que los parámetros necesa

-

ríos para la medición del factor de potencia son: los valo res RMS de la corriente de la fuente y de. su componente fun'damental y el coseno del ángulo de la diferencia de fase entre el voltaje y la componente fundamental de la corriente.

La corriente se puede medir por medio de un transformador de

corriente o utilizando un SHUNT, los cuales dan una señal desalida proporcional a la corriente objeto de medición, siendo necesario además un circuito que obtenga

de esta muestra

la componente .fundamental de la corriente.

Él coseno del ángulo de la diferencia de fase entre el Volta

je y la componente fundamental" de la corriente, se calcula -

midiendo el tiempo existente entre el cruce por cero de la onda.del voltaje y el de la onda de la componente fundamen tal-de.la corriente.

C A P I T U L O

II

DISEÑO. DEL MEDIDOR DIGITAL DEL EACTOR DE POTENCIA

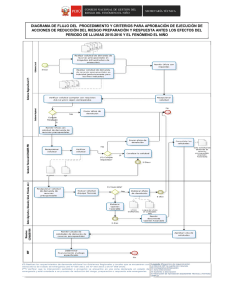

2.1.- DIAGRAMA DE BLOQUEAS

En: la- figura 2.1 se presentan las etapas necesarias pa . . ra la medición del factor de potencia. A continuación el

- .

'listado y una pequeña descripción de las mismas.

Un lector de voltaje que da una. muestra de el voltaje de

la red de alimentación.

- ;.

.

-

Un. lector de corriente que entrega una señal eléctrica -

;.:_",'>proporcional a la corriente que circula, por la línea.

Filtros pasabanda sintonizados a -60 KZ y 400 HZ', según •sea la frecuencia del voltaje de la red de alimentación.

-

Detectores de cruce por cero; uno para la muestra de

voltaje y otro para la'componente fundamental'de la corriente .

.

.

Rectificadores de precisión de onda completa para la co

rriente. de la fuente y para la componente fundamental de la corriente, de forma que llegue al conversor A/D,

únicamente señal análoga positiva.

Conversor análogo-digital

Lector de

corriente

Lector de

voltaje

Filtro de

Armónicos

Detector

:ruce-cero

Detector

cruce cero

PÍA

Rectificad

Precisión

Rectificad

Precisión

bus Ge clirecci<&a Conversor

A/D

Bus de datos '

DISPLAY

Decodifica

Dirección-'

Microproces

EPROM

Fig. 2.1.- Diagrama de bloques.

-

Microprocesador

Decodificador de direccionamiento

-

Memoria EPROM¡ encargada de almacenar la serie de instrucciones que ejecutará el microprocesador.

-

.Unidad de adaptación e interfase con periféricos (PÍA),

utilizado para manejar el display y para comunicar al microprocesador con.el" mundo exterior.

-

DISPLAY que presenta los datos de salida.

-

Fuente de poder.- Para la implementación de los Filtros

y rectificadores de precisión se utilizan amplificado —

res operacionales LM324,

los cuales pueden procesar s_e

nales menores o iguales al voltaje de polarización, menos 1.5 voltios. Los voltajes de polarización de los operacionales en este sistema son de +

5 voltios, por -

. lo que el valor máximo de las señales es de- -f

tios pico.

3.5 vol"

2.2.- LECTOR DE CORRIENTE

Para

la medición de la corriente 'se emplea un SHUNT

,-

-el mismo'que da una muestra de voltaje proporcional•a la corriente en circulación.

2.3-- LECTOR DE VOLTAJE

'. •• •

'

En la medición del factor de potencia no es necesario el verdadero valor del'voltaje, sino únicamente interesan los cruces por cero de la onda respectiva; la muestra del voltaje de la linea se toma por medio de un

transformador.

-

.

2.4- FILTRO DE ARMÓNICOS

Para la obtención de la componente fundamental de la cq

rriente se. emplea un filtro activo del tipo pasabanda bicuadrático, cuyo circuino se muestra en la figura 2.2.

Fia. 2.2.- Filtro activo pasabanda bicuadrático

El filtro escd compuesto por dos integradores A

y A3 y un

amplificador sumador Al., la función de transferencia y ecuaciones de diseño se presentan.a continuación:

• .

AVC =

vo

-r-

-SA

s2-[-SB -i- D

(2.1)

donde.-.A Ve = ganancia de voltaje del circuito como función de

la frecuencia.

1

R5C1

1 -i- R3/R4

-1 + .R1/R2

(2.2)

-1 + R3/R4

R1+ R2/R1

(2.3)

R5C1

R3

. 1 _

R4 - -R5-R6.C1.C2

D =

(2.4)

La frecuencia central del filtro está definida por:

1

2TT V.R4

1/2

(2.5)

R5.R6."C1.C2.

La ganancia del filtro a la frecuencia de resonancia H, está

definida por:

H=

R2

.6)

Los valores de R3 y R4 se calculan con la siguiente ecuación:

R3' = R4 =

2.7)

Estos" valores pueden ser seleccionados de la mitad a el doble

del

valor calculado.

'

.

•

Los valores de Cl y C2, se calculan con la siguiente ecuación

2.

Cl = 02 =

.De igual forma sus valores pueden ser seleccionados de la mi tad a el doble del. valor calculado.

Los OFFSET a la salida de A2 y A3 , se reducen haciendo:

R7 = R6

( 2.9.)

R8 = R5

( 2.10)

El valor de-Rl se calcula de:

Rl = R3

( 2.11)

Nota: .La descripción más detallada de las ecuaciones antes mencionadas, se lo puede encontrar en la referencia 2.

- DISEÑO -DEL FILTRO DE 60

Hz .

Requerimientos de diseño

£jií

(frecuencia central ) • =

60

H

(ganancia )

-i

Hz.

¿

Af

(ancho de banda)

=

C^V^* ^

2Hz

En primer lugar se calculan los valores de R3 y R4 utilizando la ecuación 2.7

R3 _ = R4

=-

1,66

M

Utilizando la 'ecuación 2.8 se tiene :

Cl = C2 '=

1.666 pF

Por medio de la ecuación 2.5 y haciendo R5 =-R6, se tiene:

R-5 '=• R6

•=

2 Tí f i Cl

R5 = R6

=

23653 M'-O .

En serie con R6 se'coloca un. potenciómetro d^w100 KCl(Pot 1)

para calibración de la frecuencia central del filtro ££>.

De Tas ecuaciones 2.9 y 2.10

se tiene:

R7

-

2,653 M.ri

R8

=

2,653 M.O-

',

'POr''medio de la ecuación 2.11 se tiene:

Rl

=

1.666 M£i

Utilizando la ecuación 2.6 se tiene:.

Rl := R2 = 1,666 M

Con el fin de dotar al circuito de un sistema de calibraciónde la ganancia se reemplaza R2 con un circuito T, como se -mue_s

tra en la figura -2.3.

Rz

Ry

Rx

Fig. 2.3 circuito T

La•impedancia equivalente del circuito T 'está determinado porla siguiente' ecuación:

Z21 =

RX.Ry+Ry.Rz+Rz\x

Rx

. (2.12)

Si se hace Rz = Ry se tiene:

.R2

=

Rx

=

2Rx.Ry+Ry

Rx

2

fídonde:

(2.13)

R2 - 2Ry

Asignando para Ry un valor de ipp KO, se obtiene que

Rx

=

12,5 K.O

DISEÑO DEL FILTRO DE 400 Hz .

Requerimientos de diseño:

H

Ai

=

12 Hz

Empleando el mismo procedimiento que en el caso del filtro de

60 Hz , se tiene que: .

.-' '

.

R3

= R4 = 250

.Cl

= .02== '250 PF

•R5

= R6 = 2,653 M_O

'

:

.

'

- •

Colocándose de la misma manera un potenciómetro de 100 KO Fot ,

i

'

• .

I1, e n serie c o n R 6 .

' . • " • ' _ .

Rl

=

- 250

Se reemplaza R2 ' con un circuito T, como el .descrito en el caso

de

60

Hz.-

.

.

•

•2.5

DETECTOR DE CRUCE POR CERO.-

Se selecciona un detector de cruce por cero no inversor con

histéresis, cuyo circuito se muestra en ía figura 2.4.

Vi

Vo

A4

DI

Fig. 2.4.- Detector de cruce por cero no inversor con histé

resis.

"1

La función de transferencia de éste detector se muestra en la

figura -2.5-

'

.

Vo

Vsat

Vi

-VD1

Fig. 2.5-'- Función de transferencia del detector de cruce

por

cero.

-.

Las ecuaciones de diseño de el detector se presentan a conti nuación"

r

R7

R7 +R8

AVI =

R7

.

Vsat-

(2.14)

VD1

(2.15) '

R7

Donde

AVI ' =

variación negativa desde cero en el voltaje• de entrada, necesaria para obtener .un cambio

del

AV2

=

;••

estado positivo al negativo,

•

•

variación positiva desde cero en el voltajede entrada, necesaria

para obtener un cam -

bio del estado ne.gativo al positivoVsat - Voltaje "de saturación del operácional (Vcc 15 5 Volt)..

'

El máximo error en los puntos de cambio antes

.

mencionados considerando- los parámetros de -en_

trada del operácional y asumiendo -Rl = R3 y -

Ri es :

Voff

=

+ (Vio + lio Rl)

. •

•'

(2.16)

;

;

El valor óptimo de RB para minimizar los efectos' de Vio e Ib

con la temperatura, se determina con:

R9 -

AVioAT

(2.17)

Las resistencias de entr-ada del circuito está determinado por:

Rin = R7 + RS'.Rid

RS-fRid

• -

(2.18)

DISEÑO DEL DETECTOR DE CRUCE POR CERO

En el sistema se emplean dos detectores de cruce por cero, uno

para la muestra de voltaje, el otro para la componente fundamen

tal de la-corriente, por las características

de las dos seña -

les; éstos dos detectores son realizados con idéntico criterio

de diseño.

REQUERIMIENTOS DE DISECO:

Voltaje positivo de salida (Vsat) = 3,5 V.

Voltaje .negativo' =

ÍAVll 4lAV2l' = 50 X 10

2 •

- 0,7 voltios

voltios

El operacional escogido es el -LM-747 que -tiene como caracterís

ticas:

AVío (25°C) = J

AT .

'

Alb

( 2 5 C ) = 1 , 3 nv\T

Con la e c u a c i ó n ^ 2 . 1 7 , se e n c u e n t r a q u e :

no

R9 =

R9 =

11-538

Con el objeto de minimizar- el error producido por la corriente de polarización

(Ib) se hace R7=R9-

Utilizando las ecuaciones 2.14 y 2.15 se obtiene

I AVI | 4- AV2 =

R7

R7+R8

(Vsat + VD1)

Con .un.voltaje Vcc = 5 voltios se tiene:

-IV-

. 11.538 (3,5+0,7)'V

= 11.538+R8

De donde:-

R8.. s 473>£6

La corriente máxima que puede entregar el operaclonal es rel_a

tivamente pequeña (2p mA), siendo ésta la corriente máxima de

circulación por el diodo, por lo que no es necesaria una re sistencia de protección para el mismo, ya que la disipación -

de potencia no alcanza valores críticos.

2.6.-

RECTIFICADOR DE PRECISIÓN DE ONDA COMPLETA.-

Debido a que el'conversor análogo, digital escogido acepta ú

nicamente voltajes análogos positivos, se requieren dos rectificadores de onda completa de precisión, uno para las mues_

tras de corriente de la fuente y otro para la componente Fun

damental.

Estos rectificadores de precisión deben operar con señales cuyas amplitudes pueden fluctuar entre + 3-5 voltios; su con.

ducción debe ser lineal y su comportamiento de un diodo ideal. Estas, características son prácticamente obtenidas por el

rectificador de precisión, que se muestra en la figura ¿.b .

Este circuito rectifica señales con voltajes pico de sólo

-

0.7V/AV ( AV = ganancia de lazo abierto del amplificador operacional), suponiendo un AV = 1000, una rectificación lí ne.al de precisión de una señal de 0.7 mV, es posible:

Fig. 2.6.- Rectificador de precisión de onda completa

£1 circuito de la figura está compuesto -de un rectificador in.

vertido con selección positiva (A5, R12, R13, R14, R15, o2-, • P3 ) ••.y/.áé 4fl_s¿.m-^— • de_.. gan age i a i gual_a_la_ unidad (A6, R10, Rll/ ^1^, Fot. 3) . . .

Las ecuaciones de diseño son las .siguientes :

a) Rectificador invertido

Voltaje de -ganancia

Vcl, para voltajes de entrada mayores

a

cero, está definido -por :

R13 Si

AVC1 • = ,

(2.19)

R12

.En -.el; caso" de voltajes menores -a cero se tiene:

AVcl = -0

Si Vi<

El valor oprimo dé -R15 con el fin de-minimizar el! voltaje

OFFSET"; de salida producido'por la corriente de B1AS Ib es

R15 -

E12.R13

R12+R13

(2.20 )

La.-resistencia de entrada del circuito es..prácticamente .igual'

a R12.

'

Rin =

b. -

Sumador'

-

R12

• ' - • • ' ' • • -

(2.21)

El amplificador sumador e-s simplemente un caso especial de -•

un. amplificador invertido,.dando una salida invertida iguala.la-suma algebraica de las dos entradas / sus ecuaciones de

diseño; 'se presentan a continuación:

VO . = - Rll

V

Vi'•+ V14

R10

R14

(2.22)

.voltaje de la.señal de entrada

V14 =• ' voltaje; a la salida del rectificador A5Para-obtener a la salida de A6, la'rectificación'de onda com

pleta-de la señal-y conociendo que "los ' voltajes sobre R10

y

Rl'4'son. iguales y opuestos, -se debe-tener:

•R14 =•

R10

(2.23)

A fin de minimizar -el voltaje OFFSET de error .'a la salida

se obtiene'R16 por medio de la siguiente ecuación:

•R16 =

R10.R11.R14

(2.24) '

RIO.R11+R10-R14+R11-R14•

- DISEÑO-DEL RECTIFICADOR DE PRECISIÓN DE ON'DA COMPLETA,

REQUERIMIENTOS DE DISEÑO:

a)' Rectificador invertido

Rin = 10'

,

VCl '= -1

Utilizando la ecuación 2.19 se tiene que:

1 =

R13

R12

. .R12 =

R13

Siendo la resistencia de entrada igual a R123- se tiene;

R12 =' R13 = '10KO-

Por medio .de/la ecuación 2.20

•R15 =

5KO.

'

se tiene:

'

•

b) Sumador..-

Para entradas negativas el sumador.A2 funciona -como un inver

sor de ganancia uno (V14=0); de acuerdo a la ecuación 2.22,

se 'tiene entonces:

Vo

Vi

Rll

R10

Rll

R10

T*:'

R10=

Rll

Se escoge un valor de R10 = Ril. 10K^_ , de forma que para

voltajes que lleguen a 5 voltios, la corriente de entrada al

sumador está en el orden de los 0 •, 5 n\A, permitiendo que losoperacionales del filtro trabajen cómodamente.

Por medio de la ecuación 2.23 se tiene:

R14 = 5K.Q. •

2-7

CONVERSOR ANÁLOGO DIGITAL.-

El conversor análogo digital escogido es el ADC0809 producido

por 'la 'NATIONAL SEMICONDUCTOR, conversor monolítico CMOS de o

cho BITS; dispone de ; 8 canales múltiplex de entrada, registro de direccionamiento y registro de tres, estados a la salida, tiempo .de conversión de 100/Useg. , además de fácil interfase con microprocesador.

Para su funcionamiento el A/D, requiere sólo de una fuen te de

-j-5 voltios, de un reloj, el mismo que es obtenido del micro procesador, y de voltajes de referencia positivo y negativo,

no pudiendo ser éste último menor de cero voltios.

Las características eléctricas, diagramas de bloque, de tiempo y método utilizado por el conversor A/D, se encuentra en el anexo 2.

La operación del A/D, se 'encuentra controlada por el micropro

cesador que de acuerdo con el programa que será explicado pos_

teriormente, indica cuándo, y el número de conversiones que se

debenrealizar.'

24

AD0809

.

NMI

/*

„/! •

w\'

[

De el Div.deFrec.

IN2 28

2 IN4

IÑÍ 2?

I

1F

3 IN5

IN0 26

IF

4 IN6

ADDA 25

5 IN7"

ADDB 24

—1

6 START ADDC 23

x

"V

R/W

E

1 IN3

\

:I±^>~

'

7 EOC . .ALE 22

-5 ' '-1

82"^

2

21

'D7

9 OE

D6

• . 2~2 20

.1É >CLOCKV

i.

^1

VMA . AD

D3

DI

2~3 19

D5

2~4 18

D4

-8 •

12 Vref+ 2

17

D0

13 GND 'Ref -- 16

-7

' -6

14 2 7 .2

15

D2

11 Vcc-

T

GN D

x

•

GND

Fig. 2.7 Diagrama de conexiones del coriversor A/D. •

En el presente sistema se utilizan dos de los ocno canales de

entrada de que dispone el A/D, IN0

y el INI, que corresponden

a código-de direccionamiento 000 y 001, respectivamente." Las-."

entradas de dirección B y C se conectan a cero lógico y .—

la - - ^

ejitrada de dirección A, está conectada al bus de datos D0,

siendo el microprocesador el que decide cuál de las entradas-es seleccionada; con un valor de D0 igual-a'cero lógico, -lacorriente de la fuente, y con- un valor 'de D0 igual a uno

—r-

25

lógico, la' componente fundamental de la corriente.

La dirección es introducida en el A/D con una transición positiva en la entrada ALE, la conversión de la muestra de corriente seleccionada se inicia con una transición negativa en la entrada START; aprovechando éstas condiciones se haceuso de un solo pulso para cumplidlas dos funciones, como se

puede observar en el diagrama -de tiempo de-' la figura 2.8a.

a.-.Ciclo de escritura

b.

Ciclo de lectura

ENABLE

VMA.AD

R/V

START, ALE

OE

Fig. 2.8.- Diagrama de tiempo de operación del A/D.

La señal de la entrada START, es el resultado de la combina ción lógica AND de las señales ENABLE, VMA, AD y

de

codificador de dirección se tiene la señal YMA.A'p'; del micrcH\¡

Luego:

26

—START = VMA.AD + ENABLE.R/W

(2.25)

Lógica que se muestra implementada en la Fig. 2.7

Una vez que termina la conversión el A/D produce en la salida

EOC una transición positiva, la misma que luego de ser invertida va al microprocesador, indicándole que termine lo que se

encuentre ejecutando y lea .el valor binario resultante de laconversión en el A/D. Esto hace que el resultado binario de la conversión sea puesto "en el bus de datos, de donde es leído por el microprocesador. El diagrama de tiempo de la figura

2.8b muestra la condición de cada una de las señales a utili zarse para la obtención del pulso para la entrada OE, -que re_s

ponde a la siguiente ecuación:

.OE =

VMA.AD'+ ENABLE. R/W

(2.26)

La raisma que se muestra implementada en la Fig. 2.7-

Las entradas de polarización Vcc y VRef+5. se encuentran cone£

tadas entre sí, dándose entonces un voltaje de referencia positivo de +5 voltios; el voltaje de referencia negativo estáconectado a tierra, con lo que las señales análogas de entrada podrán variar entre 0 y 5 voltios.-..

El reloj del A/D se obtiene dividiendo para dos la señal de ~

la salida ENABLE del microprocesador, lo cual da una frecuencia de aproximadamente 450

KHZ >

manteniéndose la velocidad de

conversión del A/D cercana a los 100 'I seg., de acuerdo a recomendaciones del fabricante (Anexo 2).

27

+5V

14 Vcc

1 CLR '

2 D

3 Q

Al A/D

(ir1 450K.HZ)

4 PR

5 CLK

ENABLE

( f 900KHz )

6 Q

.7 GND

SN7474

Fig. 2.9.- Divisor por dos.

2.8.- MICROPROCESADOR

El microprocesador escogido es el 6802, tiene un set de instrucciones exactamente igual al 6800, sistema de reloj Ínter

no y 128 BYTES de RAM, la misma que se utiliza para guardarlas constantes del programa durante la ejecación del mismo.

El 6802 es producido por MOTOROLA SEMICONDUCTORS, es total mente compatible con la familia del 68'00 diseñado especial mente para sistemas pequeños, de fácil interfase, y su costo

es relativamente bajo.

En la figura 2.10 se presentan las conexiones que se reali zan en el 6802 para acoplarlo al sistema.

28

D3

•^

U

_±

VCC

¿x

1

b-WU ^7

JL JL

1 (Tí

Det ; Cero L-pl Lj-i p^^

Dir.

A/D

^^

Ppcp-i-

2 HALT

4. T R O

5 -VMA

6 NMI

^

•7BA

/

¿

'

/

/

/

/

/

BUS

DE

DIRECCIONAM.

f

'

/

/

f

f

'

'

'

f

/

/

i

AD

2.2 UF

/

GND

EXTAL 39

? MR

K" .O I

Dec .

V c: c:

YTAT, ^H

'

p\

E ^7

. RE

36

"VCC

^

. •

PÍA.

JL II IÍ

^.

^

A/D

VccS.35

[\, A/D

R /W ^ 4

8 Ver

Do ^

9 A0

D1 '32

1 0 A1

D2 31

il 1 A2 '

D3 32)

1 2 A3

D4 29

1 3 A4

D5 28

1 4 A5

'D6 27

1 5 A6

D7 26

1 6 A7

A1 5 25

1 7 A8

A1 4 24

BUS DE

1 8 A9

A1 3 23

DIRECC.

/

/

/

/

/

/

,

/

/

/

/

/

'

•

BUS DE DATOS

s

/

/

1 9 A1 0

/

A1 2 22 -^ /

20 Al 1

Vss 21

•Fig. 2.10. Diagrama de conexiones del microprocesador

29

A continuación se presenta una descripción de las conexiones'

de la Fig. 2.10.

- RESET.- Con un cero lógico en esta entrada el microprocesa dor se encuentra parado, con el cambio de.nivel a uno lógico,

el microprocesador va a las dos últimas direcciones FFFE y FFFF, de donde obtiene la dirección de la primera instrucción

a ejecutarse.

El cambio de nivel de cero a uno lógico debe producirse sin efecto de rebote, para lo cual se impleinenta el circuito

que

se muestra en la Fig..2.9-

EXTAL, XTAL.- Entradas a los que se conecta el cristal para el funcionamiento del reloj interno del microprocesador - ,

la frecuencia óptima es de 4MHz.; sin embargo se utiliza

un-

cristal de 3.579 MHz que tiene un costo bastante inferior y la variación en velocidad no es significativa.

Con el fin de prevenir oscilaciones a frecuencias múltiples ,

el fabricante recomienda conectar dos capacitores de los terminales del cristal a tierra, como se observa

en la figura -

2.10 .

-

ENABLE (E). Salida equivalente a la fase dos(jí2) del 6

RE.- Con el objeto de utilizar la memoria RAM interna, ésta

señal debe ser mantenida en uno lógico.

Vcc STAMDBY.- Se la utiliza si se desea mantener los datos de

30

memoria de los 32 primeros BYTES de RAM cuando el sistema es'

desactivado; esto se consigue conectando una pila a ésta en trada. Esta' entrada se encuentra conectada a Vcc.

R/W. En esta salida se indica si el 6802 está realizando la lectura o escritura en alguno de los periféricos; normalmente

se encuentra en uno lógico, colocándose en cero lógico únicamente durante el proceso de escribir.

D0-D7-- Estas entradas o salidas forman el bus de datos, ca paz de manejar hasta una carga TTL, el bus tiene datos siem pre que ocurra una escritura ó lectura con alguno de los peri_

féricos. La excepción se produce cuando los 128 BYTES de

RAM

internos son accesados, situación en la que el bus de datos siempre se configura como salida, aún cuando esté- leyendo.

A0-A15-- Estas salidas forman el bus de direccionamiento de 16 líneas, capaces de manejar hasta una carga TTL.

BA.- Esta salida se pondrá en uno lógico cuando se produzca u

na interrupción

HALT o que encuentre una instrucción WAIT en-

el programa.

BA' está conectada a la compuerta TRI-STATE, permitiendo el

-

paso de la señal del 'detector de cruce por cero del voltaje ,

a la entrada IRQ, únicamente cuando el raicroprocesador se encuentra en WAIT.

NMI.~ La interrupción NMI se produce con la transición negatjl

va en ésta entrada, interrupción utilizada para leer los va -

31

lores binarios de las muestras de corriente.

i

VMA.-Ocasionalmente el microprocesador está ocupado con operaciones internas y no utiliza el bus de direccionamiento

ó

de datos, sin embargo en los buses habrá algo durante este tiempo, con el fin de asegurar que ninguno de los periféri eos confunda estos datos con información válida; VMA se pone

en uno lógico únicamente cuando se encuentra una dirección -válida en el bus de direccionamiento.

IRQ.- La interrupción IRQ se produce con un nivel de cero lo

gico en ésta entrada; IRQ puede ser inhabilitada por medio de una instrucción en el programa.

MR.- Esta entrada se utiliza para' memorias lentas.

HALT.- Siempre que esta entrada se encuentre en cero lógico ,

el microprocesador se mantendrá parado, condición que no se u.

tiliza en el sistema,

2.9.- DECODIFICADOR DE DIRECCIONAMIENTO.-

Los 128 BYTES de RAM dentro del 6802, están controlados por .un

decodificador de direccionamiento que está también en el 6802.

Esta ocupa las' direcciones 0000 a 007F. La RAM es completamente decodificada, lo cual significa que ocupa éstas y solamente'

éstas direcciones.

La EPROM debe ser direccionada de forma que incluya las- direcciones FFFE y FFFF para la interrupción RESET corno se mencionó

32

en el capítulo anterior, la EPROM a utilizarse en nuestro sis_

tema es de 1K de extensión, debiendo por lo tanto estar contenida en las direcciones FC00 hasta FFFF.

Tomando en cuenta que el sistema no será expandido hasta ocu

-

par todas las direcciones, se puede realizar una decodificación

incompleta de ios periféricos, simplificando de esta manera

el

circuito de decodiFieación. Se debe tener sin embargo el cuidado de que el sistema de decodificación alcance para

todos

los

periféricos,

Siendo únicamente tres los periféricos con que cuenta el siste-

ma, (A/D. PÍA, EPROM) se puede pensar en un decodificador de do

a cuatro, sin embargo se quiere dejar un margen para una posi -

ble expansión del sistema para cumplir funciones de control, a-

demás de las medici.ones que realiza, razón por la que se escogi

un decodificador de 3/8 (74 LS138), el cual tiene una velocidad

de propagación de aproximadamente 20 nano segundos.

El 74LS138 dispone de tres entradas de selección llamados Gl, G2, G3; en éste caso se utiliza sólo una de las mismas. Para

que el decodificador funcione, es necesario que Gl esté en uno-

lógico mientras G2 'y G3 deberán estar en cero lógico; se coló -

can por tanto G2 y G3 permanente a tierra, manteniendo de éstaforma las dos -entradas en bajo y se conecta Gl a la señal de

salida VMA del microprocesador, así el decodificador es habili-

tado únicamente cuando el 6802 envía una señal de memoria válida (VMA).

'

33

Vcc

A1 3

1 A

Vcc 1 6 '

Al 4

2 B

Yo

15

A1 5

3 C

Y1

14

4 G3

Y2

13

5 G2

Y3

12

6000 - 7FFF

VMA

6 G1

Y4

11 -

8000 - 9FFF PÍA

ECÓ00-FFFE

7 Y7

Y5

10

A000 - BFFF A/D

EPROM

8 GND

Y6

9

0000 - 1 FFF-X ocupado en RAM

2000 - 3FFF ' i n t e r n a )

4000 - 5FFF

C000 - DFFF

GND

Fig. 2.11,- Diagrama de conexiones del decodificador

Las direcciones más significativas A15, A14, A13, se conéc tan a las entradas -0,3,y -A, respectivamente, como se observa

en la figura 2.11. El decodif icador tiene ocho salidas denomi.

nadas Y0 a Y7, correspondientes a- las ocho posibles combina ciones de A. B, y C. Cuando el decodificador está inhabilitado , todas estas salidas están en uno lógico, coloc.ándose en cero-lógico la salida

que sea seleccionada, dependiendo ésta

del número binario que se encuentre en las entradas, corres pendiendo el binario 000 a la salida 0 y así sucesivamente.

En este caso la salida depende de los tres BITS más significa

tivos del bus de direcciones. Para las direcciones que empiecen con 111 (que incluye las direcciones E000 a FFFF), la salida Y? se pondrá en cero lógico, que es la que seleccio-na la

EPROM; nótese que ésta ocupa 8'KB de direcciones cuando en

34

realidad su extensión es de 1K únicamente.

2.10 EPROLM

'Siendo la extensión .del programa de aproximadamente un KBYTE

(un poco menos), la memoria escogida es MM2758A, la misma

que -tiene una capacidad de 8192 BITS (1024

X 8), suficiente-

para almacenar el programa.

Las conecciones de la 2750 son simples,. además de fuente

(+5V) y tierra se conecta el bus de datos D0-D? y las 10direc_

c i o n e s menos significativas del bus de dirección, éstas últimas permiten seleccionar

lidades.

2

ó lo que es lo mismo 1024 loc_a

.

.

Las.salidas.de datos de la 2758 son del tipo "TRI-STATE", ob_

teniéndose la información de la memoria únicamente cuando

-

las entradas CE y OS simultáneamente están en cero-lógico .

CE es la entrada para habilitar la memoria, mientras OE es la habilitación de salida. Si solamente CE está en bajo,

la

ROM está habilitada y trabajando, pero los tres estados inter_

nos se encontrarán en alta impedancia, no pudiendo la información alcanzar el bus de datos.

"

Por otro' lado, si CE está en uno lógico,.el'integrado está i

nhabilitado y por lo tanto las salidas estarán también deseo

nectadas

Con las consideraciones

antes mencionadas, en este caso se -

coloca OE siempre en cero lógico, dejando que CE

realice to

35

do el trabajo, la señal CE viene del decodificador de direo

cionamiento.

.

• .

Dentro de la operación la memoria recibe una dirección y

la

señal CE colocando la información en el bus después de un

•-

cierto tiempo llamado tiempo de acceso, en éste caso el mismo es de 450 nano segundos, tiempo que es compatible con elsistema.

+ 5V

1 A7

/

/

'A8

23

3 A5

A9

22

4 A4

Vpp 21

5 A3

OE

20

6 A2

AR

19

7 A1

CE

18

8 A8

07

17

9 00

06

16

10 01-

05

15

/

11 02

04

14

^

GND

/

2 A6 '

Vcc 24

/

/

Bus de dirección

/

Bus de dirección

/

/

/

/

x

7

Del decodif icador

/

Bus de datos

/

/

/

/

/

/

/

.

Bus de datos

Fig. 2.12.- .Diagram.a de conexiones de la EPROM

2.11.- Unidad de adaptación e interfase con periféricos (PÍA)

2.11.1'. DESCRIPCIÓN DEL PÍA

Con el objeto de manejar el DISPLAY, recibir la información

36

dé los detectores de cruce de cero y del indicador de la fre

cuencia de trabajó, se escogió el PÍA (6821). Quedando ade más.la posibilidad de emplear el mismo en procesos de control,

en una futura extensión del proyecto.

El PÍA consta de dos secciones, cada una de las cuales dispone

de tres registros principales: el registro de salida (OR), elregistro de dirección de datos (DDR) y el registro de control

(CR).

El registro OR se emplea para, almacenar el BYTE de datos quees transferido del, ó al periférico, OR.

El registro DDR configura cada una de las lineas en el bus de

datos como entradas o como salidas', con uno lógico en uno délos BITS del DDR; la línea correspondiente del OR, actuará cq

mo salida y con un cero lógico como entrada.

El OR y DDR comparten la misma dirección, siendo el.estado del

BIT dos del CR el que indica cuál de los tres registros está habilitado.

Con un cero lógico en este BIT se habilita el DDR, con uno lógico el OR.

Las entradas RS0 y RS1 son las encargadas de decidir cual de los registros internos es utilizado durante la programación

-

por el 6802, por lo que se encuentran conectados a las direc ciones A0 y Al, respectivamente (Fig. 2.13).

37

^di:

1 VSS.

CA1

Dis a

2 PA0

CA2

b

3 PA1

IRQB 38

c

4 PA2

IRQA 37

d

5 PA3

RS0 :36

_Dir.A0

e

6 PA4-

RS1'

35

_DirA1

f

7 PA5

RESET34

RESET

. g

8 PA6

D0 .

33

9 PA?

D1

32

signo

10 PB0

D2

31

entero

11

D3

-30

decimal 1

1 2 PB2

D4

29

decimal 2

13 PB3

D5

28

decimal 3

14- PB4

D6

27

detector de 0 (voltaje_)_

1 5 PB5

D7

26

E

25

detecto:? cero (corriente)17' PB7

CS1

24

1 8 CB1

CS2

23

1 9 CB2

CS0

22

20 Vcc

R/V

21

dp

PB1

_selección (60,400) 1 6 PB6

+ 5V

10 KO.

39

Fig. 2.13. Diagrama de conexiones del PÍA

Bus de datos

ENABLE

DEL DECOD

R/W (6802)

38

Las lineas de control E (ENABLE) R/W y RESET están conecta das a' los mismos puntos en el 6802. Las salidas IRQA é IRQB,

no se utilizarán en el presente sistema.

Las entradas CS0 3 CS1 y CS2, se utilizan para seleccionar el PÍA. Para que el 6802 pueda accesar el PÍA, CS0 y CS1 de

ben estar en uno lógico y CS2 debe estar en cero lógico; en

éste caso CS1 y CS0 están conectados a +5 voltios, y CS2 es

manejada por el deco.dificador de direccionamiento.

Los datos entre.el microprocesador y el PÍA se transfierena través del bus de datos.

2.11.2.~ PROGRAMACIÓN DEL PÍA.

En este sistema como se puede observar en la figura 2.3, el

lado A y las líneas PB0 a PB4 del lado 3 del PÍA, se las

—

configura como salidas, las líneas PB5 a PB7, son utiliza das como entradas.

La configuración del PÍA permanece igual durante todo el

-

proceso, por. lo que la programación del mismo se la realiza

una sola vez en el curso de programa.

La línea RESET del PÍA como se mencionó se encuentra conectada a su similar en el 6802, con lo que al conectar el sis_

tema todos los registros del PÍA se ponen en cero lógico, quedando por lo mismo los dos buses de datos configurados como entradas, el BIT 2 del CR es también cero indicando

que la dirección común a los registros DDR y OR selecciona

39

en éste caso él DDR,

El sector de dirección asignado-al PÍA es 8000 - 9FFF y losregistros internos son seleccionados por medio de las direcciones A0 y Al, de acuerdo como se ve en la tabla 2.1.

Al

'

A0

BIT 2

Reg. Interno Selec

Rsl

RS0

CRA

CRB

0

0

1

X

0

0

0

X

DDRA

0

1

X

X

CRA

1

_0

X

1

ORB

1

0

X

0

DDRB

1

1

X

X

CRB

ORA

Tabla 2.1.

Las instrucciones

necesarias para inicializar el FIA'son

1

LDA

FF

Carga el acumulador A con FF

2

STAA

8000 Almacena FF en el DDRA _

3

LDAA

1F

4

STAA

8002 Almacena 1F en el DDRB

5

LDAA

04

6

STAA

8001 Almacena en el CRAÍ0O

7

STAA

8003 Almacena en el CRBÍÍ& )

Carga el acumulador A con 1F

Carga el acumulador A can 04

40

.Con la primera instrucción se coloca el valor FF en el acunm

lador A, valor que por medio de la segunda instrucción se

-

guarda en DORA, configurando de ésta forma el lado A como sa

lida.

La tercera instrucción carga el acumulador A con 1F, valor

que es almacenado en el DDRB, configurando las líneas PB0

-

PB4 como salidas y las lineas PB5-PB? como entradas.

Con la quinta instrucción se coloca en el acumulador A el nú

mero 04hexadecimal, valor que con las dos siguientes instruc

cienes es almacenado en los registros de control A y B, quedando de esta forma habilitados los registros ORA y ORB para

ser seleccionados con las direcciones 8000.y 8002 respectiva

mente, completándose la inicialización del PÍA.

2.11-3. APLICACIÓN EN EL CIRCUITO.-

•En el inicio del proceso de cálculo del factor de potencia el

PÍA es inicializado como se mencionó, leyéndose entonces la información que se encuentra en las líneas PB5, PB6,' PB7 co rrespondientes al detector de cruce de cero del voltaje, al interruptor que indica la frecuencia t de trabajo y al detector

de cruce de cero .de la fundamental respectivamente, informa ción que se lee como si se tratara de una localidad de RAM con dirección 8002 (ORB del PÍA).

El resto de líneas del PÍA, (PA0 - PA7, PB0-PB4) se utilizan

para realizar el DISPLAY del valor resultante del factor depotencia, colocando en el ORA del PÍA el código del DISPLAY-

41

de siete segmentos. Se utilizan inversores con colector abie.r

to para suministrar la corriente requerida por los DISPLAYS,-el lado B es utilizado para determinar cuál, de los DISPLAYS es seleccionado, como se observa en la Fig. 2.13-PB0 seleccio

na el DISPLAY del signo. PB1 del valor entero. PB2, PB3, PB4,

los tres dígitos decimales.

La selección de los DISPLAYS así controlada por el PÍA permite que los mismos se prendan y apaguen un gran número de ve ees en un segundo, dando la ilusión de estar siempre prendi 'dos, situación que permite un gran ahorro de energía.

El procedimiento empleado para la selección de los DISPLAYS se explica detalladamente en el desarrollo del programa en el

índice DISPLAY del resultado (3.1.9).

2.12.- DISPLAY.-

El DISPLAY utilizado es el MAN3640 de la fábrica Monsanto, es

I

¿j

del tipo de cátodo comuTi. El diagrama de conexiones se- puedeobservar en la £ig. 2.14-

El DISPLAY del signo tiene conectado únicamente .el segmento "g", ya que es el único que se utilizará del mismo, prendiéndose el LED en el caso de signo negativo, ó en blanco en el caso de signo positivo.

El DISPLAY del entero es el único que tiene conectado la entra

da correspondiente al punto decimal, ya que el resultado siempre aparece con un dígito entero (0 ó 1) y tres dígitos décima,

les .

42

LSB DECIMAL

PB4

PB3

PA0

pb2

PA7

PB1

PB0

Fig. 2.14-- Diagrama de conexiones del DISPLAY

43

El DISPLAY del entero y los. tres dígitos decimales tienen

-

conectadas las entradas a, b, c, d, e y g, llegando por tanto

la información del código de siete segmentos a todos los

DISPLAYS simultáneamente.

En el lado'B del PÍA se decide cuál de .los DISPLAYS es el que

debe encenderse con la información que al momento se encuen tra -en ORA. Operación que se realiza colocando uno lógico

en

la línea correspondiente del ORB, línea que se encuentra co nectada a la base de un transistor (1) saturando el mismo,

-

con lo que el colector se encuentra prácticamente a tierra, habilitando el DISPLAY- conectado al colector de éste transís tor.

El número de transistores necesarios es igual a cinco, utilizándose el arreglo CA3081N de la casa RCA, el mismo que consta de siete transistores de emisor común.

Nota (1) El lado B del PÍA puede ser utilizado para alimentar

corrientes superiores a ImA con un voltaje de 1,5 voltios para manejar directamente la base de un transistor (dato del fa

bricante)

2.13-- FUENTE DE PODER.-

Para la'alimentación del circuito es necesaria una fuente dual

de + 5 voltios. El circuito completo tiene un consumo de alre_

dedor de 5^¿ mA para la fuente de

-i- 5 voltios y de 50 mA pa-

ra los - 5 voltios; en la figura 2.15 se muestra el diagramade la fuente.

5V

110. Vac

4000 •

-o

-f •

:F

LM320

' Flg.' 2.15-- Diagrama de la fuente de poder

45

C A P I T U L O III

3--

SOFTWARE DEL SISTEMA

3.1.- DIAGRAMAS DE FLUJO

Cada uno de los parámetros•necesarios para el cálculo del

factor de potencia, indicados en el capítulo uno, es obtenido de acuerdo como se muestra en los siguientes diagramas de

flujo.

Los diagramas de flujo para la inicializacion

IRQ y NMI son-

descritos en forma detallada, correspondiendo el número

que

se indica en la descripción al número con que se tia clasificado cada bloque.

3.1.1.- DIAGRAMA DE FLUJO PARA INICIALIZACION. . (Fig. '3.1)."

Una vez que se produce la interrupción RESET, el proceso se^

inicia en el- bloque No. 1.

•

1.- En este bloque se inhabilita IRQ utilizando para ello

-

el MASK -BIT existente en el microprocesador, evitando se prcD

duzca esta interrupción antes de que el sistema esté prepara,

do para leer el cos.9^

2.-

Se inicializa el PÍA en la forma descrita en 2.11.. 2'.

46

(RESÉ?

4

Inhabilita

IRQ

Iriicializa

PÍA

2

Determina

STACK

3

Habilita

IRQ

k

i

i

Espera por

IKQ i

Inhabilita'

IfiQ

00

I

Inicia conver

ción de I

16

3-1 Diagrama de Fluio

47

3--

En el .6802 los registros del STACK POINTER son ubicados

en la RAM, debiendo señalarse el punto de inicio del mismo .

Esta función es cumplida en éste bloque (el STACK empieza en

la localidad 0D de la RAM).

4.-

Con el MASK BIT se.habilita IRQ, la misma que se utili-

za para la determinación del eos *9-

5,-

Espera hasta que se tenga cero lógico en la entrada IRQ.

Una vez que ésto sucede, realiza la rutina descrita en 3.1.2,

luego de lo cual continúa en 6.

6..-

Se inhabilita IRQ en la forma ya'indicada, ya que la

misma es necesaria una sola vez por cada proceso de mc-dicióndel factor de potencia.

7.-

Se almacena en las localidades 01 (SH) y 02 (SL) de la -

RAM,, los números exadecimales 00 y 2fí respectivamente, que c_o

rresponde a la localidad de memoria (RAM), a partir de la

-

cual se almacenan las lecturas de I

F

8.-

Se inicia la conversión d e I-r,,

l-a nnisma que tomará al

r 3

conversor A/D aproximadamente 100 li segundos. Durante este

~

tiempo' el microprocesador puede desarrollar otras funciones.

9.-

Se borra el registro R que está en la localidad 00 de la

RAM. El contenido de R se utiliza como información dentro de-

48

la rutina NMI que selecciona I

F

10.-

ó I

1F

, según sea el caso

Se chequea la frecuencia de la red. Si es 60 HZ conti

núa en el bloque 11; si es 400 HZ, en 15.

11.-

Se almacena en las localidades 03 (TH) y 04 (TL) de la

RAM, los valoreshexadecimales 00 y 57 que corresponden a la—

dirección de la memoria (RAM) a partir de la cual se almacenan las lecturas de I

12.-

1F

Se carga en el contador K (localidad 06 de la RAM) con

A4-, ,- ,, que

que es

es el

el número •de conversiones (NMi) que se orodu 16

cen en el caso de 60 HZ.

13.-

Se borra el registro Q (localidad 05 de la RAM). Es te-

es utilizado en el caso de 60 HZ para reconocer si en el prp_

ceso se almacenan IF é I-,p

De las 164 muestras de corrience

que es posible tomar, se almacenan 82, 41 que corresponden a

1 v 41 a 1

con el fin de utilizar únicamente la RAM de F

IF'

que dispone el 6802. En este nivel se termina el proceso deinicialización en el caso de 60 HZ.

14.-. Cuando la frecuencia de la red es 400 HZ se almacena en las localidades TH y TL de la'RAM los valores hexadécimales00 y 56, valor menor en uno a la dirección asignada para elinicio del'bloque de I „. (esto se explica posteriormente en

IF

el diagrama de flujo)

49

15--

Se almacena en el contador M (localidad 05 de la RAM)-

el númerohexadecimal 19 que corresponde al" número de mu-es

-

tras que se almacenan de i ,

r

16."

Se almacena en el contador K (localidad 06 de la RAM )

el númerohexadecimal 1A que corresponde al número de mués

tras que

-

se toman en el caso de I. .• . •

" 1F

Una vez terminada la inicialización el proceso continúa en ~

el diagrama de flujo 3-4 en la entrada A.

3-1.2.- DIAGRAMA DE FLUJO DE IRQ ' (Fig. 3.2)

Utilizando la interrupción'IRQ, se realiza la lectura dé una

relación de tiempo proporcional a la diferencia de fase.

El máximo defasamiento (360 ) para el caso en que la Frecueri

cia de la red de alimentación es 400 HZ equivale a un tiempo

de 2.500 //segundos. Si la cuenta de tiempo'en el micropróce

/

".

"~

sador se realiza en el acumulador B 3 las operaciones necesa-,

rías para un incremento en este acumulador requieren de.10 ciclos de operación ( 11,17^-segundos), por lo que se tiene un

rn-ixii.no de 224 incremeuLus para un defasamiento de 3b0

(el a

cumulador B por ser de tí BITS puede aceptar hasta un raáximóde

255

incrementos).

•

•

Si los 224 incrementos equivalen a 360 .un incremento del- acumulador B equivale a 1,60 . Los valores de. 0 a 90 en in o

crementos de 1,60 son almacenados en la EPROM de FF0C a

—

FF453 ocupando 57 localidades.

•

.

50

LOCALIDAD DE LA EPROM

FF0C-

COSENO

.

Cos

0°

-O

FF0D

•FF0E

•

FF44

'

Cos 1,6

,o

Cos 3,2

Cos 83,6°

Cuando la.frecuencia de la red de alimentación es 60 HZ se u

tiliza como contador el registro índice; en éste caso el máximo defasamiento

(360 ), equivale a un tiempo de 16.666

tiseg. Si las operaciones .necesarias para cada incremento en el registro índice requieren de 15 ciclos de operación

(163755

——

Aseg.); se tiene entonces un máximo de 994 incremen

ros; cada incremento equivale a 0,3619 -

Con el fin de economizar espacio de memoria .(EPROM),se toman

intervalos equivalentes a cuatro incrementos, por lo que sedivide para cuatro, la cantidad que se encuentra en el regis_

tro índice, reduciéndose el máximo número de incrementos

a -

248; cada uno de estos incrementoa equivale a 1,4477 .

Los valores de coseno correspondientes

a éstos ángulos son al.

macenados en las localidades de la EPROM de FF45 a FF83, ocupando 63 localidades.

1.-

EPROM

COSENO

FF45

Cos 0°

FF46

Cos 1,4477

FF47

Cos 2,8954

FF83

Cos 90,00°

Una vez que se produce IRQ, esto es con nivel cero lógi-

co a la salida del detector de cruce de cero de la muestra de

voltaje,, se lee el estado del ORB del PÍA colocando éste BYTE

en el acumulador A.

2.-

Se realiza un "AND" lógico del valor del acumulador A

-

con el número, exadecimal 20. Si el BIT cinco de A es igual

a

cero el resultado de éste AND, BIT A BIT es'cero, en el casocontrario el res-ultado es 20., ,_

16

3--

Se chequea el resultado de la operación anterior; si es'

igual a cero el proceso regresa al bloque uno, permaneciendoen este lazo hasta que el valor del BIT 5 cambie a uno lógico,

momento en que el proceso continúa en el bloque cuatro. Cuando no existe muestra de voltaje a la entrada, el programa

se

mantendrá dentro de éste lazo.

4.-

Se realiza el chequeo de la frecuencia de trabajo, si -

la frecuencia es 60HZ continúa en 5, si es 400 H'Z en 18.

Fig.

3.2

Diagrama de Flujo de IRQ (a)

ORBi^AccA

T

AND A c c A

con. 20

2

Borra X

5

53

Fig. 3.2

Diagrama de F l u j o de IRQ

(b)

Fig. 3-2

Diagrama de Flujo de IRQ . (c)

De la EPROM

(en forma indexada)

55

5-~

Se borra el registro índice.

6.-

Se incrementa en uno el registro índice cada vez que -

el valor de I1F"es uno lógico.

7 •- • Se coloca el valor que .se encuentra en el OR3 del

PÍA

en el acumulador A, -el b7 corresponde al valor de I_ _ .

Ir

8.-

Se chequea el valor del bit 7 si es uno lógico el pro-

ceso regresa al bloque 6, permaneciendo en éste lazo hasta que el b?. cambie a cero lógico.

9--

.

Se incrementa en uno el registro índice cada vez que -

el valor de I p sea cero lógico.

10.-

Se coloca en AccA el valor del ORB del PÍA.

11.-.

Se chequea el valor del BIT 7, si es cero lógico el--

proceso regresa al bloque 9, mantenienvióse en éste lazo has-ta que el b? sea igual a uno lógico.

12.-

Se divide para cuatro el valor-que se encuentra en el .-

registro índice, éste valor como s'e mencionó es máximo 248 , •

por lo que está contenido en el BYTE menos significativo del

registro índice.

13--

.

••'

. -

'

Se almacena el B'fTE menos significativo del registro '-

índice en el acumulador

14--

Se almacena la localidad 0B de la RAM el valor equiva

lente a 270° (BAn ,.) .

16

15.-

Se almacena en la localidad 0A¿ie la RAM el valor equi.

valente a 90° (3E_,r) .

16

16.-

Se almacena en la localidad IE de la RAM el valor

de

compensación de la diferencia de fase, valor que es igual al

def as amiento producido .por el filt.ro (180 ) más el de fas a

-

miento producido por la punta de medición de corriente (W ) ,

siendo la compensación total Y de 180

+ W ( en éste caso W=

0 , ya que en la lectura experimental se utiliza un SHUNT.)

17.-

Se almacena en la localidad 1F de la RAM el valor F8 ^

16

El proceso continúa en el bloque 29 común para 60 y 4/ÓJÓ HZ.

Las operaciones que se realizan.del bloque 18 a 28 para el caso de 400 HZ son similares a las descritas en los bloques5 a 17, en el caso de 60 HZ 3 por lo que no se hace una

des-

cripción bloque por bloque.

29--

Se compara el valor del acumulador B (t91). con el de-

fasamiento de compensación, si el resultado de ésta opera

-

ción es negativa, B<C 1E el proceso continúa en 32, en el caso de B ^ 1E en 31 -

El

algoritmo desarrollado para corregir la fase es el si -

57

guíente:

a)

Si Y+01^360°

Se tiene Z = Y + 91_

Donde

Z =

def asamiento medido que se encuentra en el AccB

Y =

defasamiento de compensación, almacenado en la localidad 1E de la RAM.

01= " defasamiento real.,'

Se obtiene :

01=

b)

Z-Y es- el caso en que Z-Y^.0

Si Y + 01 ^360°

•

'

Se tiene Y + Gl = 360°+ Z

De donde se obtiene:

01= (360°-Y) 4- 2 es el caso en que Z-Y ¿- 0

Doñee:

(360 -Y) = defasamiento de compensación

en

30.-

1F.

-

-

•

Si Z-Y^0 se realiza la operación Z-Y y se coloca éste,

valor en el acumulador B.

31.-

•

almacenado-

'

..

•

Si el valor, de Z-Y^103 la operación a realizarse es Z+

Y, éste.valor se almacena en el acumulador.B.

En los bloques 32 a 52, por medio del valor que se encuentra-

en el acumulador B se realiza la determinación del signo y el

valor del coseno de Qlyalor que es colocado en la localidad 17 de la RAM, asignado para almacenar -el valor decimal del

c_o

seno de 91, el valor entero es almacenado en 18. En la locali.

dad 0E de la RAM es almacenado el inverso del código siete

segmentos del signo.

Por medio de RTI se regresa al programa en-el punto donde seprodujo la interrupción, continuando con la ejecución.del mis_

mo.

3.L3-- DIAGRAMA DE FLUJO PARA -N-MI-(Fig. 3.3).

Una vez que termina la conversión de I. se produce' la primera

F

, iniciándose el proceso de lectura de las 41 muestras deI él

en la frecuencia de 60 HZ o de las 25 muestras d'e I_

F

1K

F

e I.

eu 400HZ3 según sea la frecuencia de la red de alimenta

.

1F

—

ción.

1.- Se chequea el valor del contador K; si su valor es cero quiere decir que la lectura de muestras terminó, regresan

do al punto donde se produjo la interrupción, sin iniciar una

nueva conversión, en caso de K £ 0 el proceso continúa en 2.

2.- Se chequea la frecuencia de trabajo, si es 60 HZ va al

bloque 3, si es 400 HZ al bloque 17-

3.- Se.chequea el registro R; si R •= 0, la muestra leida co rresponde a l . si R £ 0 a I

4 u 11, respectivamente.

..

continuando en los bloques

59

Fig. 3-3"

Diagrama de Flujo para NMI

60

4*-

Se inicia la conversión de una muestra análoga de I_ „ ;'

Ir

esta conversión se inicia dentro del lazo correspondiente a I , esto se explica ya que en el caso de 60 Hz las muestras de corriente se almacenan en forma alternada.

5.-

Se cargan los valores que se encuentran almacenados en SH y SL en el MSB y LSB del registro índice respectiva -

mente; inicialniente este valor es 002E.

6.-

Se chuequea el valor del registro Q; con Q - 0 el proceso

continúa en 7> con Q ¿ 0, .no se almacena el valor del I

r

y se continúa en 9. •

7.-

Se almacena el valor de !„ en la dirección de la RAM que

se encuentra en el registro .índice.

8.-

Se incrementa en uno el valor de el registro SL.

9.-

Se complementa el valor de el registro R s de esta formase asegura la alternatibilidad de I é l " .

F

1F

10.-

Se decrementa en uno el contador K, luego de lo cual utilizando la interrupción RTI se regresa al punto donde

ee produjo NMI.

11.-

Se inicia la conversión de ]_ .

12.-

Se carga el registro índice con los valores de TH y TL,

inicialmente éste valor es 0057•

En 13, 14, 15, se realiza la misma función que la descrita -

61

para los bloques- 6, 7 y 8.

16.-

Se complementa el valor del registro Q.

El proceso continua en los bloques 9 y 10 ya descrito, regre

sando entonces al punto del programa donde se produjo la interrupción . Como ya se mencionó este proceso se repite has ta que K = 0.

El sistema 'utilizado para la lectura de las muestras en la frecuencia de 400 HZ difiere de el de 60 HZ, en que en estecaso no se alterna.ni la lectura ni el almacenamiento de las

muestras de las corrientes; esto se.debe a que reducir aún más el número de muestras (25) que se puede tomar dentro deun ciclo, disminuye la precisión del cálculo de los valoresRMS de los corrientes, razón por la que se toman las mués

-

tras de !„ e I ,_, en dos ciclos consecutivos.

F

1F

17--

Cuando el proceso se realiza para 400 HZ luego del blo_

que 2 se chequea el valor del registro R; si R = 0 con.

tinúa en 18 (!„), si R ¿ 0 continúa en 25 (!.,„)

'F

1F

18.-

Se inicia la conversión de un nuevo valor de I

19--

Se carga el registro índice con SH y SL.

20.-

Se guarda I

21.-*

Se incrementa en uno SL, valor que se carga en el LSB

F

en la memoria RAM.

del registro índice.

62

22.-

Se decre'menta en uno el contador M, el mismo que indi ca el número de muestras a tomarse de I

F

23--

Se chequea el valor de M; si M ¿ 0 por medio de RTI regresa al punto del programa donde se produjo la interru£

ción NMI, si M = 0 continúa en el bloque 24.'

24--

Se complementa el valor del registro R, asegurando de esta forma que cuando termine la presente conversión se

entre al lazo de I

1F

. La conversión en proceso al momento co-

rresponde a una muestra de I_

r

25--

Inicia la conversión de I

26.-

Carga el registro índice con los valores almacenados en

TH y TL. Inicialmente el valor almacenado será menor en

uno que la dirección donde se inicia el bloque de I

1F

, esto -

se explica por la razón: mencionada en 24, almacenando por con

siguiente la muestra 26 de I.-,

en la localidad

locali

56

r

de la RAM ..;

que no se utiliza" en el proceso de 400 HZ.

2?.~

Se almacena 1

en la memoria RAM,

1F

28.-

Se incrementa en uno TL.

29--

Se decrementa uno el contador K. Cuando K es igual a c_e

ro significa que terminó la lectura de Ip é I

.

Luego de este bloque se regresa al punto donde se produjo

interrupción NMI en el programa. Este lazo se repite hasta

la

-

63

completar la lectura de I. '.

1F

3.1.4.- DIAGRAMA DE FLUJO PARA CALCULO DEHI2 (IF^e'llF2) Fig

3.4.

Para elevar al cuadrade cada una de las muestras se considera

simplemente como una multiplicación de . un número por si mismo,

empleándose para la multiplicación el

y sumar.

'

algoritmo* de desplazar

"

M 0 0 0 0 1 1 1 0 m

Multiplicando (M)-

14

R 0 0 0 0 0 0 0 0

Multiplicador ( m ) 1 4

S6

M 0 0 0 1 1 1 0 0 0 Lsb

1

R 0 0 0 0 0 0 0 0

Resultado ( R )

196

M 0 0 1 1 1 0 0 0 1

R 0 0 0 1 1 1 0 0 *

M 0 1 1 1

R 0 1 0 1 01

1 Msb

R'l 1 0 0 0 1 0

El equivalente decimal se muestra con el- propósito de compa rar las dos operaciones; el resultado.es obtenido desplazando

y sumando el multiplicando con el resultado anterior. Cuandoel BIT chequeado del multiplicador es cero, simplemente se

desplaza a la izquierda el multiplicando. Si es uno se suma. el multiplicando

al resultado sucesivo y luego se desplaza

a

la izquierda el multiplicando, una vez chequeados todos los .BITS del multiplicador termina la operación la respuesta

es

64

Fig. 3.4

Diagrama de F l u j o para Cálculo de El

A

Borra

. INDEX

Borra 2B

MSB del Mult

(a)

65

*j

Fig. 3-4

Diagrama de Flujo para Cálculo de

£I.

(b)

Desplaza a

la Isou. Muí

{*) Con los paréntesis , se indica que se refiere al

contenido de la localidad mencionada.

Nota-.- La descripción de las localidades y registros

mencionados en los diagramas de flujo se encuentra en 3*2'.

66

igual al último resultado sucesivo (R ).

En este caso cada una de las muestras de corriente tiene unaextensión de 8 BITS, al elevar al cuadrado la misma alcanza una extensión máxima de 16 BITS., por lo que se hace necesa ria la utilización de dos BYTES de la RAM para almacenar es tos resultados parciales.

Además se realiza en el mismo diagrama de fluj'o la suma de los

cuadrados de las muestras de corriente. Se tiene un máximo de

41 sumas de números de 16 BITS de extensión, llegando a un re

sultado que tiene un-máximo de 22 BITS, por lo que para almacenare! mismo se destina una extensión de 3 BYTES

P

2

II- " y 3 BYTES para elzjr

.

r

'

para el

-

1F

3 - 1 - 5 . - DIAGRAMA DE' FLUJO PARA CALCULO DE

NUI

(!„ e I... ) *

1F

Fig. 3.5--

El algoritmo utilizado para la obtención de la raíz cuadrada

es el de restar sucesivamente la serie de números impares

—

(1, 3, 5 , 7 ...... 2n-l) del valor que se desea obtener la

-

raiz cuadrada, hasta que el resultado sea cero o un número negativo.

El número de restas requeridas corresponde a la raiz cuadrada del número; en el caso de que el número no sea un cuadrado perfecto el resultado será un valor aproximado. Con el

-

fin de reducir el margen de error se realiza además la aproximación al inmediato superior o inferior, según sea el caso.

Por ejemplo en la raiz cuadrada de 49 se tiene:

67

40

-7

33

-9

24

-11

13

49

1) -

'4)

—1

48

2)

—3

5)

3)

45

—5

40

6)

7)

13

-13

0

-15

-15

En este ejemplo se puede observar que el número de substrae ciones necesarias para obtener 0 es siete, que corresponde ala raíz exacta de 49-

El proceso de resta termina cuando se obtiene un resultado-,

negativo; el último número restado,' es igual al doble más uno del valor de la raíz cuadrada (15-2X7+1), siendo éste elprocedimiento a utilizarse en este caso, evitando de esta •forma el tener que llevar la cuenta del número de substrae ciones.

2

Como ya se mencionó la longitud máxima de E1

es de 22 bits-

con un valor decimal máximo de 2'666.025, la raíz cuadrada de éste número es 1.632,3, por lo que el máximo impar a restarse tiene un valor de 3-265, siendo necesario de 12 bits para la representación binaria de éste número.

Para realizar el algoritmo de la aproximación se considera la última resta en el caso de tres raíces cuadradas de 36,42,

43, 49-

36

42

6

R

-13

-13

-13 (6)

-

7

43

7

-13 (6)

49.

0

-15 (7)

Los valores que se encuentran entre paréntesis corresponden a

la raíz cuadrada del número, sin considerar ninguna aproximación.

Sumando algebraicamente S y R; si el resultado es un número negativo se aproxima al inmediato inferior, si de la suma

se

obtiene un número positivo se aproxima al inmediato superior.

En el microprocesador los números negativos están exprésadoscomo complemento de dos de su valor positivo, por lo que la _q

peración a realizarse es la suma de estos valores como se in-rdica a continuación:

C

S 000000000(0.)

+R 0 1 1 1 1 0 0 1 1 (-13.,)

Suma 0 1 1 1 1 0 0 1 1 -13

•

P

S

000000110(6.)

+R

0 1 1 1 1 1 0 0 1 (-7-)

0 1 1 1 1 1 1 1 1-" -1

'S

+R

0 0 0 0 . 0 0 1 1 1 (7.)

0 1 1 1 1 1 0 1 0 (-6) •

1 0 0 0 0 0 0 0 1 1

S

+R

0 0 0 0 0 0 0 0 0 (0)

0' 1 1 1

1 0 0 0 1 (-15)

0 1 1 1 1 0 0 0 1 - 15.

Desprendiéndose de las operaciones antes- indicadas que cuando

el CARRY es 0 el resultado permanece igual, si c= 1 se incrementa en uno el resultado.

69

Fig. 3 - 5

Diagrama de F l u j o para Cálculo de

NHI'

divide para

2 resultado

70

3.1. 6.-

DIAGRAMA DE FLUJO PARA CALCULO DE

La división a realizarse es entre dos números binarios, con

una extensión máxima de 1 2 BITS cada uno.

Para realizar esta operación se emplea el algoritmo de .restas sucesivas.

En el caso de la obtención del. entero del re-

sultado, simplemente va restando

' \LZTI

menos la

\ÍHI

,

el número de restas que se puedan realizar sin OVERFLOW es

el valor de la parte entera.

Una vez que se produce el OVERFLOW la operación a seguir es

la obtención del resultado decimal.

En la figura 3-6rse presenta la división binaria de 1 5 para

11 .

De esta operación se puede desprender que cuando el resultado de la resta del dividendo menos el divisor es un número

negativo (C=l), se coloca un cero en el BIT menos significada del dividendo, para realizar la próxima resta, cuando

71

Fig. 3.6

Diagrama de F l u j o para Cálculo de\|lT t I

Borra

IB .

1F

(entero)

I

IKC 1B

T

AccA-(21

v

.ni;:r

(a)

72

Fig. 3.6

Diagrama de Flujo para Cálculo de

V

no

,-'2

(b)

73

Fiq. 3 .6 (c)

E j e m p l o de d i v i s i ó n

binaria

(C)

CARRY

ENTERO

DIVIDENDO

DIVISOR

RESIDUO

1111

- 1011

.

0

1

0100—[ D E S P L A Z A

- 1 01 1 /

/

1

00000000

1 1 01 /

N = 2

00000000

1001/

. indica que no alean;

1000-y DESPLAZA- 1011 /

N = 1

DECIMAL

0

1 0000

- 1011

00101-7 DESPLAZA

00000001

1010-j D E S P L A Z A

- 1011 /

N = 3

1

1111/

00000010

1 01 00

N = 4 .

0

'

010017 DESPLAZA

00000101

•1 001 0

- 1011

N = 5

0

001 11 -.DESPLAZA

011

1110

- 1011

N = 6

0

0011-, D E S P L A Z A

00010111

0110-.DESPLAZA

1011 /

N = 7

1

1011/

001 01 1 1 0

1011

N =

0001

01011101

74

C = 1, se coloca en uno en el BIT menos significativo del re_

saltado y se hace un desplazamiento a la izquierda del residuo , repitiendo el proceso durante ocho veces, obteniéndoseel resultado binario de 1,01011101,

, . Siendo su equi-

valente decimal 1,36328125 valor que es aproximadamente igual

a 1,3636 que 'es el resultado de dividir los valores decima les de 15 para 11. El valor que se coloca.cada vez en el BIT

menos significativo, del resultado es el complemento de C por

lo que en el proceso simplemente se entra C en este BIT, para finalmente complementar el decimal completo obteniendo de

esta forma el resultado deseado.

3-1.7.- DIAGRAMA DE FLUJO PARA CALCULO DEL FACTOR DE POTENCIA

EN BINARIO (Fig. 3-7)

El producto a realizarse para la obtención del factor de po\

2 7\

2

tencia es de MCI

/ N E I 0 por el eos.91, estos valores

1F

r

constan de parte entera y parte decimal con las siguientes características:

a)

El coseno tiene parte entera, únicamente cuando su valor

absoluto es 1, por lo que para fines de programación se-

considera el coseno como un número decimal binario de 8 BITS.

El caso de eos. 91=1 es tratado como up caso especial.

b)

\ /\

El valor de NZII^^/ \JHI

puede ser considerado de ídén

1F'

F

—

ticas características a las del coseno, pues como se

—

-

menciono

\\

Al

2

MUÍ., / MHI n r i

,

__ .

1F'

1F pero se desarrolla esta operación -

'como si este valor constara de parte entera y parte decimal.

De esta forma si se obtiene un valor mayor

a uno

quiere

—

75

Fig. 3-7

Diagrama de Flujo para Cálculo del Factor de Potencia

en Binario, (a)

D

*

1

Borra

1^15,16

Borre

Acc.A. y AccB

09 ^>N

76

Fig. 3.7

Diagrama de Flujo para Cálculo del Factor de Potencia

en Binario, (b)

77

decir que hay algún problema de calibración en el sistema.

El algoritmo utilizado es el de una multiplicación entre dos

números enteros, en que el multiplicando (eos 91) es de 8 BITS y el multiplicador tiene un máximo de 9 BITS, con ps -'

tas características se asigna para el resultado 3 BYTES

—

(24 BITS).

Se considera tanto el coseno de 01 como a

con ocho decimales cada uno, de esta forma en la ubicacióndel punto decimal se recorre 16 BITS a la izquierda. Así en

el resultado obtenido un BYTE corresponde al entero y los dos BYTES menos significativos a 'los decimales.

3-1.8.- DIAGRAMA DE FLUJO'PARA CONVERTIR EL RESULTADO BINARIO DEL FACTOR DE POTENCIA EN UN VALOR BCD. (Fig. 3.8)

Para el cálculo del valor BCD del factor de potencia, se to_

ma en cuenta únicamente los 8 primeros BITS binarios decima

les, los cuales se encuentran en la localidad 15 de la RAM,

siendo los valores BCD equivalentes de cada BIT los siguieri

tes:

b7

0,5

b6

0,25

b5

0,125

b4

0,0625

b3

0,03125.

b2

0,015625

. bl

b0

0,0078125

0,00390625

78

Fig. 3 - 8

Diagrama de Flujo para convertir el resultado

del FP. a BCD. (a)

egistro índice)

no

Carga AccA

Indexado 0C

AccA+( 1

T

DAA(ajust 2 decimal)

T

INC X

INC X

Binario

79

Fig. 3.8

. . .

Diagrama de Flujo para convertir el resultado Binario

del FP. a BCD. (b)

v

Carga AccA

DAA

INC X

no

Carga MSB

BCD en 15

Carga ^SB

BCD en 10

Carga 3SB

BCD en 10

En el proceso se utiliza los 4 dígitos más significativos de

los decimales, valores que son almacenados permanentemente

en la EPROM en las localidades FF84 a FF93 en la siguiente

forma:

FF84

39

FF88

56

FF8C

25

FF90

00

FF85

00

FF89

01

FF8D

06

FF91

25

FF86

78

FF8A

12

FF8E

50

FF92

00

FF8?

00

FF8B

03

FF8F

12

FF93

50

Para el cálculo del valor BCD equivalente al MSB decimal del

factor de potencia simplemente se realiza la suma de los valores correspondientes a cada BIT que tenga el valor uñó. Por