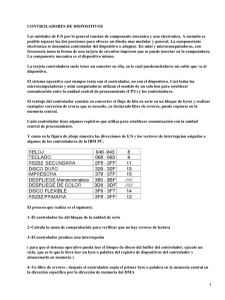

total = 10 + 5 + 25 + 30 + 5 + 55 + 145 + 25 = 300

Anuncio

1 TEORÍA DE LOS SISTEMAS OPERATIVOS GESTIÓN Y ADMINISTRACIÓN DE LA ENTRADA Y SALIDA INTRODUCCIÓN. El Subsistema de Entrada y Salida, es la parte del sistema operativo, encargada de la gestión de los dispositivos de E/S y tiene por objeto, actuar como interfaz entre los usuarios del sistema y los dispositivos de E/S, de forma que en las capas superiores del sistema operativo, los dispositivos se traten de una manera, sencilla, segura y eficaz. Respecto a los distintos módulos de gestión del SO, analizados anteriormente, tal vez sea la gestión del módulo de E/S, el más complejo en el diseño de los sistemas operativos, dada la amplia variedad de dispositivos y las numerosas aplicaciones que los utilizan, resultando difícil construir y diseñar una solución general y consistente. El subsistema de E/S proporciona un medio, para el tratamiento de una manera uniforme, de los archivos y dispositivos donde se encuentran estos archivos y permite, que se puedan manipular mediante un conjunto de instrucciones de un lenguaje de alto nivel utilizadas por el usuario. Para que esto sea posible el subsistema de E/S, debe proporcionar al dispositivo final, las señales de control específicas de cada tipo de dispositivo, correspondientes a las órdenes de alto nivel de la unidad de control del procesador, que se producen durante la ejecución de un proceso. Después de estas breves consideraciones se puede definir una operación de E/S, como el intercambio de información entre la memoria principal o la unidad de control de la CPU y los dispositivos periféricos, denominados también dispositivos de E/S o también módulos de E/S. Este intercambio se realiza a través de los controladores existentes en la actualidad, que tienen por objeto regular el tráfico de datos hacia los dispositivos de E/S o viceversa, que puede constituir una sola interacción ocasional con la CPU o tener un número de operaciones de E/S independientes, situadas en una cola de espera, antes de que se completen otras en ejecución. Por otra parte, la ejecución concurrente de tareas independientes, procedentes de los diversos procesos en multiprogramación, requiere una cuidadosa planificación de múltiples secuencias de código diferentes y de sucesos críticos en el tiempo, percibidos o producidos por los dispositivos de E/S. Para que esto sea posible será necesario incorporar al hardware del sistema, pequeños procesadores de E/S, que reciben el nombre de canales de E/S. En este tema se trata de señalar brevemente los aspectos más importantes de los dispositivos de E/S y la planificación que es necesario establecer, para obtener la máxima eficacia, en el funcionamiento del subsistema de E/S, posteriormente, se analizará la organización de las funciones de E/S y finalmente enfocaremos, algunos aspectos hardware del subsistema de E/S, insistiendo en sus atributos únicos, que necesitan una programación especializada y hacen posible las operaciones de concurrencia. DISPOSITIVOS DE ENTRADA Y SALIDA. En la actualidad pueden existir múltiples tipos de dispositivos conectados al sistema informático, mediante los controladores de E/S, cada uno con sus propios requerimientos. La mayor parte de ellos operan asincronamente con respecto a la CPU, por lo tanto, el hardware y software del subsistema de E/S, se enfrenta con las complicadas tareas de atender, tanto las solicitudes individuales de los dispositivos de E/S, como las ordenes de alto nivel, procedentes de la unidad de control del procesador, asegurando una operación segura y eficaz, ocultando los detalles APUNTES DE SISTEMAS OPERATIVOS I A. GLEZ. DEL ALBA 2 GESTIÓN Y ADMINISTRACIÓN DE LA ENTRADA Y SALIDA específicos del dispositivo, presentando a las capas exteriores del sistema operativo una abstracción uniforme de las operaciones de E/S y finalmente a los programas de usuario. APUNTES DE SISTEMAS OPERATIVOS I A. GLEZ. DEL ALBA 3 TEORÍA DE LOS SISTEMAS OPERATIVOS En este tema no se puede realizar un estudio detallado de cada uno de los dispositivos que pueden estar conectados a un ordenador, por lo tanto, se dedicará todo el detalle a los dispositivos de discos, que son los más utilizados por el sistema operativo. Desde un punto de vista general, los dispositivos de E/S o periféricos, que realizan las operaciones de E/S con los ordenadores, pueden clasificarse en tres categorías: Dispositivos legibles por las personas, que son los más apropiados para la comunicación con el usuario, entre ellos se pueden destacar los terminales de vídeo, que constan de un teclado y una pantalla y quizá otros dispositivos como un ratón o una impresora. Dispositivos legibles por la máquina, adecuados para comunicarse con los equipos electrónicos del ordenador, entre los que se puede destacar el procesador, los canales de E/S, los dispositivos de E/S. En este grupo se pueden destacar, los discos, las unidades de cinta, los sensores, los controladores, etc. Dispositivos de comunicaciones, apropiados para comunicarse con dispositivos remotos, como por ejemplo, los adaptadores de líneas digitales y módem. Existen grandes diferencias entre las clases de dispositivos y estas son incluso substanciales dentro de cada clase, las principales diferencias son las siguientes: Velocidad de los datos, ya que puede haber una diferencia de varios órdenes de magnitud, en las velocidades de transmisión de datos, según los dispositivos. Aplicaciones, ya que la utilidad que se le da a un dispositivo, tiene una gran influencia en el software y en las políticas del sistema operativo. Complejidad del control, ya que existe una cierta diferencia entre el control de unos dispositivos u otros, así por ejemplo, una impresora necesita una interfaz de control relativamente simple, en cambio en un disco es mucho más compleja. Unidad de transferencia, ya que los datos pueden transmitirse, como flujos de bytes o caracteres, por ejemplo en un terminal, ratón etc, o bien en bloques mayores, constituidos por un conjunto de bytes o caracteres, como por ejemplo en un disco. Representación de los datos, ya que en diferentes dispositivos, se pueden utilizar distintos esquemas de codificación de datos, incluidas las diferencias en los códigos de caracteres y los convenios de paridad. Condiciones de error, ya que la naturaleza de los errores, la manera en que se informa sobre ellos y el rango disponible de respuestas, difieren ampliamente de unos dispositivos a otros. Sincronización, la mayor parte de los dispositivos de E/S, no mantienen ninguna relación con el reloj del ordenador, siendo por tanto impredecible para la UCP, el tiempo que se necesitará para completar una operación de E/S. Esta diversidad en los conceptos anteriores, conduce hacia un enfoque consistente y uniforme de la E/S, que es difícil de alcanzar, tanto desde el punto de vista del sistema operativo, como de los procesos de usuario. APUNTES DE SISTEMAS OPERATIVOS I A. GLEZ. DEL ALBA 4 GESTIÓN Y ADMINISTRACIÓN DE LA ENTRADA Y SALIDA PLANIFICACIÓN DE LA ENTRADA/SALIDA EN DISCO. En los últimos años, el crecimiento en velocidad de los procesadores y la memoria principal ha dejado muy atrás el de los accesos a disco, es decir, la velocidad del procesador y de la memoria principal se ha incrementado en dos órdenes de magnitud con respecto al disco y el resultado es que, actualmente, los discos son por lo menos, cuatro veces más lentos que la memoria principal. Este avance se espera que continúe en el futuro inmediato, por lo tanto el rendimiento de los subsistemas de almacenamiento en disco, es de una importancia vital y se han realizado numerosas investigaciones sobre la manera de mejorar dicho rendimiento. El rendimiento de los subsistemas de disco se puede mejorar de dos formas: Utilizando una memoria cache de disco. Planificando las solicitudes de acceso. La mayoría de los trabajos dependen de las unidades de disco para las operaciones de E/S, por lo tanto, es importante que el servicio del disco sea lo más rápido posible, el sistema operativo puede mejorar el tiempo promedio de servicio del disco, de las dos formas anteriores. Una solicitud especifica varias informaciones necesarias: Si se trata de una operación de Entrada o de Salida. Cual es la dirección en el disco, es decir, unidad, cilindro, superficie y bloque. Cual es la dirección de memoria. Cuanta información se transferirá, es decir, número de bytes o de palabras. Si se opta por la planificación de las solicitudes de acceso y se deja para más adelante la utilización de una memoria cache adecuada, se debe observar, que el tiempo total para servir una solicitud del disco es la suma de tres tiempos: Posicionamiento. Latencia. Transferencia. Cada dispositivo de E/S, incluyendo cada unidad de disco, tiene una cola de solicitudes pendientes y cada vez que un proceso necesita E/S del disco, emite una llamada al sistema operativo. Si la unidad y el controlador del disco están disponibles es posible servir de inmediato la solicitud, sin embargo, si la unidad o el controlador está sirviendo una solicitud, será necesario colocar en una sola cola todas las solicitudes que no puedan ser atendidas. En un sistema de multiprogramación con varios procesos activos, con frecuencia esa cola no estará vacía, por lo que al concluir una solicitud, debemos seleccionar una nueva de la cola y servirla. Un servicio de disco requiere el movimiento de la cabeza a la pista deseada, esperar el tiempo de latencia y finalmente transferir los datos, por lo tanto, la planificación del disco implica un cuidadoso examen de las peticiones pendientes, para determinar la forma más eficiente de servir las peticiones de servicio. Para una buena planificación del disco, es preciso examinar las relaciones posicionales entre las solicitudes en espera, tratando de reordenar la cola de solicitudes de manera que las peticiones puedan ser servidas con el mínimo de movimiento mecánico posible. APUNTES DE SISTEMAS OPERATIVOS I A. GLEZ. DEL ALBA 5 TEORÍA DE LOS SISTEMAS OPERATIVOS ALGORITMOS DE PLANIFICACIÓN DEL DISCO. Existen varios algoritmos, para minimizar el tiempo de planificación de una operación del dispositivo de disco y para analizar el funcionamiento de los distintos algoritmos se utilizará una cola de peticiones dinámica, teniendo en cuenta, que mientras la cabeza del disco se está colocando, para atender una solicitud, continuarán llegando peticiones posteriores. Las estrategias más populares que se pueden utilizar, para la optimización del acceso a un dispositivo de disco, son las que se estudian a continuación. PLANIFICACIÓN FCFS ( First-Come, First-Served) La forma más sencilla para planificar un disco es la planificación del servicio por orden de llegada. Este algoritmo es fácil de programar e intrínsecamente justo y el único posible cuando las peticiones llegan muy espaciadas en el tiempo. El principal inconveniente es que presenta unos resultados fuertemente dependientes de la distribución de las solicitudes sobre las pistas en el tiempo, por lo tanto es probable que no ofrezca el mejor tiempo de servicio. Supongamos que tenemos una cola de peticiones de acceso con las siguientes solicitudes: 90, 180, 35, 120, 10, 125, 60, 65, Si en un principio, la cabeza de lectura/escritura está situada en la pista 50, se moverá primero a la pista 90, después a la 180, 35, 120, 10, 125, 60, 65. 0 10 35 50 60 65 90 120 125 180 50 * (40) 90 * 35 180 * (145) * 10 (90) (85) 120 * (110) * (115) (65) 60 125 * * (5) *65 TOTAL = 40 + 90 + 145 + 85 + 110 + 115 + 65 + 5 = 655 En todo este recorrido, se ha producido un movimiento de la cabeza de lectura escritura, que totaliza 655 pistas. Con este tipo de planificación se producen bruscos movimientos de la cabeza de lectura/escritura que con otro tipo de planificación se podrían reducir. APUNTES DE SISTEMAS OPERATIVOS I A. GLEZ. DEL ALBA 6 GESTIÓN Y ADMINISTRACIÓN DE LA ENTRADA Y SALIDA PLANIFICACION SSTF. (Shortest-Seek, Time-First) Parece razonable servir juntas todas las solicitudes próximas a la posición actual de la cabeza de lectura/escritura del disco, antes de desplazar la cabeza de lectura/escritura a un punto lejano para servir otra solicitud. Si dos peticiones son equidistantes, se dará preferencia al sentido de movimiento actual de la cabeza de lectura/escritura. Esta suposición es la base del algoritmo, que resuelve primero las peticiones de menor tiempo de posicionamiento, para la planificación del disco, como el tiempo de posicionamiento es proporcional a la diferencia entre las solicitudes, medida en pistas, implantamos esta estrategia moviendo la cabeza a la pista más próxima de la cola de solicitudes. En el ejemplo que se ha considerado anteriormente la cola está formada: 90, 180. 35, 120, 10, 125, 60, 65 Si la posición actual es la pista 50. 0 10 35 50 50 60 65 90 120 180 * (10) 60 * (5) 65 * (25) 90 * (30) 120 * 125 (145) (25) 125 * (55) * * * TOTAL = 10 + 5 + 25 + 30 + 5 + 55 + 145 + 25 = 300 Este método de planificación, da como resultado un movimiento de 300 pistas, por lo tanto mejoraría considerablemente el promedio del servicio del disco. Con este tipo de planificación puede aumentar el tiempo máximo de atención de una petición, ya que en un sistema fuertemente cargado, si las peticiones para cilindros próximos llegan con cierta frecuencia y eso puede ocurrir en un sistema de asignación indexada, se podría producir un bloqueo indefinido, para algunas solicitudes más alejadas, en este sentido, es preciso recordar, que en un sistema real las solicitudes pueden llegar en cualquier momento, por lo tanto en un instante determinado, podemos tener una solicitud para la pista 10 y otra para la 180, si mientras se atiende la solicitud de la pista 10, van llegando otras solicitudes, que estén próximas a la pista 10, la solicitud para la pista 180 puede quedar en espera de una manera indefinida. Esta posible situación se denomina inanición u olvido. El algoritmo SSTF, aunque representa una considerable mejora con respecto al algoritmo FCFS no es óptimo. Así por ejemplo si en el caso que se ha representado anteriormente hubiéramos atendido la petición 35 antes de la petición 60, aún en el caso de no ser la más próxima el movimiento total se reduce. Una de las características importantes de los algoritmos FCFS y SSTF, es que cuando se termina de atender una petición, se examina la cola de solicitudes, para decidir el siguiente movimiento de la cabeza, por lo tanto, una vez tomada la decisión, la cabeza se posicionará en la pista correspondiente, sin atender las peticiones que pudiera encontrar en su camino. APUNTES DE SISTEMAS OPERATIVOS I A. GLEZ. DEL ALBA 7 TEORÍA DE LOS SISTEMAS OPERATIVOS Para intentar rentabilizar los movimientos de la cabeza, atendiendo las peticiones que se van encontrando, se proponen los algoritmos que se examinan a continuación. PLANIFICACION SCAN. El reconocimiento de la naturaleza dinámica de la cola de solicitudes, nos lleva al algoritmo SCAN (rastreo). Consiste en que la cabeza de lectura/escritura, comienza en un extremo del disco y se desplaza hacia el otro, sirviendo todas las solicitudes que encuentra a su paso, hasta alcanzar el extremo opuesto. Al llegar a este extremo, se invierte la dirección del movimiento de la cabeza de lectura/escritura y continua el servicio de rastreo en el disco hasta llegar al otro extremo. En el ejemplo que se está considerando: 90, 180, 35, 120, 10, 125, 60, 65 Lógicamente en este criterio se necesita conocer la dirección del movimiento de la cabeza de lectura/escritura, así como su posición más reciente. Si se considera que la posición actual es la 50 y la dirección del movimiento de la cabeza de lectura/escritura es descendente, se atendería primero las solicitudes 35 y 10 y al llegar a la pista 0, se invertiría el movimiento de la cabeza de lectura/escritura y se desplazaría hasta el extremo opuesto, sirviendo las solicitudes 60, 65, 90, 120, 125, 180. Si una solicitud llega justamente cuando la cabeza de lectura/escritura no ha sobrepasado esa pista, se serviría casi de inmediato, mientras que una solicitud correspondiente a una pista sobrepasada, tendrá que esperar a que la cabeza de lectura/escritura se mueva hasta el final del disco e invierta su dirección. 0 0 * 10 10 * 35 50 35 * 50 * (15) 60 65 90 60 * (5) * 65 (25) 90 * 120 125 180 (15) (60) (30) 120 * 125 (5) * (55) 180 * TOTAL = 15 + 15 + 10 + 60 + 5 + 25 + 30 + 5 + 55 = 220 Suponiendo que una distribución uniforme de las solicitudes de pistas, considera la densidad de solicitudes, cuando la cabeza de lectura/escritura llega a un extremo e invierte la dirección, en ese momento, lógicamente debe haber pocas solicitudes, para la zona que la cabeza de lectura/escritura acaba de sobrepasar, es decir la mayor densidad de solicitudes, se encontrará en el extremo opuesto del disco, además estas solicitudes, son las que más han esperado. PLANIFICACIÓN C-SCAN. Una variante de la planificación SCAN, diseñada para ofrecer un tiempo de espera más uniforme, es la planificación C-SCAN que consiste en la realización de un rastreo circular. APUNTES DE SISTEMAS OPERATIVOS I A. GLEZ. DEL ALBA 8 GESTIÓN Y ADMINISTRACIÓN DE LA ENTRADA Y SALIDA Al igual que la planificación SCAN, la C-SCAN mueve la cabeza de lectura/escritura de un extremo al otro, sirviendo solicitudes durante su marcha, sin embargo, cuando llega al extremo opuesto, regresa de inmediato al inicio del disco, sin servir ninguna solicitud en el camino. En esencia, la planificación C-SCAN considera la última pista adyacente a la primera. Utilizando este algoritmo, la cabeza de lectura/escritura cuando atiende peticiones, se mueve siempre en el mismo sentido, es decir de cero a n, considerando que se trata de un disco en el que la pista cero es la siguiente a la pista n, siendo n el máximo número de pistas del disco PLANIFICACIÓN LOOK. Observe que, de la manera que las hemos descrito, las planificaciones SCAN y C-SCAN, siempre mueven la cabeza de lectura/escritura de un extremo del disco al otro. En la prática, ninguno de los dos algoritmos se implanta de esta forma, sino que es más común, que la cabeza de lectura/escritura se mueva hasta la última solicitud en cada dirección. Si ya no existen solicitudes en la dirección actual, se invierte el movimiento. A estas versiones de la planificación, SCAN y C-SCAN, se las modificar dando lugar a la planificación LOOK y el C-LOOK, que consisten en comprobar si existe alguna solicitud antes de moverse en esa dirección. La decisión de no llegar al extremo del disco, se toma en un momento en el que no hay peticiones en dicho sentido, por lo tanto, una vez tomada esa decisión, cualquier petición que llegue, para la zona no barrida, deberá esperar a la próxima pasada. CRITERIOS DE SELECCIÓN DE ALGORITMOS. Anteriormente se ha realizado un análisis de un conjunto de algoritmos de planificación del disco, por lo tanto, será preciso establecer una serie de consideraciones para la selección de un algoritmo determinado. Es posible definir un algoritmo óptimo, cuando se realiza el diseño de un sistema operativo, pero quizá la simulación y los cálculos necesarios para la planificación óptima no justifiquen el estudio. El rendimiento de cualquier algoritmo de planificación, depende en gran medida de la cantidad y tipo de solicitudes. Si existen pocas solicitudes, lógicamente todos los algoritmos son equivalentes. El método de asignación de archivos, puede tener una gran influencia sobre las solicitudes del servicio del disco. Un programa que trata de leer un archivo asignado contiguamente, generará varias solicitudes cercanas en el disco, por lo tanto, el movimiento de las cabezas de lectura/escritura será muy limitado, sin embargo, si el archivo ha sido asignado de forma enlazada o indexada, puede incluir bloques dispersos por el disco, resultando una mejor utilización del espacio en disco, a costa de un mayor movimiento de las cabezas de lectura/escritura. Es importante también, la ubicación de los directorios y bloques de índices, la forma de apertura del archivo para poder usarlo y si es preciso realizar un alto número de búsquedas en el directorio. Si se tiene en cuenta, que los accesos a los directorios son muy frecuentes, estos deben situarse en la mitad del disco, ya que de esta manera, se reducen considerablemente el número de movimientos de las cabezas de lectura/escritura. Así por ejemplo, si una entrada del directorio esta en el primer bloque y los datos del archivo en los últimos bloques, la cabeza de lectura/escritura tiene que recorrer todo el disco, si el directorio esta situado en los bloques centrales del disco, como mucho se recorrería la mitad del disco. APUNTES DE SISTEMAS OPERATIVOS I A. GLEZ. DEL ALBA 9 TEORÍA DE LOS SISTEMAS OPERATIVOS Evidentemente, teniendo en cuenta estos aspectos, el algoritmo de planificación del disco, como todos los demás algoritmos, debe escribirse como un modulo separado, que permita reemplazarlo por otro algoritmo si es necesario. Como elección inicial podría utilizarse la planificación FCFS o bien la SSTF. La planificación SSTF es bastante habitual e interesante, sin embargo, los algoritmos SCAN y C-SCAN, son más apropiados para sistemas de gran uso del disco. ALGORITMOS DE PLANIFICACIÓN PARA DISPOSITIVOS DE CABEZA FIJA. Los algoritmos de planificación de disco que se han analizado anteriormente, es decir, el FCFS, y C-SCAN, todos ellos tienen por objeto, minimizar el movimiento de las cabezas de lectura/escritura, para reducir los tiempos de espera y de servicio. SSTF, SCAN Los dispositivos de cabeza fija, como son los tambores magnéticos, no presentan este problema, ya que no hay movimiento de las cabezas de lectura/escritura, ni tiempo considerable para la selección de una pista, por consiguiente, para estos dispositivos se emplean otros algoritmos. Las colas por sectores es un algoritmo para la planificación de los dispositivos de cabeza fija, que se basa en la división de cada pista en un número fijo de bloques, llamados sectores. La dirección del disco especifica en cada solicitud la pista y el sector, como el tiempo de posicionamiento es cero, para los dispositivos de cabeza fija, la mayor parte del tiempo de servicio es el tiempo de latencia. Para la planificación FCFS, suponiendo que todas las solicitudes están distribuidas uniformemente entre los sectores, la latencia esperada es medio giro. Así por ejemplo, supongamos que la cabeza de lectura/escritura se encuentra sobre el sector 2 y la primera solicitud de la cola es para el sector 12. Para atender esta solicitud tenemos que esperar a que el sector 12 pase por debajo de las cabezas de lectura/escritura. Si en la cola se presenta una solicitud para el sector 5 podemos atenderla antes, sin demorar la solicitud del sector 12. De esta manera, se mejora en gran medida la productividad, sirviendo una solicitud para cada sector conforme pase bajo la cabeza de lectura/escritura, aunque no se encuentre al inicio de la cola de espera. Las colas por sectores definen una cola para cada sector del tambor magnético. Cuando llega una solicitud para el sector i, se coloca en la cola del sector i y al pasar el sector por debajo de las cabezas de lectura/escritura, se sirve la primera solicitud en su cola. Las colas de sectores, se utilizan principalmente, con dispositivos de cabeza fija, aunque también pueden utilizarse en dispositivos de cabeza móvil, si hay más de una solicitud de servicio para una pista o cilindro en particular. Una vez que la cabeza de lectura/escritura se mueve a un cilindro, pueden atenderse todas las solicitudes referentes al cilindro sin tener que mover la cabeza de lectura/escritura, por lo tanto, las colas por sectores pueden usarse para ordenar varias solicitudes de un mismo cilindro. Por supuesto, como sucede con otros algoritmos de planificación, las colas por sectores tendrán efecto, solo si el sistema operativo, puede escoger entre varias solicitudes. ALGORITMOS PARA MINIMIZAR LOS TIEMPOS DE LATENCIA Y DE TRANSFERENCIA. El tiempo de latencia rotacional es difícil de minimizar, dado que la distribución de las solicitudes en sectores dentro de una pista es aleatoria, cabe la posibilidad de agrupar las peticiones por sectores, pero esto solamente daría resultados satisfactorios, en dispositivos sin tiempo de posicionamiento, ya que da lugar a un aumento de dicho tiempo. APUNTES DE SISTEMAS OPERATIVOS I A. GLEZ. DEL ALBA 10 GESTIÓN Y ADMINISTRACIÓN DE LA ENTRADA Y SALIDA Teniendo en cuenta que el tiempo de transferencia se debe a que hay que transmitir la información desde el dispositivo de E/S al buffer del controlador y después a la memoria principal. APUNTES DE SISTEMAS OPERATIVOS I A. GLEZ. DEL ALBA 11 TEORÍA DE LOS SISTEMAS OPERATIVOS Podría pensarse en eliminar este tiempo, haciendo que la información sea enviada directamente por el controlador a la memoria principal, pero esto es imposible, ya que una vez que damos comienzo a una lectura, el flujo de información se produce a velocidad constante y no podría soportar el hecho de que el bus de datos estuviera ocupado por otras operaciones. El tiempo de transferencia tiene un efecto muy importante sobre el tiempo de latencia, ya que en un principio, los sectores de una pista los podríamos numerar consecutivamente y asignar todos ellos a un fichero determinado. En estas circunstancias, los sectores contiguos del fichero, estarían físicamente contiguos en el disco, dando lugar al sistema de numeración no intercalado. Utilizando un sistema de numeración no intercalado del tipo descrito anteriormente, cuando la cabeza de lectura/escritura, ha terminado de leer un sector, estará situada justo al comienzo del sector siguiente, que debe ser leído a continuación. No obstante durante el tiempo de transferencia, muchos controladores no pueden hacer nuevas lecturas y el disco debe seguir rotando, colocándose en una posición intermedia de un sector consecutivo, con lo que al terminar ese tiempo, hemos de realizar una rotación adicional, para leer el sector siguiente, al de la última operación de lectura. El tiempo de transferencia da lugar, por lo tanto, a un aumento del tiempo de latencia, al ocasionar rotaciones adicionales del disco, que no serían necesarias si no existiera el tiempo de transferencia. Los tiempos de latencia y de transferencia, no pueden hacerse menores directamente, pero cabe la posibilidad de superponer ambas operaciones, para ello es necesario disponer de unos métodos de numeración de sectores más sofisticados, como los que se describen a continuación: 0 1 0 4 0 3 7 2 7 1 5 6 6 3 3 5 2 1 5 4 NUM. NO INTERCALADA 6 2 NUM. INTERCALADA 7 4 NUM. INTERCALADA DOBLE Como se puede observar en las figuras anteriores, en la numeración no intercalada los sectores están situados en el disco de forma contigua, por lo tanto, durante el tiempo de transferencia el disco girará y por lo tanto la lectura del sector siguiente, obligará a una rotación adicional. Con la numeración intercalada, se trata de situar consecutivamente los sectores, dejando un sector intercalado entre los sectores que tienen números consecutivos, de esta forma, si el disco durante el tiempo de transferencia gira como mucho un sector, se podrá leer la pista completa en dos rotaciones del disco. El sistema de numeración intercalado doble, se basa en dejar dos sectores intercalados, entre los sectores que tienen números consecutivos y se utiliza en sistemas con una velocidad de rotación del disco mayor, por lo tanto, si el disco durante el tiempo de transferencia, avanza más de un sector y menos de dos, el sector que puede leerse a continuación, sin rotaciones adicionales, es el que está situado dos posiciones por delante del leído anteriormente, de esta manera se podrá leer una pista completa en tres rotaciones del disco. APUNTES DE SISTEMAS OPERATIVOS I A. GLEZ. DEL ALBA 12 GESTIÓN Y ADMINISTRACIÓN DE LA ENTRADA Y SALIDA ORGANIZACIÓN DE LAS FUNCIONES DE ENTRADA Y SALIDA. Vamos a tratar de definir las técnicas, que pueden ser utilizadas para la organización de las operaciones de E/S, pero antes vamos a recordar, sus características más importantes. 1. La mayor parte de las operaciones de E/S se realizan de forma asincrona, es decir, se solicitan en cualquier momento y no mantienen ninguna relación con el reloj del procesador. Dada la necesidad de controlar la operación asincrona, el hardware de E/S, debe incluir señales especiales, que activen la CPU y los controladores del dispositivo, para indicarse mutuamente sus estados, intenciones y disponibilidad de datos y a estas señales se las denomina conjuntamente, señales de dialogo ( Handshaking). 2. La diferencia de velocidad entre la CPU y los dispositivos periféricos, ya apuntada anteriormente es de varios órdenes de magnitud, es decir, todos los dispositivos de E/S son mucho más lentos que la UCP, pero además, existe una gran variedad en lo que se refiere a la velocidad de los dispositivos de E/S. 3. Las conversiones entre formatos de datos, necesarias para saltar las incompatibilidades entre el procesador y los diversos periféricos, ya que algunos dispositivos requieren transferencia de datos de bytes o caracteres y otros esperan transferencias de datos en bloques de caracteres, además existen diferentes codificaciones de datos entre las cuales se pueden citar ASCII, EBCDIC y otras especificas para cada dispositivo. Los sistemas de E/S, se suelen clasificar de acuerdo con el nivel de intervención de la Unidad de Control del procesador en las operaciones de E/S y son posibles tres técnicas: Entrada y Salida Programada. Cuando el procesador esta ejecutando un programa y encuentra una instrucción de E/S, se produce una interrupción, se ejecuta la rutina de interrupción y como consecuencia se envía una orden de alto nivel al controlador, es decir al modulo de E/S correspondiente. Si la operación de E/S, se haya totalmente controlada por la unidad de control del procesador, es decir, arranca, dirige y termina la operación de E/S, en este caso, se dice que se está realizando una E/S programada, por lo tanto, el módulo de E/S llevará a cabo la acción requerida y luego activará los bits apropiados en el registro de estado del controlador o del módulo de E/S. En este caso el módulo de E/S, no lleva a cabo ninguna otra acción para indicar al procesador que la operación se ha realizado, es decir, no interrumpe al procesador, por lo tanto, será responsabilidad del procesador, comprobar periódicamente el estado del modulo de E/S, para saber si se ha completado la operación. Con esta técnica, el procesador es el responsable de extraer los datos de la memoria principal y situarlos en el buffer del controlador, cuando se va a realizar una salida, o de extraer los datos del buffer del controlador y situarlos en la memoria principal, cuando se va a realizar una entrada. Esta técnica se puede implementar con muy poco hardware y por lo tanto, existe en casi todos los sistemas informáticos, pero puede dar lugar a un rendimiento bajo, si la unidad de control del procesador consume mucho tiempo gestionando entradas y salidas. El software de E/S se escribe de manera tal que el procesador ejecute unas instrucciones, que le otorguen el control directo sobre la operación de E/S, incluyendo la comprobación del estado de los dispositivos, el envío de órdenes de lectura o escritura y la transferencia de los datos. APUNTES DE SISTEMAS OPERATIVOS I A. GLEZ. DEL ALBA 13 TEORÍA DE LOS SISTEMAS OPERATIVOS Entrada y salida dirigida por interrupciones. El problema de la E/S programada, es que el procesador tiene que esperar un largo tiempo a que el módulo de E/S en cuestión, realice la operación y este listo para recibir o transmitir más datos. El procesador mientras tanto esta esperando y debe interrogar repetidas veces estado del módulo de E/S, por tanto, el nivel de rendimiento del sistema, en conjunto, se degrada fuertemente. Una alternativa diseñada posteriormente para resolver consiste en que el procesador envíe una orden de E/S al módulo correspondiente para que este se haga cargo y la unidad de control del procesador mientras tanto realice operaciones más productivas. Esto requiere algo más de hardware, ya que el módulo de E/S, debe ser capaz de generar las señales correspondientes, para poder comunicar a la unidad de control del procesador la finalización de las operaciones de E/S que estaba realizando, produciendo de esta manera, una interrupción externa. Que permite a la unidad de control del procesador realizar la transferencia de la información a la memoria principal. La unidad de control del procesador seguirá siendo la encargada de arrancar la operación de pero una vez iniciada, la unidad de control del procesador y el módulo de E/S solo se interferirán, cuando quieran acceder a la memoria principal, para la transferencia de la información. E/S, Acceso directo a memoria (DMA, Direct Memory Access). La entrada y salida dirigida por interrupciones, aunque es más eficiente, que la simple E/S programada, todavía requiere de la intervención activa del procesador para transferir los datos entre la memoria y el módulo de E/S y además cualquier transferencia de datos debe recorrer un camino que pasa por el procesador. Así pues, ambas técnicas de E/S adolecen de dos desventajas inherentes: La velocidad de transferencia de E/S, esta limitada por la velocidad con la que el procesador puede comprobar y dar el servicio correspondiente a un dispositivo concreto. El procesador participa en la gestión de la transferencia de E/S y deben ejecutarse una serie de instrucciones en cada transferencia de E/S. Cuando se tienen que mover grandes volúmenes de datos, se necesita una técnica más eficiente, que consiste en el acceso directo a memoria DMA. La función de DMA se puede llevar a cabo, por medio de un módulo separado sobre el bus del sistema o bien puede estar incorporada dentro del módulo de E/S, en cualquier caso, la técnica funciona de la siguiente forma: Cuando el procesador desea leer o escribir un bloque de datos, emite una orden hacia el módulo DMA, enviándole la información siguiente: Si lo que se solicita es una lectura o una escritura. La dirección del dispositivo de E/S involucrado. La dirección inicial de la memoria desde la que se va a leer o a la que se va a escribir. El número de palabras o caracteres que se desea leer o escribir. El procesador continúa entonces con otro trabajo, delegando la operación de E/S, en el módulo de DMA y dicho módulo es el que tendrá que encargarse de llevar a cabo la operación de E/S. APUNTES DE SISTEMAS OPERATIVOS I A. GLEZ. DEL ALBA 14 GESTIÓN Y ADMINISTRACIÓN DE LA ENTRADA Y SALIDA El módulo de DMA transfiere el bloque entero o bien una palabra cada vez, directamente hacia o desde la memoria sin pasar por el procesador. Cuando se completa la transferencia, el módulo de DMA envía una señal de interrupción al procesador, de esta manera, el procesador se ve involucrado solo al inicio y al final de la transferencia. El módulo DMA debe tomar el control del bus de datos, para transferir la información a la memoria, por lo tanto, debido a la competencia por la utilización del bus de datos, puede ocurrir que el procesador necesite el bus de datos, cuando esta siendo utilizado por el módulo DMA y en este caso el procesador debe esperar. Es preciso observar que esto no es una interrupción, ya que el procesador no salva el contexto y se dedica a ejecutar otro proceso, sino que el procesador realiza una pausa durante un ciclo del bus y el efecto en general, es que el procesador es más lento durante una transferencia de DMA, no obstante, para una transferencia de E/S de varias palabras, la técnica DMA es bastante más eficiente que la E/S programada o la dirigida por interrupciones. En los grandes sistemas informáticos, que deben soportar un elevado número de dispositivos, se puede llegar a un grado de autonomía mucho más grande, dejando a la unidad de control del procesador, la posibilidad de conectarse a los controladores a través de un canal de E/S, denominado IOP (Input/Output Processor), consistente en un procesador especializado, para realizar las operaciones de E/S, reservándose únicamente la exclusiva responsabilidad de arrancar las operaciones de E/S y procesar los resultados. El propósito de un canal es conseguir, que los dispositivos sean tratados como virtuales, abstractos o transparentes y descargar en lo posible al procesador central del ordenador, del trabajo de utilizarlos directamente. Para ello, será preciso introducir unos elementos de hardware denominados procesadores de E/S (IOP) o canales. No está claro, cuando un módulo de E/S, alcanza el grado de IOP, pero debe tener las siguientes características: Posibilidad de trabajar por DMA e interrupciones. Capacidad de ejecutar programas sencillos escritos especialmente para ellos. Cuando el módulo de E/S en cuestión es un sofisticado IOP o canal de E/S, el concepto de DMA debe tenerse en cuenta con más razón. Los canales se manejan mediante comandos específicos, para realizar las operaciones de E/S, las cuales se suelen llevar a cabo con la ayuda de módulos DMA, de manera que, cuando se termina cada operación, el canal devuelve el estado correspondiente del dispositivo que la realizó, al mismo tiempo que interrumpe al procesador central. Estos canales o procesadores de E/S son muy simples, especializados y sin grandes exigencias de velocidad de procesamiento, resultando bastante más económicos que el procesador central de un sistema informático. Los canales pueden ser de varios tipos: Selectores, que permiten la gestión de varios dispositivos, pero solo pueden gestionar uno en cada momento, estos canales se emplean normalmente, para dispositivos de muy alta velocidad, como pueden ser los discos magnéticos. Multiplexores, que pueden trabajar con varios dispositivos, pudiendo transferir datos simultáneamente por todos ellos, como es lógico, se utilizarán con dispositivos lentos, como por ejemplo las impresoras o los terminales. Multiplexor por bloques, que se basa en las ventajas de los dos anteriores, permitiendo que puedan coexistir operaciones de E/S, sobre varios dispositivos de alta velocidad. El APUNTES DE SISTEMAS OPERATIVOS I A. GLEZ. DEL ALBA 15 TEORÍA DE LOS SISTEMAS OPERATIVOS funcionamiento interno de este tipo de canales se fundamenta, en la encuesta que se realiza sobre los dispositivos que se conectan al mismo. CONTROLADORES DE PERIFÉRICOS. A medida que los sistemas informáticos han evolucionado, se ha producido una tendencia creciente en la complejidad y sofisticación de cada componente individual. En ningún caso se hace esto más evidente que en las funciones de E/S y las etapas de su evolución pueden resumirse como sigue: El procesador controla directamente los dispositivos periféricos, esto se puede ver en dispositivos simples controlados por microprocesadores. Se añade un controlador de periféricos o módulo de E/S, el procesador utiliza la E/S programada sin interrupciones, en este caso, el procesador parece aislarse de los detalles específicos de las interfaces con dispositivos externos. Posteriormente, se considera la misma configuración, señalada en el punto anterior, pero empleándose interrupciones, en este caso, el procesador no tiene que desperdiciar el tiempo esperando a que se realice una operación de E/S, incrementando así la eficiencia. El módulo de E/S recibe el control directo de la memoria, a través de DMA, de esta manera, puede mover un bloque de datos a la memoria o desde la misma, sin que intervenga el procesador, excepto al principio y al final de la transferencia. El módulo de E/S es mejorado, para constituir un procesador separado con un conjunto de instrucciones, especializado para realizar la E/S. El procesador central (CPU), ordena al procesador de E/S, la ejecución de los programas de E/S en la memoria principal. El procesador de E/S localiza estas instrucciones y las ejecuta sin la intervención de la CPU. Esto permite a la CPU, precisar que una secuencia de actividades de E/S se vea interrumpida solo cuando haya terminado la secuencia entera. El módulo de E/S posee su memoria local y es de hecho un computador independiente. Con esta arquitectura se pueden controlar un gran número de dispositivos de E/S, con una participación mínima de la CPU. Un uso muy común de esta arquitectura, ha sido el control de las comunicaciones con terminales interactivos, en este caso, el procesador de E/S se encarga de la mayoría de las tareas implicadas en el control de los terminales. Un módulo de E/S, controlador de periférico, interfaz o tarjeta controladora, actúa como intermediario, entre la CPU y los periféricos, es decir, sirve de puente entre la incompatibilidad de señales entre la CPU y los periféricos pero además traduce las órdenes genéricas de E/S emitidas por la CPU, en unos controles específicos del dispositivo. Algunos controladores pueden gestionar varios dispositivos del mismo tipo o de tipos similares. Un controlador o módulo de E/S tiene la siguiente estructura: BUS DEL SISTEMA LÓGICA DE DIRECCIONES CAPA 1 INTERFAZ DEL BUS Y BUS DE DRIVERS CONJUNTO DE REGISTROS CAPA 2 DE DATOS, ORDENES Y ESTADO CONTROLADOR GENÉRICO DEL DISPOSITIVO PARTE DEL CONTROLADOR CAPA 3 INTERFAZ DEL DISPOSITIVO ESPECIFICA DEL DISPOSITIVO APUNTES DE SISTEMAS OPERATIVOS I A. GLEZ. DEL ALBA 16 GESTIÓN Y ADMINISTRACIÓN DE LA ENTRADA Y SALIDA DISPOSITIVO FÍSICO Las capas 1 y 3 son importantes para los diseñadores del hardware y la capa 2 tiene vital importancia para el sistema operativo. Al conjunto de registros que forman la capa 2, se le suele denominar puerto de E/S. Existen cuatro tipos fundamentales de registros en los controladores: Registros de memoria intermedia de entrada. Registros de memoria intermedia de salida. Registros de órdenes. Designación de modo. Ordenes operacionales de E/S. Registros de Estado. Registros de memoria intermedia de entrada. Su función principal es guardar un dato hasta que la CPU esté preparada para aceptarlo, ya que la CPU puede estar ocupada, cuando el dato esté disponible en el controlador. Si se dispone de memorias múltiples se pueden guardar varios datos. Registros de memoria intermedia de salida. Su función principal consiste en guardar los datos enviados por la CPU, de forma que los dispositivos externos, puedan contar con señales seguras adecuadas a sus requerimientos. Registros de órdenes. Existen dos tipos: Designación de modo, solo se modifica su valor cuando arranca el controlador, recibiendo el nombre de inicialización hardware, determinado el formato, que tendrá la información a transmitir, como por ejemplo el tipo de protocolo (sincrono o asincrono), longitud del carácter (7 y 8 bis), paridad (par o impar). Ordenes operacionales, que gobiernan el mecanismo de las transferencias de los datos, como por ejemplo: leer, escribir, habilitar o deshabilitar la transmisión. Las órdenes de la CPU alteran valores de bits individuales en estos registros. Registros de estado. Se utilizan principalmente para proporcionar informaciones a la CPU acerca del estado del dispositivo de E/S, como por ejemplo, ocupado o preparado. Estará ocupado cuando se pide una operación de entrada y el dispositivo no está disponible y estará preparado cuando el dato esté ya disponible para la CPU en el registro de memoria intermedia de entrada. ENTRADA Y SALIDA PROGRAMADA. Es el método más sencillo y directo de implementar los cambios de información y operaciones de E/S, consistente en responsabilizar a la unidad de control de todos los pasos necesarios para llevar a cabo una operación de E/S, es decir, cada dato transferido conlleva la ejecución de una o más instrucciones de la unidad de control. APUNTES DE SISTEMAS OPERATIVOS I A. GLEZ. DEL ALBA 17 TEORÍA DE LOS SISTEMAS OPERATIVOS La transferencia se realiza entre un registro de la unidad de control y un registro del controlador del periférico, ya que este no tiene acceso a memoria. Tanto la unidad de control, la memoria y los controladores periféricos, comparten los buses de datos y direcciones. APUNTES DE SISTEMAS OPERATIVOS I A. GLEZ. DEL ALBA 18 GESTIÓN Y ADMINISTRACIÓN DE LA ENTRADA Y SALIDA BUS DE DIRECCIONES BUS DE DATOS RD WR MEMORIA PRINCIPAL MEMRQ UNIDAD DE CONTROL IORQ CONTROLADOR DISPOSITIVOS La unidad de control del procesador es la que pone el contenido en el bus de direcciones y por lo tanto se emplearán para seleccionar un controlador igual que se selecciona una celda de memoria. Los controladores de dispositivos periféricos, incluyen un registro buffer (Registro de memoria intermedia), que hace que a efectos del procesador no haya diferencia física entre una posición de memoria y un controlador. La señal RD es para lecturas en memoria y entradas. La señal WR es para escrituras en memoria y salidas. Asignamos una parte del espacio de direccionamiento a la memoria y otra a los controladores. Así por ejemplo, de las direcciones 0000 a EEEE son de la memoria principal y desde F000 hasta FFFF pertenece a los controladores. Si deseamos que tengan distinto espacio de direccionamiento por ejemplo, 0000 será posición de memoria y también dirección de un controlador, por lo tanto, habrá que añadir dos señales para distinguir, cuando queremos acceder a memoria (MEMRQ) y cuando queremos acceder a un controlador (IORQ). Para llevar un dato desde el periférico a memoria es preciso realizar dos operaciones: Cargar el dato en un registro del controlador. Por ejemplo: IN A,(P). Esta instrucción llevará un dato desde el periférico nº P, hasta el registro A de la Unidad de Control. Almacenarlo en memoria. Por ejemplo: LD (HL), A. Carga en la dirección de memoria que apunta el registro HL, el valor del registro A. Para escribir un dato de memoria en un periférico se utilizarán operaciones similares. Almacenar en un registro del controlador, el contenido de una dirección de memoria. Por ejemplo: LD A, 1100 H almacena en el registro A el contenido de la dirección 1100 hexadecimal. Escribirlo en el periférico. Por ejemplo: OUT (P), A para hacerlo desde el registro A de la unidad de control, hacia el controlador nº P. Cuando se ejecuta una instrucción de este tipo: IN A, (P). Se supone que el controlador debe contestar en un tiempo marcado. APUNTES DE SISTEMAS OPERATIVOS I A. GLEZ. DEL ALBA 19 TEORÍA DE LOS SISTEMAS OPERATIVOS Hay sistemas que esperan hasta que el dato está en el buffer del controlador del dispositivo y otros en que pasado un momento, suponen que el dato está y lo leen. En la E/S programada la CPU está esperando a que los datos se acaben de leer o escribir, es decir, está continuamente preguntando al controlador, si se ha realizado la operación en su registro de estado. A esto se le llama bucle de espera activa, que conlleva una baja utilización del procesador y la dificultad de manejar dispositivos múltiples. Si el registro de estado está en 1, la CPU toma el dato y lo lleva a la memoria principal, en el caso de que sea una operación de lectura. Gestores de dispositivos de E/S controlada por programa. Los gestores de dispositivos en un S.O. se implementan como módulos de E/S que se enlazan normalmente al núcleo del sistema operativo. Una transacción típica de E/S controlada por programa tiene la siguiente forma: Inicializar el controlador (Solo si es necesario). Mientras leer datos Arrancar E/S Mientras no preparado Leer registro estado Fin Mientras. Bucle de Espera Activa Ejecutar la Rutina de Servicio El procesador, es decir la unidad de control del procesador, realiza la transferencia de los datos desde el registro de memoria intermedia de entrada del controlador a la memoria principal. Arranca la siguiente lectura y pone No Preparado el registro de estado del controlador, o el registro de estado del controlador se pone automáticamente a No Preparado en el momento de transferir el dato. Fin Mientras. CONTROL DE DISPOSITIVOS MÚLTIPLES. Para intentar controlar más de un controlador, que esté realizando E/S, vamos a expandir el bucle de espera activa, para comprobar el estado de los diversos controladores de E/S y bifurcar a la rutina de servicio de E/S adecuada, del primer controlador que se encuentre preparado. A este procedimiento se le denomina rutina de escrutinios y el bucle de espera activa sería: Comprobar registro estado controlador 1 Si preparado Ejecutar rutina servicio controlador 1 Fin-Si Comprobar registro estado controlador 2 Si preparado Ejecutar rutina servicio controlador 2 Fin-Si . . Comprobar registro estado controlador n Si preparado Ejecutar rutina servicio controlador a APUNTES DE SISTEMAS OPERATIVOS I A. GLEZ. DEL ALBA 20 GESTIÓN Y ADMINISTRACIÓN DE LA ENTRADA Y SALIDA Fin-Si Las rutinas de servicio del controlador, consisten en un conjunto de instrucciones, que realizan la E/S realmente y la rutina de servicio finaliza con una bifurcación a un punto concreto de la rutina de escrutinio, por lo tanto, cuando un controlador está preparado y se realiza la rutina de E/S, que corresponde a ese controlador, el regreso se puede hacer al comienzo de la rutina de escrutinio o bien a comprobar el estado del controlador siguiente en la rutina de escrutinio. Si se reanuda al comienzo de la rutina de escrutinio, aquellos controladores que están al comienzo, tendrán más prioridad, que los que se encuentran al final, ya que su petición siempre será atendida antes. Existen por lo tanto dos tipos de rutina de escrutinio: Rutina de escrutinio cíclica. Rutina de escrutinio por prioridades. Se puede definir el tiempo de latencia de escrutinio, como el tiempo transcurrido desde que un controlador indica que está preparado, hasta que su rutina de servicio comienza a ejecutarse, por lo tanto, en la implicación del tipo de escrutinio sobre el tiempo de latencia del controlador, solo se considera el tiempo correspondiente a la ejecución de la rutina, tiempo que denominamos t y eso quiere decir, que el tiempo de respuesta de E/S, está estrechamente relacionado, con la estrategia aplicada en la realización de la rutina de escrutinio. Rutinas de escrutinio por prioridades. Para el controlador de mayor prioridad, el tiempo de latencia en el caso más favorable será cero, mientras que el tiempo más desfavorable será t, de la última rutina de servicio ejecutada. Para el resto de controladores, su tiempo de latencia estará en función del comportamiento de los controladores de mayor prioridad, en el caso más favorable el tiempo de latencia será 0, cuando sea el único en estado preparado, respecto a los que tiene por encima; en el caso más desfavorable será infinito, cuando haya siempre controladores con mayor prioridad con su registro de estado preparado. Por lo tanto en una rutina de escrutinio por prioridades, puede producirse inanición, en la atención por parte de la CPU, de la rutina de servicios de algunos controladores, es decir, el controlador de mayor prioridad puede monopolizar la atención de la CPU. Rutinas de escrutinio cíclicas. Para todos los controladores de la rutina cíclica, el tiempo de latencia, más favorable será cero, y el caso más desfavorable será la suma de los tiempos de rutina de servicio anteriormente ejecutados. En principio, la noción de encuesta expuesta anteriormente, puede extenderse para proporcionar multitarea en un sistema de propósito general sin recurrir a las interrupciones, ya que la implantación de la rutina de escrutinio, esencialmente es una variante del bucle de espera activa explicado anteriormente y ello nos conduciría a una encuesta continua, que daría lugar a una baja utilización del procesador. La solución podría ser efectuar alguna actividad computacional en un segundo plano y ejecutar la rutina de escrutinio cada cierto tiempo. El problema sería determinar con que frecuencia realizar la rutina de escrutinio y como implementar esa frecuencia en un sistema de propósito general. Si la frecuencia en la ejecución de la rutina de escrutinio es muy alta, la rutina puede degenerar en un bucle de espera activa, manteniendo la mayoría de sus problemas ya que si se ejecuta muchas veces, puede ser que los controladores no hayan podido modificar el registro de estado. APUNTES DE SISTEMAS OPERATIVOS I A. GLEZ. DEL ALBA 21 TEORÍA DE LOS SISTEMAS OPERATIVOS Sin embargo, si la rutina de escrutinio se realiza con poca frecuencia, puede aumentar la utilización del procesador, pero al mismo tiempo puede aumentar los tiempos de latencia, reduciendo de esta manera el rendimiento del sistema y posiblemente, provocando perdidas de datos, por lo tanto, se llega a la conclusión de que la frecuencia correcta depende del sistema y de la configuración. Incluso si se resolvieran estas cuestiones y se eligiera una frecuencia para la rutina de escrutinio adecuada, seguiría existiendo el problema de la implementación, ya que fuese lo que fuese lo que el procesador estuviese haciendo, debería ejecutar la rutina de escrutinio a intervalos elegidos. En general, esto implicaría un análisis de tiempo cuidadoso de todos los programas, en términos de sus tiempos de ejecución, con el fin de asegurar, que las bifurcaciones a la rutina de escrutinio, se insertasen en los lugares adecuados, lo cual sería claramente irracionable en la práctica. Por ejemplo en un sistema operativo que gestiona la E/S controlada por programa para varios controladores mediante una rutina de escrutinio, se dispone de tres controladores: DISCO, CINTA e IMPRESORA, la duración de la rutina de servicio para cada controlador es: DISCO = 30 msg. CINTA = 100 msg. IMPRESORA = 500 msg. ¿Calcule el tiempo de latencia en el mejor y peor caso para cada controlador?. a) b) Suponiendo que la mayor prioridad es del disco, después la de la cinta y por último la de la impresora. En el caso más favorable: DISCO = 0 msg. CINTA = 0 msg. IMPRESORA = 0 msg. En el caso más desfavorable DISCO = 500 msg. CINTA = Infinito. IMPRESORA = Infinito. En el caso de rutina de escrutinio cíclica. En el caso más favorable: DISCO = 0 msg. CINTA = 0 msg. IMPRESORA = 0. En el caso más desfavorable: DISCO = 600 msg. CINTA = 530 msg. IMPRESORA = 130 msg. APUNTES DE SISTEMAS OPERATIVOS I A. GLEZ. DEL ALBA 22 GESTIÓN Y ADMINISTRACIÓN DE LA ENTRADA Y SALIDA ACCESO DIRECTO A MEMORIA (DMA) La gestión de la E/S por la unidad de control del procesador, explicada anteriormente, es decir, E/S programada, presenta serios inconvenientes, siendo el principal, que la unidad de control, está detenida durante mucho tiempo, esperando a que el controlador del dispositivo, le facilite el dato solicitado. No parece muy lógico, utilizar la unidad de control del procesador, para la realización de estas tareas o actividades, pero además no es solamente el problema de ineficacia que se produce, sino que si como es lógico, existen varios controladores de dispositivos periféricos, la lentitud de algunos dispositivos en contestar, a las solicitudes de lectura o grabación de la unidad de control, hará que otras solicitudes no pudieran ser atendidas en el momento oportuno. Los circuitos de acceso directo a memoria realizados por los módulos DMA y las interrupciones, se utilizan para mejorar la velocidad de las operaciones de E/S y eliminar así el papel de la unidad de control del procesador, en estas actividades. El acceso directo a memoria DMA, es una técnica de transferencia de datos, que tiene lugar normalmente, entre un controlador de E/S y la memoria principal y se realiza mediante un componente hardware específico, denominado controlador de DMA (DMAC). La CPU, puede realizar accesos a memoria de forma aleatoria, sin embargo, el controlador de DMA, solo puede acceder a conjuntos de posiciones de memoria consecutivas, por este motivo, el DMA es adecuado para la transferencia de bloques de datos. Si se trata de una operación de entrada de datos desde un dispositivo periférico, estos quedarán almacenados en el controlador, concretamente en un buffer de entrada o conjunto de posiciones de memoria intermedia consecutivas, por el contrario, si se trata de una operación de salida, se tomará de un buffer de salida o conjunto de posiciones de memoria intermedia consecutivas, para enviarlos al dispositivo periférico. Una de las características más sobresalientes del módulo DMA, es la eficiencia que se consigue, en lo que respecta a la velocidad de transferencia, ya que la transferencia de bloques es bastante más rápida que si se hiciera mediante un mecanismo de E/S programada. Sin embargo, lo más importante es que una operación DMA, se puede realizar de forma prácticamente concurrente con el funcionamiento de la CPU, por lo que la E/S puede no restar un tiempo significativo a la velocidad de ejecución del proceso, que se encuentre en el procesador en ese momento. A nivel hardware suelen existir varios controladores DMA, aglutinados por integración en un mismo chip VLSI, denominados canales, por ejemplo, el 8237A DMAC de Intel utilizado en los sistemas PC, que integra cuatro canales, del 0 al 3, que suelen funcionar de forma coordinada, utilizando un mecanismo basado en prioridades. El DMAC utiliza un reloj propio, que puede ser el mismo que controla la CPU u otro diferente. Además dispone de una entrada para la inserción de estados de espera, en caso de que sea preciso regular externamente su velocidad, adecuándola a los tiempos de acceso de la memoria y de los dispositivos periféricos. En la gestión de la E/S mediante la incorporación a los controladores del módulo DMA, la operación de E/S es arrancada por la unidad de control del procesador, permitiéndose al controlador la transferencia de bloques de datos, hacia o desde la memoria, el puerto de E/S de un controlador, para que pueda funcionar bajo DMA, contiene además de los registros de un controlador normal otros registros, necesarios para su funcionamiento. APUNTES DE SISTEMAS OPERATIVOS I A. GLEZ. DEL ALBA 23 TEORÍA DE LOS SISTEMAS OPERATIVOS El funcionamiento básico de un controlador de DMA, consta de los siguientes registros: Registro de Dirección Base, en el que se almacena la dirección de comienzo espacio de memoria involucrado en la transferencia. Registro de Datos a Transferir, en el que se almacena el número de datos que se van a transferir, es decir, el tamaño de cada bloque involucrado en la transferencia. Es preciso darse cuenta, que cada “dato” puede llegar a constituir una unidad superior al byte, según la configuración hardware del controlador utilizado. Registro de Direcciones, que consiste en un contador reversible, cuyo contenido tiene conexión directa al bus de direcciones. Cuando comienza una transferencia DMA, este contador, se incializa con la dirección almacenada en el Registro de Dirección Base. Según se haya programado la transferencia (mediante bits adicionales) este contador, cuenta en sentido ascendente y descendente. Contador de Datos Transferidos, que consiste en un contador, que siempre cuenta en sentido descendente. Cuando se inicia una transferencia DMA, el contador se inicializa con el valor almacenado en el Registro de Datos a Transferir y cuando la cuenta llega a cero, se da por terminada la operación, circunstancia que se señaliza por hardware. Resumiendo para el funcionamiento del controlador como módulo DMA es preciso incorporar a los registros del controlador genérico dos nuevos registros: Registro DIR, contiene la dirección de memoria a la cual se va a efectuar el siguiente acceso, cuando comienza la ejecución de DMA, la CPU carga este registro con la dirección a partir de la cual se van a leer o escribir los datos, este registro se incrementa cada vez que se produce un acceso del controlador a memoria. Registro CONT, contiene inicialmente el número de datos, que se van a transferir en la operación de DMA, el contenido se reduce cada vez que se transfiere un dato, desde la memoria al buffer del controlador o viceversa. Cuando el contenido de CONT es igual a cero, el controlador envía una señal de interrupción a la CPU, para indicarle que ha terminado la operación de E/S. Tanto la unidad de control, la memoria y los controladores de los dispositivos periféricos, comparten los buses de datos y direcciones. BUS DE DIRECCIONES BUS DE DATOS MEMRD MEMWR IORD IOWR MEMORIA PRINCIPAL UNIDAD DE CONTROL BUSRQ BUSACK CONTROLADOR INT DISPOSITIVOS APUNTES DE SISTEMAS OPERATIVOS I A. GLEZ. DEL ALBA 24 GESTIÓN Y ADMINISTRACIÓN DE LA ENTRADA Y SALIDA La unidad de control del procesador es la que pone el contenido de las ordenes en el bus de direcciones y por lo tanto se emplearán para seleccionar la memoria intermedia de un controlador igual que para seleccionar una celda de memoria principal y debe ser capaz de solicitar los buses del sistema, mediante una señal que se denomina (BUSRQ). Desde el punto de vista de la CPU, el DMAC se considera como un periférico más, por lo que tiene reservado un conjunto de direcciones en el mapa de E/S, para el acceso en lectura y escritura a sus registros. En este caso, cuando el DMAC es accedido desde la CPU, sus conexiones al Bus de Direcciones (selección de registro), Bus de datos (valor a leer y escribir), y a las líneas IORD# e I WR# se consideran entradas. El principal problema que se manifiesta en este esquema de conexiones a buses, es la posible competencia entre la CPU y el DMAC por el acceso a los buses del sistema, fundamentalmente al Bus de Datos y al Bus de Direcciones. Esta competencia se resuelve siempre a favor del DMAC, que deberá solicitar los buses del sistema a la CPU, mediante las señales BUSRQ, quien se los concederá siempre, activando la señal de confirmación BUSACK. Una de las principales diferencias entre la CPU y el DMAC, radica en el hecho de que este último, no lee ni escribe datos en el bus de datos, solamente se limita a ordenar la transferencia entre el dispositivo (R/W) y memoria (W/R) La unidad de control del procesador, debe de cargar los datos correctos en los registros DIR y CONT del módulo DMA, para que se pueda arrancar la operación de E/S. La unidad de control, cada vez que acaba un ciclo de CPU del proceso que esta ejecutando, observará el valor de BUSRQ para comprobar sí esa señal esta activa o inactiva. En caso afirmativo le concederá el bus de datos al módulo DMA, indicándoselo con la activación de la señal BUSACK, a este intercambio de señales que se produce, es a lo que se denomina ciclo de DMA. Una vez concedido el Bus de Datos, el DMA debe hacerse cargo de dicho bus y utilizar las señales necesarias para acceder a la memoria y realizar la transferencia. Cuando el módulo DMA haya realizado la transferencia, retira la señal BUSRQ y la unidad de control del procesador puede continuar utilizando el bus de datos en sus ciclos de CPU. Cuando finalice la transferencia totalmente, el módulo DMA enviará una señal a la unidad de control del procesador, denominada INT, indicando que la transferencia ha finalizado. Es necesario destacar que en el módulo DMA, las operaciones de transferencia de datos, tienen preferencia sobre el acceso a los Buses de Datos y Direcciones, con respecto a la unidad de control del procesador. Podemos definir como ciclo de DMA, el conjunto de operaciones de transferencia de datos, que se produce, durante el intervalo de tiempo en el que está activa la señal BUSACK. Como se observa en este método para el tratamiento de las operaciones de E/S, algunas funciones siguen siendo realizadas por la unidad de control del procesador y al controlador de DMA correspondiente al dispositivo, se le ha pasado la función de la transferencia de los datos a la memoria principal o viceversa. APUNTES DE SISTEMAS OPERATIVOS I A. GLEZ. DEL ALBA 25 TEORÍA DE LOS SISTEMAS OPERATIVOS Teniendo en cuenta que los Buses del sistema no pueden ser utilizados por el procesador y por el módulo DMA, para las transferencias a memoria, es preciso buscar formas de máximo aprovechamiento del Bus de datos, encontrándose distintos tipos de transferencia: Por Bloques, en cuyo caso toma el control del Bus de Datos y no lo suelta hasta que termina de transmitirse el bloque completo. Por ráfagas, en cuyo caso toma el control del Bus de Datos y transmite los caracteres que tiene en ese momento. Por robo de ciclos, en cuyo caso toma el control del Bus de Datos durante un ciclo, enviando una palabra cada vez. Transparente, que consiste en aprovechar los ciclos en los cuáles el procesador no utiliza el Bus de Datos. FASES DE UNA OPERACIÓN DMA. 1. La unidad de control del procesador, carga los registros DIR y CONT del módulo DMA, con la dirección inicial de memoria, a partir de la cual se va a efectuar el acceso y el número de unidades de información a transferir. 2. La unidad de control arranca la operación de E/S comunicándoselo al módulo de E/S, donde generalmente está incluido el módulo DMA. 3. Cuando el módulo de E/S, tiene disponible la información a transferir, en el registro de memoria intermedia, activa la señal BUSRQ y espera. La activación de la señal constituye una petición por parte del módulo DMA, de los buses de datos y direcciones. 4. Cuando la unidad de control del procesador concluye el ciclo de CPU actual, comprueba el estado de activación de la señal BUSRQ, si está activa envía al módulo DMA la señal BUSACK, indicándole a este que tiene disponibles los buses de datos y direcciones. A partir de este momento, la CPU no puede hacer uso de tales buses, aunque si puede seguir ejecutando operaciones en la ALU. 5. El controlador se hace cargo de los buses y transfiere el dato la memoria o viceversa, e incrementa el valor del registro DIR. 6. Si existe un nuevo dato disponible en el puerto de E/S para su transferencia, es decir CONT no es igual a cero, se repite de nuevo la acción de la fase 5. 7. Si no existe dato disponible en el controlador y el valor de CONT no es igual a cero, se retira la señal BUSRQ y el control de los buses de datos y direcciones es cedido de nuevo a la unidad de control del procesador. 8. Si no existen datos disponibles en el controlador y el valor de Cont es igual a cero, se retira la señal BUSRQ, se cede el control de los buses a la unidad de control y se envía la señal INT, que indica que la operación DMA ha terminado totalmente. En el caso de que existan varios controladores de dispositivo funcionando bajo DMA, debe existir un elemento hardware denominado controlador de DMA, que se encargue de dar una orden de prioridad a las distintas señales de petición de buses que le lleguen de los distintos controladores. ENTRADA Y SALIDA DIRIGIDA POR INTERRUPCIONES. Dentro del tratamiento de las operaciones de E/S, una interrupción externa o de hardware, es una señal enviada por un controlador de periférico al procesador, para indicarle, que la operación de E/S pendiente ha finalizado, por lo tanto, se puede ejecutar la rutina de interrupción por la unidad de control del procesador. APUNTES DE SISTEMAS OPERATIVOS I A. GLEZ. DEL ALBA 26 GESTIÓN Y ADMINISTRACIÓN DE LA ENTRADA Y SALIDA El sistema operativo debe disponer de los mecanismos adecuados, para guardar el estado de ejecución actual del proceso interrumpido, ejecutar la rutina de atención a la interrupción y continuar el proceso interrumpido a partir del estado en que se interrumpió. De esta manera la unidad de control no necesita realizar la encuesta definida anteriormente, sobre el registro de estado del controlador, para saber cuando se ha terminado una operación de E/S y por lo tanto, puede seguir ejecutando otros trabajos, hasta que el controlador le envíe una señal de interrupción, para indicarle que la operación de E/S ha finalizado, eliminando de esta manera, el bucle de espera activa. La E/S por interrupciones se diferencia de la E/S programada, en que evita el descenso de la productividad del procesador, ya que suprime el bucle de espera activa. Respecto a la diferencia con la E/S por DMA, hay que tener en cuenta que si la unidad de control del procesador está accediendo a memoria, el controlador no puede enviar el vector de interrupción por el bus de datos, siendo necesario esperar a que la unidad de control la acepte enviando la señal INTACK, que indica el reconocimiento de la interrupción, ya que como se ha expuesto anteriormente debe guardar, el contador de programa, el contenido de los registros, etc. Para que esto sea posible, se tiene que producir un cambio de contexto, para pasar a ejecutar la rutina de tratamiento de la interrupción, ya que cuando acabe esta rutina de interrupción, debe volver al lugar del programa donde lo dejó, es decir, no puede enviar la señal INTACK hasta que la instrucción en curso haya concluido, diferencia fundamental con la petición de buses de DMA que se realizaba robando uno o varios ciclos a la unidad de control, en el curso de la ejecución de la instrucción. La E/S mediante interrupciones tiene una pequeña desventaja, que es el tiempo adicional que supone el cambio de contexto, que se tiene que producir, para atender la interrupción externa. En esta forma de gestión de la E/S, la operación de E/S es arrancada por la unidad de control del procesador, dejando al controlador la realización de la operación de E/S. Cuando la información solicitada se encuentre en el puerto de E/S, el controlador envía a la unidad de control del procesador una señal de interrupción, para indicar que ya puede realizarse la transferencia de los bloques de datos, hacia la memoria, el puerto de E/S de un controlador, para que pueda funcionar de esta manera debe enviar una señal INT a la unidad de control del procesador y esperar a que esta le devuelva la señal de reconocimiento de la interrupción INTACK. Tanto la unidad de control, la memoria y los controladores periféricos, comparten los buses de datos y direcciones. BUS DE DIRECCIONES BUS DE DATOS MEMRD MEMWR IORD IOWR MEMORIA PRINCIPAL APUNTES DE SISTEMAS OPERATIVOS I UNIDAD DE CONTROL INT INTACK CONTROLADOR A. GLEZ. DEL ALBA 27 TEORÍA DE LOS SISTEMAS OPERATIVOS DISPOSITIVOS La unidad de control del procesador es la que pone el contenido de las órdenes en el Bus de Direcciones, por lo tanto, se emplearán para la realización de la operación de E/S y seleccionar la memoria intermedia de un controlador igual que para seleccionar una celda de memoria principal. La unidad de control del procesador, suspenderá el proceso que estaba realizando y se encargará la realización de la operación de E/S. En el caso de que existan varios controladores de dispositivo funcionando mediante interrupciones, debe existir un elemento hardware denominado controlador de interrupciones, que se encargue de dar una orden de prioridad a las distintas señales que le lleguen de los controladores. En este método se pueden considerar tres puntos importantes respecto a las interrupciones, ya que puede haber varios controladores interrumpiendo simultáneamente. 1. La unidad de control del procesador, debe ser capaz de identificar, que controlador ha generado la interrupción, para poder ejecutar la rutina de atención específica. 2. Determinar si se van a tratar interrupciones anidadas. 3. La unidad de control del procesador, debe ser capaz de establecer un orden de atención a las distintas interrupciones cuando estas se generen simultáneamente. Se trata de desarrollar estos puntos: 1. Para identificar la interrupción existen dos formas de determinar que controlador ha generado la interrupción: a) POLLING: Cuando la unidad de control recibe una señal de interrupción, interroga sucesivamente a cada uno de los controladores, para determinar cual de ellos ha generado la señal y en consecuencia ejecutar la rutina de atención a la interrupción. La rutina polling se diferencia de la rutina de escrutinio, utilizada en la E/S controlada por programa, en que en este caso, se tiene la seguridad de que al menos un controlador esta preparado. Este sistema es muy lento y por lo tanto se utiliza otra solución para resolver este problema, que es la vectorización. b) VECTORIZACIÓN, consiste en que el controlador del periférico envíe la señal de interrupción y simultáneamente, envía también a través del bus de datos, una clave ó código que identifica unívocamente la interrupción, a esta clave ó código, es a lo que denominamos vector de interrupción del controlador y se utiliza para reconocer dónde se encuentra en memoria la rutina de tratamiento de la interrupción. El número de bits (n) que se reserven para la identificación de los controladores, indicará el número máximo de estos que pueden conectarse directamente con vectorización (2n). Por ejemplo: si para cada controlador se reservan 5 bits, sólo puede haber 25, es decir, 32 controladores que pueden enviar vectores de interrupción, si se quiere trabajar con más habría que agruparlos y pasar por cada grupo una rutina de encuesta como polling. Una vez tomado el vector se completaría para señalar una celda de memoria, en donde residiría la rutina de tratamiento de la interrupción o incluso la dirección de la rutina. APUNTES DE SISTEMAS OPERATIVOS I A. GLEZ. DEL ALBA 28 GESTIÓN Y ADMINISTRACIÓN DE LA ENTRADA Y SALIDA 2. Tratamiento de Interrupciones. Si se utiliza una serie posiciones fijas para salvar el contexto de un proceso durante la ejecución de una rutina de tratamiento de la interrupción, no se podría admitir la atención de una nueva interrupción, ya que los valores salvados quedarían perdidos. Además si el controlador no desactiva la señal de interrupción INT, podría interrumpirse el mismo de forma indefinida. Para evitar esto problemas se utiliza una instrucción, Disable Interrupt (DI), para desactivar las interrupciones y otra Enable Interrupt (EI), para activar las interrupciones. Si se permite el anidamiento de las interrupciones, es necesario disponer de estructuras de almacenamiento dinámicas de tipo LIFO, es decir pilas. Si el anidamiento no esta permitido, basta con que exista un área de memoria de tipo estático (variables ó conjuntos de variables), para almacenar el contexto de ejecución hardware en el instante en que se produce la interrupción. I1 P0 I2 I1 P0 I2 I1 P0 I1 P0 Como se puede observar en la figura cuando la unidad de control recibe la interrupción I1, almacena en la pila el estado de ejecución del proceso que se está ejecutando (P0), comienza entonces a ejecutarse la rutina de atención a la interrupción (I1), cuando esta se está ejecutando, la unidad de control recibe una nueva interrupción (I2), en ese momento guarda en la pila el estado de ejecución de la rutina de atención a I1 y comienza a ejecutar la rutina de atención a I2, cuando finaliza la ejecución de esta rutina recupera la rutina de atención I1 y continua ejecutándola, una vez que esta ha finalizado, recupera de la pila de estado de ejecución a (P0) y continua ejecutando de nuevo el proceso. 3. Prioridad en la atención a interrupciones. En el caso de que se produzcan varias interrupciones de forma simultánea, habrá que establecer un sistema de prioridades, de tal forma que solamente una esté activa. En el caso de que el sistema trabaje bajo Polling, la prioridad está implícita en la rutina de escrutinio, en este caso solo es necesario una línea de interrupciones a la cual acceden todos los controladores. APUNTES DE SISTEMAS OPERATIVOS I A. GLEZ. DEL ALBA 29 TEORÍA DE LOS SISTEMAS OPERATIVOS BUS DATOS BUS DE DATOS CPU INT BUS DE DIRECCIONES INTACK CONTROLADOR 1 CONTROLADOR 2 CONTROLADOR N ..... IEI IEO IEI IEO IEI IEF ........... Cuando el sistema trabaja bajo vectorización pueden existir dos soluciones: Si todos los controladores comparten la misma línea INT a la unidad de control, la línea INTACK deberá ir pasando por todos los controladores uno tras otro. Después de la ejecución de una instrucción, si la unidad de control detecta que está activa la señal INT, entonces activa la señal INTACK. De esta forma el controlador i recibe esta señal y se la pasa al siguiente, solo si el no necesita servicio. Así la señal INTACK se propaga hasta el primero que solicita INT, siendo este el que pone su vector de interrupción en el bus de datos. De esta forma el controlador que esté más cercano en la línea de INTACK será el que tenga mayor prioridad. La segunda posibilidad sería que llegaran a la unidad de control tantas líneas INT como controladores existen. En este caso la unidad de control debe de disponer de una unidad de gestión de prioridad. Para gestionar la prioridad de los controladores, la CPU dispone de un componente, que se denomina gestor de interrupciones. El principal inconveniente de esta opción, es la limitación en cuanto al número de controladores con los puede trabajar la CPU, esta limitación será equivalente al número de líneas del gestor de interrupciones. Para solventar dicha limitación se utiliza un sistema mixto entre Polling y Vectorización, los controladores se agrupan por conjuntos y cada uno de ellos utiliza la misma línea de interrupción, cuando la CPU atiende la señal de interrupción de la línea, ejecuta una rutina Polling sobre los controladores del mismo grupo. En los grandes sistemas informáticos, se permite atender interrupciones por niveles, es decir, cada línea, podría atender de forma independiente a cualquiera de interrupciones. Para realizar esta opción, se necesita establecer una máscara, que especifique, que líneas se pueden interrumpir y cuales no. El registro de máscara de interrupciones está formado por una serie de bits, uno por cada línea de interrupción, de tal forma que cada bit corresponde a un nivel de interrupción, es decir, si está en 1 se permite y si está en 0 se inhabilita. APUNTES DE SISTEMAS OPERATIVOS I A. GLEZ. DEL ALBA 30 GESTIÓN Y ADMINISTRACIÓN DE LA ENTRADA Y SALIDA Como resumen se pueden indicar los pasos que hay que realizar en un subsistema de E/S, controlada por interrupciones. 1. La unidad de control del procesador, envía la orden de arranque al controlador especifico y continua con otro proceso. 2. Cuando la información está en el registro de memoria intermedia del controlador, este activa la señal INT. 3. Cuando la unidad de control del procesador finaliza la instrucción en curso y están permitidas las interrupciones, se realiza lo siguiente dependiendo de que las interrupciones se encuentren: Activadas (EI). Desactivadas (DI). Si están activadas, se realiza lo siguiente: Se realiza el cambio de contexto. Se identifica la fuente de interrupción: Por Polling. Por vectorización. Se ejecuta la rutina especifica de la interrupción. Finaliza la interrupción. Si están desactivadas, se impiden y se colocan en la cola de interrupciones. APUNTES DE SISTEMAS OPERATIVOS I A. GLEZ. DEL ALBA