DISPOSITIVOS METAL/ÓXIDO/SEMICONDUCTOR (MOS / MIS)

Anuncio

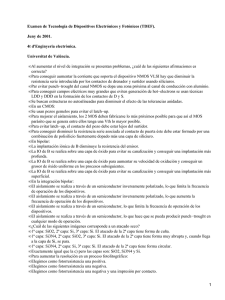

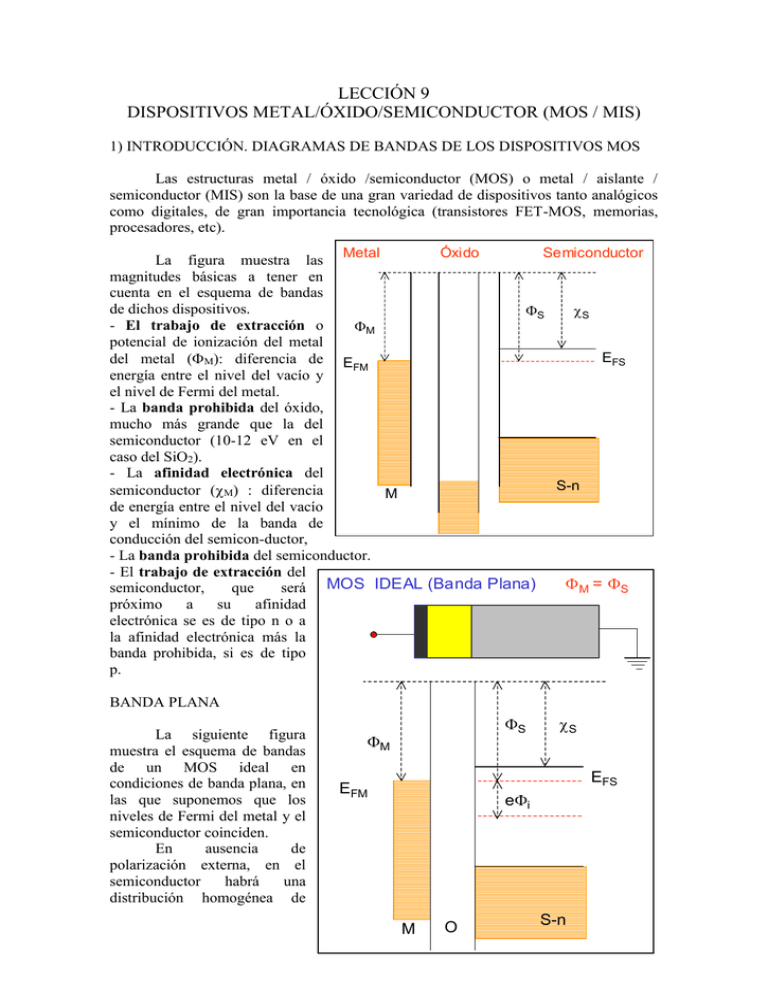

LECCIÓN 9 DISPOSITIVOS METAL/ÓXIDO/SEMICONDUCTOR (MOS / MIS) 1) INTRODUCCIÓN. DIAGRAMAS DE BANDAS DE LOS DISPOSITIVOS MOS Las estructuras metal / óxido /semiconductor (MOS) o metal / aislante / semiconductor (MIS) son la base de una gran variedad de dispositivos tanto analógicos como digitales, de gran importancia tecnológica (transistores FET-MOS, memorias, procesadores, etc). Óxido Semiconductor La figura muestra las Metal magnitudes básicas a tener en cuenta en el esquema de bandas de dichos dispositivos. S S - El trabajo de extracción o M potencial de ionización del metal EFS del metal (M): diferencia de E FM energía entre el nivel del vacío y el nivel de Fermi del metal. - La banda prohibida del óxido, mucho más grande que la del semiconductor (10-12 eV en el caso del SiO2). - La afinidad electrónica del S-n semiconductor (M) : diferencia M de energía entre el nivel del vacío y el mínimo de la banda de conducción del semicon-ductor, - La banda prohibida del semiconductor. - El trabajo de extracción del M = S semiconductor, que será MOS IDEAL (Banda Plana) próximo a su afinidad electrónica se es de tipo n o a la afinidad electrónica más la banda prohibida, si es de tipo p. BANDA PLANA La siguiente figura muestra el esquema de bandas de un MOS ideal en condiciones de banda plana, en las que suponemos que los niveles de Fermi del metal y el semiconductor coinciden. En ausencia de polarización externa, en el semiconductor habrá una distribución homogénea de S M S EFS EFM ei M O S-n portadores, y no habrá carga en ninguna de las interfaces (o "interficies"): metal/óxido , óxido/semiconductor. MOS -n IDEAL EN ACUMULACIÓN V>0 ACUMULACIÓN DE -PORTADORES V>0 --La siguiente figura muestra el esquema de bandas del MOS cuando aplicamos una tensión positiva al metal, que atrae electrones hacia la interfaz óxido / semiconductor. La diferencia entre los niveles de Fermi del metal y el semiconductor es igual a la EFS diferencia de potencial aplicada, eV multiplicada por la carga del EFM electrón. En una estrecha zona del semiconductor próxima a dicha interfaz se forma una zona de acumulación, en la que el nivel de Fermi penetra en la banda de conducción. Debido a la S-n O distribución inhomogénea de carga, en el semiconductor habrá un potencial de superficie (VS), M diferencia entre el nivel de Fermi en la interfaz y en la zona neutra del semiconductor. CARGA DE ESPACIO MOS -n IDEAL EN AGOTAMIENTO V<0 La siguiente figura muestra el esquema de bandas del MOS cuando aplicamos una tensión negativa al metal, que repele los electrones de la interfaz óxido / semiconductor. El nivel de Fermi se desplaza hacia el centro de la banda prohibida. En la zona del semicon-ductor próxima a dicha interfaz se forma una zona de agotamiento (carga de espacio), con una densidad de carga igual a la concentración de impurezas ionizadas. Al ir aumentando el valor absoluto de la tensión aplicada, se mantendrá esta situación de carga de espacio mientras el ++ ++ ++ V<0 EFM eV EFS M O S-n |Vs|<2i potencial de superficie sea inferior a (aproximadamente) el potencial i , diferencia entre el nivel de Fermi y el centro de la banda prohibida. INVERSIÓN DE PORTADORES La siguiente figura muestra el esquema de bandas del MOS cuando aplicamos una tensión negativa al metal, que repele los electrones de la interfaz óxido / semiconductor. El nivel de Fermi se desplaza hacia el centro de la banda prohibida. En la zona del semicon-ductor próxima a dicha interfaz se forma una zona de agotamiento (carga de espacio), con una densidad de carga. MOS -n IDEAL EN INVERSIÓN V<0 |V|>2i + ++ + ++ + + ++ + V<0 EFM eV EFS M O S-n 2) CAPACIDAD DE UN DISPOSITIVO MOS La figura muestra el esquema de bandas de un dispositivo MOS ideal a cierta tensión de polarización V. M O S-p EFS eV EFM Las cargas a ambos lados del aislante están distribuidas según muestran la siguiente figura, de manera que la carga QM en superficie del metal en contacto con el óxido debe ser igual a la carga en la zona de agotamiento del semiconductor. El campo y el potencial eléctricos en el dispositivo varía según la siguientes figuras. El potencial total aplicado se distribuye entre el óxido y el semiconductor: V Vox VS VS C MOS 1 1 Cox C S dox W QS=-eNAW E E=QS/S eN aW 2 2 s Por tanto, y dado que la caída de potencial en el dispositivo está distribuida entre el óxido y el semiconductor, las capacidades correspondientes están asociadas en serie: 1 QM V VS La capacidad del óxido, al tratarse de un aislante será (por unidad de superficie): Cox=ox/dox. Para calcular la capacidad asociada a la carga en el semiconductor es necesario resolver la ecuación de Poisson: d 2V ( x) e N A n( x) p( x) dx2 s s En cada punto la concentración de electrones y huecos dependerá del potencial V(x) y si suponemos que no hay degeneración: eV eV d 2V e kT kT N n e p e A p0 p0 2 dx s Esta ecuación diferencial puede integrarse multiplicando por dV: d 2V e dV 2 dx s eV eV kT kT N n e p e dV A p0 p0 Obteniéndose la siguiente ecuación: 2 1 dV e 2 dx s eV eV kT kT kT kT N V n e p e Cte A p0 p0 e e Para determinar la constante de integración, imponemos la de que en el límite de la zona de agotamiento o acumulación el campo y el potencial son nulos E 0 V 0 ): ( x W e kT kT 0 n p 0 p p0 Cte s e e lo que nos permite obtener el valor del campo eléctrico: 2 1 dV 1 e 2 E ( x ) 2 dx 2 s eV eV kT kT kT kT N V n e 1 p e 1 A p0 p 0 e e Si tomamos el valor del campo en la interfase y aplicamos el teorema de Gauss, Q E (0) S , obtenemos: S 1 QS 2 S eV eV e kT kTs kT kTS N AVs n p 0 e 1 p e 1 p 0 e e s 2 y la carga total por unidad de superficie en el semiconductor en función del potencial de superficie: QS s eV eV 2e kT kTs kT kTS e 1 p e 1 N AVs n p 0 p0 s e e A partir de esta ecuación resulta inmediato obtener la capacidad por unidad de superficie de la zona de carga en el semiconductor: s S 2e N A n p 0 e kT p p 0 e kT s eV CS dQS s dVS eV eV eV 2e kT kTs kT kTS e 1 p p 0 e 1 N AVs n p 0 s e e 2 Podemos ahora particularizar a cada una de las situaciones anteriormente descritas. - Acumulación (VS < 0) QS 2 s p p 0 kT e eVS 2 kT CS e 2 s p p 0 e eVS 2 kT 2kT La capacidad crece exponencialmente con la tensión. - Agotamiento (2i >VS > 0) QS s 2e s CS s N AVS 2e s NA 1 e s N A 2VS 2 VS La capacidad disminuye al aumentar VS. - Inversión (VS>2i) eVS QS 2 s n p 0kT e 2kT CS e2 s n p 0 2kT eVS e 2kT - Banda plana (VS=0) La sustitución directa daría un valor indeterminado por lo que aplicamos la ecuación para un potencial VS<<kT: eV eV 2e N A n p 0 (1 s ) p p 0 (1 s ) s kT kT CS s 2 2 2e kT eVs 1 eVs kT eVs 1 eVs 2 N V n p0 p p0 s A s e kT 2 kT e kT 2 kT Aplicando la ecuación de neutralidad del semiconductor en equilibrio térmico (NA=pp0np0) y recordando la expresión de la longitud de Debye: 2e s CS s p p0 eVs kT s s 2 LD p p 0 kT kT 1 eVs e 2 s s e 2 kT Como era de esperar, en condiciones de banda plana, el campo solo penetra en el semiconductor hasta una distancia de la superficie del orden de la longitud de Debye. Conocida la contribución del semiconductor, podemos calcular la capacidad del dispositivo MOS: 2 1 CMOS 2e p p0 1 1 Cox CS - Acumulación e inversión (CS >> COX) CMOS Cox ox d ox La capacidad del MOS es constante e igual a la del óxido. - Banda plana (CS ~ COX) 1 CMOS dox ox LD S CMOS ox S S dox ox LD - Agotamiento (CS < COX) CMOS CS Con estos cálculos previos la dependencia de la capacidad del MOS con la tensión sería la que muestra la curva BF en la siguiente figura: El hecho de que tengamos que distinguir entre BF (baja frecuencia) y HF (alta frecuencia) está relacionado con la respuesta de los portadores mayoritarios y minoritarios. En acumulación, la carga superficial es de portadores mayoritarios por lo que la carga acumulada varía rápidamente con las variaciones del campo. Igual sucede en agotamiento, ya que básicamente la carga se acumula al retirarse o acercarse los portadores mayoritarios. La situación es muy diferente en inversión, ya que la zona de inversión está separada de la zona neutra por una zona de agotamiento. A baja frecuencia, los portadores minoritarios pueden ser atraídos a la superficie desde la zona neutra o desde la zona de carga de espacio mediante mecanismos de generación térmica y la capacidad del MOS coincide con la del óxido. A alta frecuencia no hay tiempo para atraer los portadores minoritarios a la superficie y la capacidad del MOS queda bloqueada en la capacidad de la zona de carga de espacio, tal como muestra la siguiente figura: Toda la tensión continua aplicada cae en la zona de inversión, por lo que la zona de agotamiento se mantiene, a partir de VS=2i, a una tensión constante y la capacidad no varía. En agotamiento e inversión débil el MOS se comporta como una unión p-n abrupta y el potencial sigue una ley cuadrática: 2 eN AW 2 x V ( x) VS 1 VS 2 s W La anchura máxima corresponde pues al valor de VS al que empieza la inversión (VS=2i): 2 sVS 4 s i WMAX eN A eN A El valor de VS puede estimarse a partir de las ecuaciones de la estadística de electrones y huecos: 4 s kT ln( N A / ni ) kT N A WMAX VSMAX 2 i 2( Ei E F ) 2 ln e2 N A e ni El valor mínimo de la capacidad del semiconductor será Cs s / WMAX , y la del MOS: 1 C MOS d ox ox WMAX S C MOS ox d ox ( ox / s )WMAX 3.- CONDUCTANCIA DE UN CANAL DE INVERSIÓN: TRANSISTOR FET-MOS Uno de los dispositivos más importantes derivados de la estructura MOS es el transistor de efecto de campo FET-MOS, esquematizado en las figuras. Sobre un sustrato de tipo p se generan dos zonas de tipo n (la fuente S y el sumidero D). En el espacio entre ambas se deposita una capa de óxido y , sobre ella, un contacto metálico (la puerta G). VG>0 VG=0 VD VD G D G ID=0 S S n D n n Canal de inversión n n p p En ausencia de polarización de la puerta, entre S y G la resistencia es muy alta por tratarse de dos uniones p-n en oposición. Cuando G se polariza con una tensión positiva se genera una capa de inversión en la interfase que pone en contacto eléctrico la fuente y el sumidero, con una conductancia proporcional a la tensión de puerta. Podemos calcular dicha conductancia. Supongamos que la zona de inversión tiene una longitud l una anchura a y un grosor d. La conductancia será: G da da en l l Como lo que conocemos es la densidad de electrones por unidad de superficie, expresamos la conductancia en función de dichas densidad ns como limn0 (nd) : G e nd d 0 a a a ox enS VS l l l d ox ID VG4 VG3 VG2 VG1 La corriente fuente sumidero ISD, será a ox VSVD VD l edox La figura muestra la representación habitual de las características IDS(VSD) para diferentes tensiones de puerta, útiles en su aplicación como amplificador de alta impedancia de entrada (debido al aislamiento eléctrico entre la puerta y los otros terminales). I SD GVD e El transistor FET-MOS, usado en régimen de saturación o corte, es también la base de los circuitos biestables usados en electrónica digital, en memorias y procesadores. ID 4.- TIEMPO DE ALMACENAMIENTO: DISPOSITIVOS CCD Una de las más importantes aplicaciones de las estructuras MOS son los dispositivos CCD (dispositivos de acoplamiento por carga o de cargas acopladas). La base consiste en hacer trabajar un MOS en condiciones de inversión extrema fuera de equilibrio como depósito de cargas. Cuando un MOS se pone en condiciones de inversión extrema (a en la figura), se tarda cierto tiempo en alcanzar el equilibrio (b en la figura). Para calcular ese tiempo es necesarioconsiderar como se generan los portadores que van a formar la zona de inversión a partir de una trampa situada en el centro de la banda prohibida. Si suponenos que el tiempo de captura para electrones y huecos por la trampa es el mismo, la velocidad de recombinación será: pn ni2 C 2ni n p Cuando el MOS se polariza a cierta tensión de inversión los portadores son arrastrados fuera de la zona de carga de espacio por lo que p y n serán mucho menores que ni y quedará r ni / 2 C , lo que significa que la zona de inversión tardará en crearse un tiempo del orden de S N A / r 2N A C / ni . r 1 Para el silicio puro ese tiempo puede llegar a ser de varios minutos por lo que, durante ese tiempo (tiempo de almacenamiento) el MOS polarizado se comporta como un pozo de potencial en el que pueden almacenarse cantidades determinadas de carga generadas por inyección o por iluminación. Esta es la base de los dispositivos CCD (c en la figura). La siguiente figura ilustra una aplicación típica de un CCD en la que cierta carga se transfiere de un pozo de potencial a otro. a) Esta parte de la figura muestra la variación temporal de las tensiones que hay que aplicar a los electrodos A y B dos CCDs contiguas para transferir cierta carga electrónica del CCD A al CCD B. Obviamente, todos los tiempos han de ser inferiores al tiempo de almacenamiento antes definido. b) Para t<t1, la carga está acumulada en el CCD A que, al estar en inversión, es un pozo de potencial para electrones (tal como muestra c) d) Para t1< t<t1+ 1, se aplica una tensión V1 a b. Inicialmente el pozo B es más profundo y la carga empieza a ser transferida de A a B. e) El potencial en B empieza a subir al ir llenándose de electrones, por lo que t 1+ 1 < t<t1+ , se va despolarizando el CCD A para terminar la transferencia. f) Para t>t1+ la carga se ha transferido completanmente de A a B. 5.- TRANSISTORES MNOS (Metal/Nitruro/Óxido/Semiconductor) La figura muestra el esquema de una estructura MNOS (metal/nitruro/ óxido/semiconductor) que puede funcionar como memoria no volátil. Se basa en la posibilidad de almacenar cargas en la interfase entre dos capas aislantes (nitruro de silicio/óxido de silicio). Ese almacenamiento es posible porque en los aislantes el tiempo de relajación de Maxwell es muy largo. a) Proceso de escritura en una memoria MNOS: al aplicar una tensión positiva al metal, electrones del semiconductor pasan (por efecto túnel) de la zona de acumulación en la interfase O-S a las trampas de electrones en la interfase N-S donde pueden permanecer durante tiempso muy largos (años, incluso). b) Memoria activada: los electrones fijos en la interfase N-O repelen a los electrones y atraen a los huecos del semiconductor, dando lugar a una zona de inversión. c) Proceso de borrado: Una tensión negativa aplicada al metal hace que los electrones de las trampas sean transferidos al semiconductor. d) Memoria desactivada: al desaparecer la carga negativa en la interfase N-O, los electrones vuelven a formar una zona de acumulación en la interfase O-S. Para convertir este dispositivo en un transitor es necesario dotar de dos zonas p al dispositivo a ambos lados del canal conducto, con dos contactos eléctricos suplementarios (fuente y sumidero) tal como muestran las siguiente figuras. En la primera figura la memoria está desactivada y entre la fuente y el sumidero no pasa corriente (hay dos uniones p-n en oposición). VG=0 VD=VCC R VCC G D ID=0 S p+ Acumulación e- p+ n En la segunda, la memoria está activada y, debido al canal de inversión, la resistencia entre la fuente y el sumidero es muy pequeña. VG=0 VD=0 R VCC G D S p+ Canal de inversión ID=VCC/R p+ n Si se conecta una resistencia mucho más grande que la del canal de inversión entre la alimentación y el sumidero, en el primer caso la tensión V D será la de alimentación (el transistor está en corte: no circula corriente). Por el contrario en lal segunda la tensión será prácticamente cero (el transitor está en saturación : circula corriente entre la fuente y el sumidero). Estas situaciones corresponderían a los valores 1 y 0 si ese transistor se utiliza como bit de memoria.