Universidad Nacional de la Patagonia “S.J.Bosco”- Fac.de Ingeniería- Dto. Informática

ARQUITECTURA DE COMPUTADORAS

CAPÍTULO 001: INTRODUCCIÓN A LAS TÉCNICAS DIGITALES

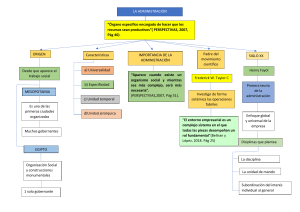

bINDICE

Temas:

1.1. Introducción

Pág. 1

1.2. Generalidades sobre Circuitos Lógicos

Pág. 1

1.3. Álgebra de Boole

1.3.1. Definiciones. Funciones básicas

1.3.2. Teoremas fundamentales

1.3.3. Teoremas de De Morgan

1.3.4. Generación, implementación y simplificación de

funciones booleanas

1.3.5. Otras funciones lógicas (XOR, NOR, NAND)

Pág. 2

Pág. 2

Pág. 3

Pág. 3

1.4. Ejemplos de Circuitos Combinacionales

1.4.1. Semisumador

1.4.2. Sumador completo de un bit (Full Adder)

1.4.3. Suma de 2 números de 4 bits

1.4.4. Codificadores

1.4.5. Decodificadores

1.4.6. Multiplexores

Pág.

Pág.

Pág.

Pág.

Pág.

Pág.

Pág.

1.5. Sistemas Secuenciales

1.5.1. Biestable RS

1.5.2. Biestable JK

1.5.3. Biestable D (Delay)

1.5.4. Ejemplo: Esquema de Memoria RAM

1.5.5. Registro de Desplazamiento

1.5.6. Flip Flop D Master Slave

1.5.7. Flip Flop JK Master Slave

Pág. 10

Pág. 10

Pág. 11

Pág. 12

Pág. 12

Pág. 13

Pág. 13

Pág. 14

1.6. Ejemplos de Sistemas Secuenciales Sincrónicos

1.6.1. Contador Sincrónico Módulo 8. Diseño e Implementación

1.6.2. Contador Sincrónico Módulo 5

Pág. 14

Pág. 14

Pág. 15

1.7. Resumen de Dispositivos digitales básicos

Pág. 16

Anexo I: Fabricación de circuitos integrados digitales.

Pág. A1

1

2

Pág. 3

Pág. 5

3

6

6

7

7

8

8

9

4

+5V

J

Q

CK

K

J

Q

CK

Q

K

J

Q

CK

Q

K

J

Q

CK

Q

K

Q

CK

Ing. José I. GALLARDO

Pág. 1

Universidad Nacional de la Patagonia “S.J.Bosco”- Fac.de Ingeniería- Dto. Informática

ARQUITECTURA DE COMPUTADORAS

CAPÍTULO 001: INTRODUCCIÓN A LAS TÉCNICAS DIGITALES

1.1.INTRODUCCION

Este capítulo referido a las técnicas digitales, tiene como objetivo, suministrar al

alumno los elementos básicos necesarios para la comprensión de aspectos técnicos

de la materia, sin pretender hacer de él un especialista en lógica ó electrónica.

Se tratan las herramientas del Algebra de Boole, como introducción a los sistemas

combinacionales, y la Teoría de Autómatas como introducción a los circuitos

secuenciales.

Se abordan luego los circuitos básicos de procesadores, como piezas elementales

para construir más adelante las distintas unidades de la máquina (computadora),

como son compuertas, flip-flops (biestables) y registros para conservar en memoria

la información, los buses y multiplexores para transferirlas, codificadores y

decodificadores para selección de memorias, y la etapa de sumador, como elemento

básico de todo operador aritmético.

1.2.GENERALIDADES SOBRE CIRCUITOS LÓGICOS

En las computadoras digitales, la información (info) procesada, de tipo binario, está

materializada por señales eléctricas de 2 estados, que pueden hacerse muy distintos

uno del otro, por ejemplo un nivel de tensión (voltage) para el estado “1”, y otro para

el estado “0”.

Ventajas de representación digital respecto de la analógica:

1. La información digital se transmite mejor, ya que un ruido pequeño puede perturbar

y alterar la info contenida en una señal analógica, mientras que una señal digital

puede ser perturbada y no perder su info, en la medida que sea posible distinguir el

estado “1” del estado “0”.

2. Se memoriza mejor pues es más simple realizar sistemas con 2 estados estables

capaces de memorizar un bit. Por el contrario, memorizar el valor de una señal

eléctrica analógica es mucho más difícil, por ejemplo,cargando un condensador.

Lógica de Nivel: se representa la info digital elemental sobre una línea eléctrica,

manteniendo una tensión A para materializar el “1” lógico, y una

tensión B para el “0” lógico.

En realidad no son valores exactos,sino franjas alrededor de

estos valores hay una zona intermedia con valores lógicos

indeterminados.

Se trabaja con Lógica Positiva cuando la tensión que representa

al “1” lógico es superior a la tensión del “0” lógico, y, en caso

contrario, se trabajará con lógica negativa.

La mayoría de las veces el “0” será la masa ó tensión 0 Volt.

La elección de los niveles de tensión resulta de la tecnología

escogida para la realización de circuitos (TTL, CMOS, etc).

Lógica de Impulsos: es cuando la magnitud eléctrica representativa de la info dura un

tiempo muy corto. El bit se reconoce por la presencia ó ausencia

de un pulso. La mayoría emplea solamente impulsos + ó -,e

imponen leer la info en instantes dados.

Ing. José I. GALLARDO

Pág. 2

Universidad Nacional de la Patagonia “S.J.Bosco”- Fac.de Ingeniería- Dto. Informática

ARQUITECTURA DE COMPUTADORAS

CAPÍTULO 001: INTRODUCCIÓN A LAS TÉCNICAS DIGITALES

Transmisión en Serie y en Paralelo: para transmitir una info codificada con n bits,

puede hacerse, bien transmitiendo los impulsos correspondientes unos detrás de

otros por un sólo hilo (Transmisión en Serie) ó bien transmitiéndolos

simultáneamente por distintos hilos. (Transmisión en Paralelo).

.Puede pasarse de un sistema paralelo a uno serie con ayuda de un dispositivo

Serializador. El inverso se llama Paralelizador.

Circuitos Combinacionales y Secuenciales:

.Un Circuito es un conjunto de componentes electrónico dotado de entradas y

salidas.

.Se llama Circuito Lógico ó de Conmutación a un circuito que trata señales lógicas.

.Un circuito es Combinacional cuando las señales de salida no dependen más que

de las de entrada, y será Secuencial, si las señales de salida dependen de las

señales de entrada y de la historia previa ó secuencia del sistema en el tiempo. Un

circuito secuencial contiene elementos de retardo ó de memoria.

.El estudio de los Circ. Combinacionales se basa en el Algebra de Boole y el de los

Circ. Secuenciales en la Teoría de Autómatas finitos.

1.3.ALGEBRA DE BOOLE

1.3.1.Definiciones:

Una Variable Lógica puede tomar un valor de entre dos distintos, que por

convención notaremos con los símbolos “0”y “1”

A {0,1}

Igualmente se dirá que A es cierta (ó Verdadera) si su valor es 1 ó Falsa en caso

contrario (A=0). Son sinónimos de Variable lógica, Var. Binaria ó Booleana.

Una Función Lógica (ó Booleana) es una función de n variables lógicas que toman

valores en el conjunto {0,1}

F(A1,A2, ...An) {0,1}

la función está perfectamente definida dando valores con c/u de las 2n

combinaciones posibles de las n variables.

El cuadro que presenta las 2 valores posibles de una función se llama Tabla de

Verdad de la función.

n

Función Lógica Inversión (ó negación ó NOT)

_

A F1

F1(A)= A

0 1

1 0

A esta función lógica básica, le corresponde un operador lógico que la

materializa eléctricamente: Símbolo del operador Inversión ó NOT, según

normas A.N.S.I. americanas. (ANSI / IEEE 91-1984 Símbolos de Compuertas)

Ing. José I. GALLARDO

Pág. 3

Universidad Nacional de la Patagonia “S.J.Bosco”- Fac.de Ingeniería- Dto. Informática

ARQUITECTURA DE COMPUTADORAS

CAPÍTULO 001: INTRODUCCIÓN A LAS TÉCNICAS DIGITALES

Función Lógica AND (ó producto lógico)

A B F2

F2(A,B)= A.B / F2=1 si A=B=1

0 0 0

0 1 0

: Operador AND

1 0 0

1 1 1

Función Lógica OR (ó suma lógica)

A B F3

0 0 0

0 1 1

1 0 1

1 1 1

F3(A,B)= A+B / F3=1 si A=1 ó B=1

: Operador OR

Toda función lógica puede formularsecomo una expresión compuesta por estas 3

funciones básicas ó fundamentales.

1.3.2.Teoremas Fundamentales del Algebra de Boole

A+1= 1

A+0= A

A.1= A

A.0= 0

_

A.A= 0

A.A= A

_

A+A= 1

Asociatividad:

(A+B)+C= A+ (B+C) (A.B).C= A.(B.C)

Conmutatividad:

A+B= B+A

Distributividad:

A.(B+C)= A.B + A.C A+(B.C)=(A+B).(A+C)

A+A= A

A.B= B.A

1.3.3.Teoremas de DeMorgan

Permiten encontrar el complemento de un elemento de expresión booleana.

_____ _ _

___ _ _

1.

A + B = A.B

2.

A.B= A + B

1.3.4.Generación, Implementación y Simplificación de Func. Booleanas

Dada una tabla de verdad que representea una función lógica, se puede extraer la

expresión booleana de dicha función, con las tres operaciones básicas vistas.

A B C F

0 0 00

__

0 0 1 1 F=1 ó cierta si A=0, B=0 y C=1 ó sea si A.B.C=1 ó cierto.

0 1 01

__

_ _

__

_

0 1 10

F= A.B.C + A.B.C + A.B.C + A.B.C

(1)

1 0 01

1 0 10

1a. Forma Canónica de representar a F como suma de minitérminos.

1 1 01

. Estas son las únicas situaciones en que F=1 es la C.N. y S.

1 1 10

_ ______________________

_ ___ _

_

Otra forma de representarla es cuando se hace cero: F=A.B.C+A.B.C+A.B.C+A.B.C y

aplicando Teor. de DeMorgan,

_ _ _

_ _ _ _

F= (A+B+C)(A+B+C)(A+B+C)(A+B+C) (2)

que constituye la 2da. Forma canónica de F, como producto de Maxitérminos.

Ing. José I. GALLARDO

Pág. 4

Universidad Nacional de la Patagonia “S.J.Bosco”- Fac.de Ingeniería- Dto. Informática

ARQUITECTURA DE COMPUTADORAS

CAPÍTULO 001: INTRODUCCIÓN A LAS TÉCNICAS DIGITALES

.Implementación:

.Simplificación: 1. El Método Algebraico consiste en utilizar los teoremas básicos del

Algebra de Boole.

1

2

3

4

2+4

1

3+4

__

_ _

__

_

_ _

_ _

_ _

Ejemplo: de (1) F= A.B.C + A.B.C + A.B.C + A.B.C = B.C(A+A) +A.B.C +A.C(B+B)=

_

_ __

F= B.C + A.C + A.B.C

(3)

2. Existen Métodos gráficos para facilitar las simplificaciones donde la

Tabla de Verdad puede organizarse en forma de una tabla llamada Diagrama ó Mapa

de Karnaugh, en honor a Maurice Karnaugh, quien lo propusiera en 1953 como

método de minimización de circuitos lógicos.

C

AB

0 1

Diagrama de Karnaugh de F: contiene toda la info de la Tabla

n

00

0 1

de Verdad. Se tienen 2 celdas (como combinaciones posibles

01

1 0

existen de las n variables) presentados en forma matricial.

11

1 0

10

1 0

Dos celdas adyacentes difieren entre sí en que una sola variable independiente ha

cambiado de estado. También son adyacentes las celdas de las esquinas, ya que se

pasa, por ejemplo, de ABC=001 a ABC=101 sólo cambia A.

Las celdas 4,5,6 y 7 definen el lugar geométrico del mapa en donde la variable

lógica A adopta el estado lógico “1” A.

Las otras 4 celdas _obviamente ponen de manifiesto el estado lógico “0”

complemento de A ó A.

En realidad no son figuras planas por la adyacencia de bordes, sino esféricas.

Entre 2 celdas adyacentes se elimina una variable lógica, siendo ella la que tiene

diferentes estados en las celdas contiguas.

Entre 4 celdas adyacentes se eliminan 2 variables independientes, siendo éstas las

que cambian de estado.

Una celda (20) define una expresión de 3 variables; el agrupamiento de 2 =21 celdas,

una expresión de 2 variables y, el agrupamiento de 4 =22 celdas define una

expresión de 1 variable.

Ing. José I. GALLARDO

Pág. 5

Universidad Nacional de la Patagonia “S.J.Bosco”- Fac.de Ingeniería- Dto. Informática

ARQUITECTURA DE COMPUTADORAS

CAPÍTULO 001: INTRODUCCIÓN A LAS TÉCNICAS DIGITALES

Se trata de lograr las figuras más grande posibles:

1º) de 8 celdas F=1

2º) de 4 celdas F(A)

3º) de 2 celdas F(A,B)

4º) de 1 celda F(A,B,C)

_

_ __

En resumen:

F= B.C + A.C + A.B.C

(4)=(3)

Ejemplo: Dada F(A,B,C,D) por su tabla de verdad simplificar por Diagrama de

Karnaugh Implementar circuito lógico.

AB

A B CD F

CD

00 01 11 10

0 0 0 0 0

00

0 1 1 0

0 0 0 1 0

01

0 0 0 0

0 0 1 0 1

11

1 1 1 1

0 0 1 1 1

10

1 0 0 1

0 1 0 0 1

0 1 0 1 0

_ _ _

0 1 1 0 0

F= B.C.D + B.C + C.D

0 1 1 1 1

1 0 0 0 0

Circuito Lógico:

1 0 0 1 0

1 0 1 0 1

1 0 1 1 1

1 1 0 0 1

1 1 0 1 0

1 1 1 0 0

1 1 1 1 1

1.3.5.Otras Funciones Lógicas

Función OR Exclusiva (XOR)

A B F4

0 00

0 11

1 01

1 10

_

_

F4(A,B)= A.B + A.B=AB/ F4=1 si AB

:Operador XOR

Esquemas en Suma de productos y en Producto de sumas:

Función lógica NOR

A B F5

0 0 1

0 1 0

1 0 0

1 1 0

Ing. José I. GALLARDO

___ _ _

F5(A,B)= A+B=A .B

:Operador NOR

Pág. 6

Universidad Nacional de la Patagonia “S.J.Bosco”- Fac.de Ingeniería- Dto. Informática

ARQUITECTURA DE COMPUTADORAS

CAPÍTULO 001: INTRODUCCIÓN A LAS TÉCNICAS DIGITALES

Función lógica NAND

___ _ _

A B F6

F6(A,B)= A.B=A +B

0 0 1

0 1 1

:Operador NAND

1 0 1

1 1 0

___

____ _ _

Interpretación de Leyes de DeMorgan: 1. A+B = A.B

___ _ _

2. A.B = A + B

Así cualquier función lógica se puede implementar con compuertas NOT,

NAND y NOR. De hecho los circuitos integrados más comunes implementan

estos tipos de compuertas ó gates.

1.4.EJEMPLOS DE CIRCUITOS COMBINACIONALES

1.4.1.Sumador de 2 números de un bit (Half-adder)

A B S C

0 0 0 0 S= F1 (A,B) y C=F2(A,B)

0 1 1 0

_

_

1 0 1 0 S= A.B + A.B = AB

1 1 0 1 C= A.B

Es un Semisumador ó sumador incompleto

(sin acarreo anterior)

Ing. José I. GALLARDO

A ? S

B

C

A

S

B

C

Pág. 7

Universidad Nacional de la Patagonia “S.J.Bosco”- Fac.de Ingeniería- Dto. Informática

ARQUITECTURA DE COMPUTADORAS

CAPÍTULO 001: INTRODUCCIÓN A LAS TÉCNICAS DIGITALES

1.4.2.Sumador Completo de un bit (Full-adder)

A B Ci S Co

__

_ _

__

_ _

_

__

0 0 0 0 0 S= ABCi + ABCi + ABCi + ABCi= Ci (AB + AB)+ Ci(AB + AB)

0 0 11 0

0 1 0 1 0 S= Ci [AB]

0 1 10 1

_

_

_

_

_

_

1 0 0 1 0 Co= ABCi + ABCi + ABCi + ABCi= Ci (AB + AB)+ AB(Ci+Ci)

1 0 10 1

1 1 0 0 1 Co= Ci(AB) + AB

1 1 11 1

Circuito lógico del sumador completo:

A

B

S

Ci

Co

1.4.3.Suma de dos nros. de 4 bits

Debido al empleo de circuitos integrados y a la realización de lógicas celulares, se

reduce el nº de circuitos de base, entonces se toma el circuito anterior como un

bloque sumador completo y encadenando sumadores completos, realizamos un

sumador de 4 bits.

A su vez, con estos nuevos bloques, podrían sumarse números de cantidad de bits

múltiplos de 4.

1.4.4.Codificadores

Son sistemas combinacionales en los cuales en un determinado instante, una sola

de sus entradas está activa (una que se diferencia del estado normal de las demás).

La cantidad de salidas es suficiente para que a cada entrada activa, le corresponda

una combinación de salidas diferentes.

E1

E2

C1

.

C2

n entradas m salidas / 2m n

.

Cm

En

.Ejemplo: codificador de 10 teclas (de 0 al 9) como entradas y la salida es el código

BCD correspondiente. Tabla de verdad restringida para respetar que una

10

sola entrada =1 por vez, sino se plantea tabla de 2 combinaciones.

Ing. José I. GALLARDO

Pág. 8

Universidad Nacional de la Patagonia “S.J.Bosco”- Fac.de Ingeniería- Dto. Informática

ARQUITECTURA DE COMPUTADORAS

CAPÍTULO 001: INTRODUCCIÓN A LAS TÉCNICAS DIGITALES

Circuito Lógico:

b0

b1

b2

b3

_

_

_ _ _ _ _

.Si el cambio se hace con Ei=0, y el estado normal es Ei=1, b0= E1 +E3 +E5 +E7 +E9 ..

1.4.5.Decodificadores

m

.Se tienen m entradas y N salidas>m / N 2 ,

E1

S1

y c/u de las salidas se activa solamente para

E2

S2

una combinación de entradas determinadas.

.

Em

SN

.Ejemplo: Decodificador de 3 bits de entrada a 8 líneas de salida / para cada

combinación de entradas se active una salida diferente.

E2 E1 E0 S7 S6 S5 S4 S3 S2 S1 S0

__ _

0 0 0 0 0 0 0 0 0 0 1 S0= E2E1E0

_ _

0 0 1 0 0 0 0 0 0 1 0

_ _

S1= E2E1E0

0 1 0 0 0 0 0 0 1 0 0

S2= E2E1E0

_

0 1 1 0 0 0 0 1 0 0 0

__

S3= E2E1E0

1 0 0 0 0 0 1 0 0 0 0

S4= E2E1E0

_

1 0 1 0 0 1 0 0 0 0 0

_

S5= E2E1E0

1 1 0 0 1 0 0 0 0 0 0

S6= E2E1E0

1 1 1 1 0 0 0 0 0 0 0

S7= E2E1E0

Ing. José I. GALLARDO

Pág. 9

Universidad Nacional de la Patagonia “S.J.Bosco”- Fac.de Ingeniería- Dto. Informática

ARQUITECTURA DE COMPUTADORAS

CAPÍTULO 001: INTRODUCCIÓN A LAS TÉCNICAS DIGITALES

1.4.6.Multiplexor y A.L.U.

Se suponen 2 variables lógicas A y B, que ingresan a una serie de circuitos que

evalúan distintas funciones lógicas y aritméticas.

el Circuito Multiplexor elige una sola de las entradas (OR, AND, ...) en función

de los códigos C0C1C2, y la transmite a la salida habilitándola.

S= f (A,B, C0 ,C1,C2)

en función del código de selección,

será S una función aritmética ó

lógica de las presentadas.

Este sistema combinacional es un

esquema de Unidad Aritmético-Lógica

ó A.L.U.

Para n bits, se acoplan n circuitos

como éstos y el código de selección

puede ser el mismo para todos.

A

B

AND

AB

OR

NOT

A+B

_

A

_

B

+

A+B

NOT

-

S

A-B

DECODIF

Multiplexor

C0C1C2

Ing. José I. GALLARDO

Pág. 10

Universidad Nacional de la Patagonia “S.J.Bosco”- Fac.de Ingeniería- Dto. Informática

ARQUITECTURA DE COMPUTADORAS

CAPÍTULO 001: INTRODUCCIÓN A LAS TÉCNICAS DIGITALES

1.5.SISTEMAS SECUENCIALES

Concepto de Autómata Finito: los autómatas son entes matemáticos que permiten

dar un soporte teórico a numerosos desarrollos relacionados con la informática:

teoría de circuitos, de algoritmos, de lenguajes formales,etc.

Aquí restringiremos su estudio a verlo como una “caja negra”, con entradas y

salidas, desde el punto de vista externo.

Notaremos, E: conjunto de entradas

S: conjunto de salidas

t, t+1, t+2,... : instantes de observación discretos

S(t+1)= F [H(t), E(t)]

donde:

S(t+1)= salida en t+1,

E(t)= estímulo en t

H(t)= historia previa del sistema ó secuencia,que sólo toma un nº

finito de Estados Internos anteriores, por ej.valores S(t) anterior.

* Así en los Sistemas Secuenciales, el valor

de la salida para una dada combinación

de entradas, dependerá de la historia ó

secuencia previa del sistema, dada por

una serie de variables de estado interno.

Hay una memoria en el sistema.

Entradas Sistema

Secuencial

Salidas

Estado Interno

La memoria más elemental es una línea de retardo con 2 compuertas NOT, que

forman un circuito estable en “1” ó “0”. Es el principio de funcionamiento del

biestable, que en ausencia de estímulos externos no cambian de estado.

1.5.1.Biestable RS

Circuito formado por 2 compuertas NOR en oposición.

_

Si _S=R=0 (estado de reposo), entonces continúa en su estado actual: Q=0 y Q=1

ó Q=1 y Q=0. Se nota: Q t+1= Q t ( El circuito equivale a dos NOT en oposición).

_

Si S=1 (se envía impulso por entrada Set= Poner en uno) y R=0, irá al estado Q=0 y

Q=1, que permanece estable, aún cuando el impulso desaparezca.

_

Si R=1 (impulso Reset=Poner a Cero), y S=0, irá al estado Q=1 y Q=0, también

estable.

_

Si R=S=1 Q=Q=0, pero cuando las entradas vuelvan a cero, el biestable

recuperará uno de los dos estados estables, aquél que dependa de la entrada que

primero desaparezca. Por ello, se prohíben enviar impulsos por R y S

simultáneamente, pues su estado final es indefinido.

Ing. José I. GALLARDO

Pág. 11

Universidad Nacional de la Patagonia “S.J.Bosco”- Fac.de Ingeniería- Dto. Informática

ARQUITECTURA DE COMPUTADORAS

CAPÍTULO 001: INTRODUCCIÓN A LAS TÉCNICAS DIGITALES

Se resume su comportamiento en su Tabla de Estados

Tabla de Estados: S R Qt Qt+1 Transición

T.Estados

S R Qt+1

0 0 0 0

No cambia

Reducida

0 0 Qt

t+1

t

0 0 1 1

Q =Q

0 1 0

0 1 0 0

Se Resetea

1 0 1

0 1 1 0

1 1 *

1 0 0 1

Se setea

1 0 1 1

1 1 0 *

Indefinido

También se pueden deducir las Ecuaciones características del biestable RS:

_

_

_____

t+1

t

t+1

Q = Q + R y, Q = S + Q t , de donde:

_____

_

_

_____

_ _

t+1

t

t

t+1

t

t

Q = (S+Q ) + R = (S+ Q ).R

y

Q = S+ Q +R= (R+ Q ).S

_

_

_ _

Q t+1= (S+ Q t).R

y

Q t+1=(R+Q t).S

Este circuito se comporta como elemento de memoria, capaz de conservar una

información binaria, recibida en forma de impulso.

Por convención, el Estado_del biestable RS, es el estado de la salida Q. La otra es

la salida complementaria (Q).

Símbolos de Flip Flop RS:

_

Q Q

_

Q Q

_ _

R S

R S

Los círculos en las entradas indican que son activadas en cero.

1.5.2.Biestable JK

Principio de funcionamiento: las entradas J y K se comportan como Set y Reset,

respectivamente, con la diferencia que si rec_iben impulsos simultáneos en ambas

(J=K=1), la salida va al valor opuesto ( Q t+1= Q t).

K

R

_

Q

K

_

Q

J

Q

Símbolo:

J

S

Q

_

Ecuaciones: Biestable RS Q = (S+Q ).R _

Puertas AND R=K.Q t y S= J.Q t

_

_ _

Q t+1= (J.Q t + Q t)(K + Q t)

t+1

Tabla de Estado:

J

0

0

1

1

Ing. José I. GALLARDO

t

_

____

Q t+1= (J.Q t + Q t).K.Q t

K Q t+1

0Qt

10

01

1 /Q t

Pág. 12

Universidad Nacional de la Patagonia “S.J.Bosco”- Fac.de Ingeniería- Dto. Informática

ARQUITECTURA DE COMPUTADORAS

CAPÍTULO 001: INTRODUCCIÓN A LAS TÉCNICAS DIGITALES

1.5.3.Biestable D (Delay) Latch

Es usual que el biestable sirva para muestrear una determinada señal y almacenar

su valor. En el caso que la entrada sea disparada por nivel se denomina Latch D, y

por impulsos: Flip Flop.

D

Clk

S

R

Q

_

Q

Si Clk=0

S=R=0

Q

Cdo Clk=1,

si D=1

si D=0

S=1 y R=0 Q=1

S=0 y R=1 Q=0

t+1

t

= Q anterior

entonces la salida Q sigue a la entrada ó señal D cuando Clk=1.

Cuando el Clk vuelve a cero, Q t+1= Q t, memorizando la última entrada D.

Puede ser la celda más simple de memoria. Así, con varios latches D en paralelo,

puedo procesar bits en paralelo con una señal de habilitación común a todos

llegamos al concepto de Registro.

Ent

D

Q

Ck

Ent

D

Ck

Q

Ent

D

Ck

Q

Ent

D

Ck

Q

Clk

1.5.4.Esquema de Memoria RAM

Se puede armar así la estructura de una memoria RAM con un Decodificador, un

conjunto de AND’s y de latches D:

Entrada de Datos

n filas x m columnas

n palabras de m bits

Ejplo: n=256, m=8

Ram de 256 bytes

Ing. José I. GALLARDO

Pág. 13

Universidad Nacional de la Patagonia “S.J.Bosco”- Fac.de Ingeniería- Dto. Informática

ARQUITECTURA DE COMPUTADORAS

CAPÍTULO 001: INTRODUCCIÓN A LAS TÉCNICAS DIGITALES

Cada punto de conexión :::::::: es controlado por un latch, que se activa con la línea

de selección correspondiente, y pone Q=1, activando la And de salida de datos hacia

las OR finales, donde se leerá el dato seleccionado.

Si queremos Leer ESC=0 ANDI de Clk=0 Qt+1=Qt (igual a D ó Dato anterior)

y se habilitan las AndII con la línea seleccionada por el

decodificador, leyendo en las Or su contenido Datos.

Si queremos Escribir ESC=1 y en Data Input se coloca lo que se quiere grabar

que entra por los latches D.

ESC=1 habilita el Clk cuando

seleccione la línea y ahí se grabará el Dato I en los latches D

de esa línea ó palabra.

Esto sería una memoria RAM (de Acceso Aleatorio) de lectura/escritura, vista como

un tipo especial de sistema secuencial.

1.5.5.Registro de Desplazamiento

Si interconectamos varios latches en cascada, logro un “Registro de

Desplazamiento”, tal que a cada pulso de Clock, la información se desplaza una

posición.

tClk < tProp

El problema es que hay que hacer el ancho de pulso de Clock más angosto que el

tiempo de propagación de la entrada a la salida, para que avance un paso por vez,

por lo que al no ser totalmente confiable, se crea el Latch Master-Slave (MaestroEsclavo), donde el latch elemental está formado por dos latches.

1.5.6.Flip-Flop D Master-Slave

Mientras Clk=0, Q1=Q1ant=S’ [Bloqueado]

Cdo Clk=1 S Bloqueado y estable en

el valor anterior S=Q2=Q2ant ;

S’=E

E

Clk

Master

Slave

D

Q1 S’ D

Q2 S

Clk

Clk

Cdo Clk=0 S’ estable en valor anterior

S=S’ (Esclavo copia al maestro)

S=E durante el flanco de bajada del Clock.

S’=E “

“

“

“ subida del Clock, donde lo memoriza

Con estos FF D Master-Slave, se garantiza el funcionamiento paso a paso del

registro de desplazamiento.

Registros de desplazamiento se aplican para:

Conversión Paralelo a Serie,

Procesamiento Aritmético x2 y /2, que implican desplazamientos a Izquierda

un lugar (x2) ó a derecha (/2)

Ing. José I. GALLARDO

Pág. 14

Universidad Nacional de la Patagonia “S.J.Bosco”- Fac.de Ingeniería- Dto. Informática

ARQUITECTURA DE COMPUTADORAS

CAPÍTULO 001: INTRODUCCIÓN A LAS TÉCNICAS DIGITALES

1.5.7. Flip-Flop JK Master-Slave

Se emplea mismo concepto de Master-Slave usado para latches D.

Estos FF Master-Slave JK ó D, son Sistemas Secuenciales Sincrónicos

elementales, pues realizan solamente cambios de estado en determinados instantes,

en sincronismo con una señal de sincronización (Clk).

En cambio los RS comunes (de 2 NOR en oposición), responden inmediatamente a

las modificaciones de las entradas, en forma arrítmica, son Sistemas Secuenciales

Asincrónicos, que en gral son más simples, pero más inestables frente a ruidos, y

más rápidos que los sincrónicos.

Los Sist. Sec.Sincrónicos son en gral:

más complicados

más inmunes a ruidos

más lentos(limitados por veloc.clk)

1.5.8. Representación del Flip-Flop JK Sincrónico

Set Asincrónico

S

J

_

K

Q

Q

R

Reset Asincrónico

1.6.Ejemplos de Sist. Sec. Sincrónicos

1.6.1. Contador Sincrónico de Módulo 8:

Por el Método de la Tabla de Transición del FF JK

t+1

Estado Q2

0

1

2

3

4

5

6

7

0

0

0

0

1

1

1

1

Q1t+1 Q0t+1 J2t K2t J1 K1 J0 K0

0

0

0 * 0 * 1 *

0

1

0 * 1 * * 1

1

0

0 * * 0 1 *

1

1

1 * * 1 * 1

0

0

* 0 0 * 1 *

0

1

* 0 1 * * 1

1

0

* 0 * 0 1 *

1

1

* 1 * 1 * 1

Qt Qt+1 Jt K t

0 0

0 *

0 1 1 *

1 0

* 1

1 1

* 0

Analizando Qi salida, vemos qué se

necesita en Ji y Ki en el tiempo t, para

t+1

que en t+1, obtener Qi 6 Mapas Ki .

Tabla de Estados del Contador

t

t

t

J0=K0=1,

J1=K1= Q0 ,

J2=K2= Q0 .Q1

_

Cdo Clk=1 Q0t+1= Q0t;

_

Q1t+1= Q1t ,si Q0t=1;

_

t+1

t

t

t

Q2 = Q2 , si Q0 = Q1 =1 los tres FF

cambian de estado en el mismo instante.

Ing. José I. GALLARDO

Pág. 15

Universidad Nacional de la Patagonia “S.J.Bosco”- Fac.de Ingeniería- Dto. Informática

ARQUITECTURA DE COMPUTADORAS

CAPÍTULO 001: INTRODUCCIÓN A LAS TÉCNICAS DIGITALES

Mapas de Karnaugh de J2

Q2Q1\Q0

00

01

11

10

0

0

0

x

x

y K2

Q2Q1\Q0

00

01

11

10

1

0

1

x

x

J2=Q0.Q1

0

x

x

0

0

1

x

x

1

0

K2=Q0.Q1

1.6.2. Contador Sincrónico Binario de Módulo 5:

Se plantea la Tabla de Estados del contador, tal que se decodifica el último estado

(5º) , y al próximo pulso de clock, coloco todos en cero.

t+1

Estado Q2

0

1

2

3

4

0

0

0

0

0

1

0

t+1

Q1

0

0

1

1

0

0

t+1

Q0

0

1

0

1

0

0

t

t

J2 K2 J1 K1 J0 K0

0 * 0 * 1 *

0 * 1 * * 1

0 * * 0 1 *

1 * * 1 * 1

* 1 0 * 0 *

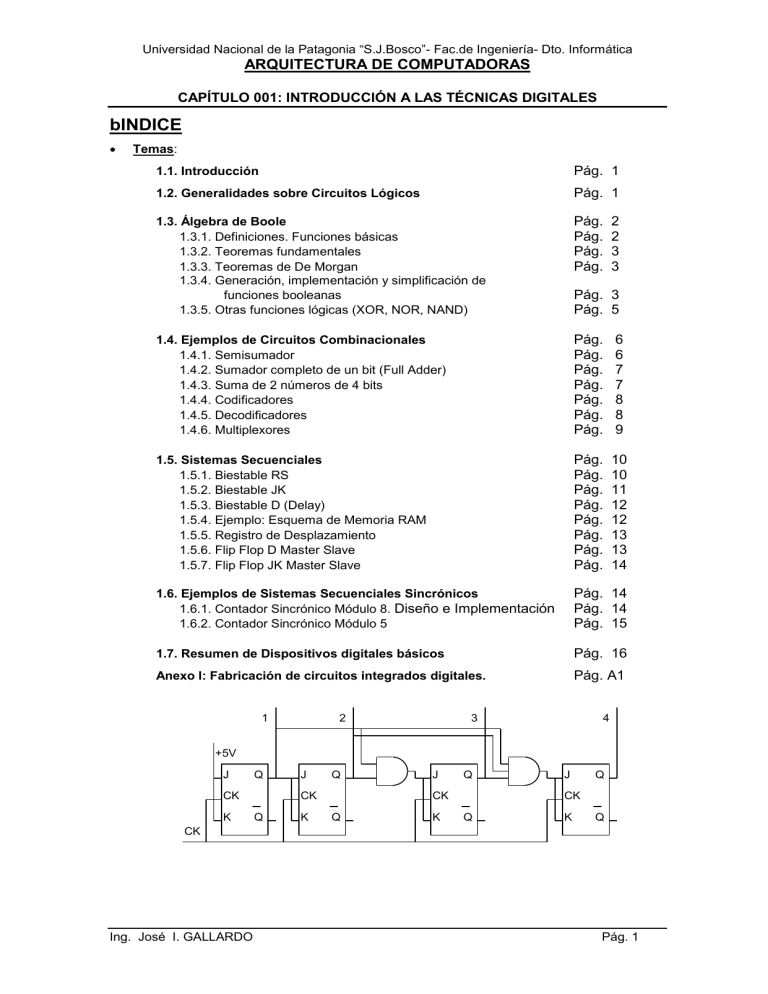

_

J0=Q2t, K0=1,

J1=K1= Q0t,

Q0

J

Q

Q1

J

Clk _

K

Q

J2=Q0t.Q1t, K2=1

K

Q

_

Q

Q2

J

K

Q

_

Q

---------------------------------Bibliografía:

1. Estructura y Funcionamiento de Computadores Digitales- Meinadier- Edit. AC- Cap.3.

2. Fundamentos de Computadores Digitales- Bartee- Edit. McGraw Hill- Cap.3 y 4.

3. Fundamentos de Microprocesadores- Tokheim- Serie Schaum- McGraw Hill- Cap.3.

---------------------------------FIN CAPITULO I

Ing. José I. GALLARDO

Pág. 16

Universidad Nacional de la Patagonia “S.J.Bosco”- Fac.de Ingeniería- Dto. Informática

ARQUITECTURA DE COMPUTADORAS

CAPÍTULO 001: INTRODUCCIÓN A LAS TÉCNICAS DIGITALES

RESUMEN DE DISPOSITIVOS DIGITALES BÁSICOS (Morris Mano)

a) Compuertas Lógicas

XNOR

Ing. José I. GALLARDO

Pág. 17

Universidad Nacional de la Patagonia “S.J.Bosco”- Fac.de Ingeniería- Dto. Informática

ARQUITECTURA DE COMPUTADORAS

CAPÍTULO 001: INTRODUCCIÓN A LAS TÉCNICAS DIGITALES

RESUMEN DE DISPOSITIVOS DIGITALES BÁSICOS

b) Biestables

Flip-Flop RS

Flip-Flop JK

(Toggle)

Ing. José I. GALLARDO

Pág. 18