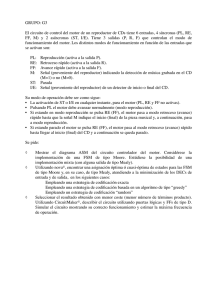

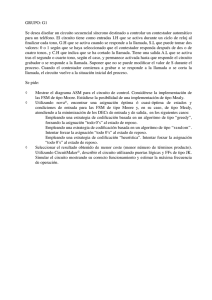

8.1 571 Estado siguiente Estado presente w=0 w=1 y2 y1 Y2 Y1 Y 2 Y1 00 10 11 0 01 01 00 0 10 11 00 0 11 10 01 1 Figura P8.1 8.3 PASOS BÁSICOSPROBLEMAS DE DISEÑO Salida z Tabla de asignación de estados para los problemas 8.1 y 8.2. Derive un diagrama de estado para una FSM que tiene una entrada w y una salida z. La máquina debe generar z ⫽ 1 cuando los valores previos de w fueron 1001 o 1111; de otro modo, z ⫽ 0. Se permite sobreponer patrones de entrada. Un ejemplo del comportamiento buscado es w : 010111100110011111 z : 000000100100010011 8.4 Escriba código de VHDL para la FSM descrita en el problema 8.3. *8.5 Elabore una tabla de estados mínimos para una FSM tipo Moore de entrada y salida únicas que genera una salida de 1 si en la secuencia de entrada detecta patrones 110 o 101. Deben detectarse secuencias sobrepuestas. *8.6 Repita el problema 8.5 para una FSM tipo Mealy. 8.7 Derive los circuitos que se aplican en las tablas de estado de las figuras 8.51 y 8.52. ¿Cuál es el efecto de la minimización de estados en el costo de la implementación? 8.8 Dibuje los circuitos que implementan las tablas de estado de las figuras 8.55 y 8.56. Compare los costos de los circuitos. 8.9 Un circuito secuencial tiene dos entradas, w1 y w2, y una salida, z. Su función es comparar las secuencias de entrada de las dos entradas. Si w1 ⫽ w2 en cualquiera de cuatro ciclos consecutivos de reloj, el circuito genera z ⫽ 1; de lo contrario z ⫽ 0. Por ejemplo w1 : 0110111000110 w2 : 1110101000111 z : 0000100001110 Derive un circuito posible. 8.10 Escriba código de VHDL para la FSM descrita en el problema 8.9. 572 CAPÍTULO 8 • CIRCUITOS SÍNCRONOS SECUENCIALES 8.11 Una FSM tiene una entrada, w, y una salida, z. En cuatro pulsos consecutivos de reloj se aplica una secuencia de cuatro valores de la señal w. Calcule la tabla de estado para la FSM que genera z ⫽ 1 cuando detecta que se han aplicado las secuencias w : 0010 o w : 1110; de lo contrario, z ⫽ 0. Después del cuarto pulso de reloj, la máquina debe entrar de nuevo en el estado reset y estar lista para la secuencia siguiente. Minimice el número de estados necesarios. *8.12 Construya una tabla de estados mínimos para una FSM que actúa como un generador de paridad de tres bits. Por cada tres bits que se observan en la entrada w durante tres ciclos consecutivos de reloj, la FSM genera el bit de paridad p ⫽ 1 si y sólo si el número de unos (1) en la secuencia de tres bits es impar. 8.13 Escriba código de VHDL para la FSM descrita en el problema 8.12. 8.14 Dibuje los diagramas de tiempo para los circuitos de las figuras 8.43 y 8.47, si se supone el mismo cambio en las señales a y b para ambos circuitos. Considere los retrasos de propagación. *8.15 Muestre una tabla de estado para la tabla de asignación de estados de la figura P8.1. Emplee A, B, C y D para las cuatro filas de la tabla. Elabore una nueva tabla de asignación de estados con codificación de 1 activo. Para A utilice el código y4 y3 y2 y1 ⫽ 0001. Para los estados B, C y D emplee los códigos 0010, 0100 y 1000, respectivamente. Sintetice un circuito con flip-flops D. 8.16 Muestre cómo puede modificarse el circuito del problema 8.15, de modo que el código y4 y3 y2 y1 ⫽ 0000 se emplee para el estado reset, A, y los códigos para los estados B, C y D se cambien como sea necesario. (Sugerencia: no es necesario volver a sintetizar el circuito.) *8.17 En la figura 8.59 suponga que las salidas no especificadas en los estados B y G son, respectivamente, 0 y 1. Construya la tabla de estados mínimos para esta FSM. 8.18 En la figura 8.59 suponga que las salidas no especificadas en los estados B y G son, respectivamente, 1 y 0. Construya la tabla de estados mínimos para esta FSM. 8.19 Dibuje los circuitos que implementan las FSM definidas en las figuras 8.57 y 8.58. ¿Puede concluir algo respecto a la complejidad de los circuitos que se aplican en los tipos de máquinas Moore y Mealy? 8.20 Diseñe un contador que cuente los pulsos de la línea w y despliegue el conteo en la secuencia 0, 2, 1, 3, 0, 2,... Utilice flip-flops D en el circuito. *8.21 Repita el problema 8.20 con flip-flops JK. *8.22 Repita el problema 8.20 con flip-flops T. 8.23 Diseñe un contador módulo 6 que cuente en la secuencia 0, 1, 2, 3, 4, 5, 0, 1,... El contador debe contar los pulsos del reloj si su entrada enable, w, es igual a 1. Utilice flip-flops D en el circuito. 8.24 Repita el problema 8.23 con flip-flops JK. 8.25 Repita el problema 8.23 con flip-flops T. 8.26 Diseñe un circuito de tres bits tipo contador controlado por la entrada w. Si w ⫽ 1, entonces el contador agrega 2 al contenido y lo envuelve si el conteo alcanza 8 o 9. Así, si el estado presente es 8 o 9, entonces el estado siguiente se convierte respectivamente en 0 o 1. Si w ⫽ 0, entonces el contador resta 1 del contenido y actúa como un contador descendente normal. Utilice flip-flops D en el circuito. 8.1 8.27 Repita el problema 8.26 con flip-flops JK. 8.28 Repita el problema 8.26 con flip-flops T. *8.29 PASOS BÁSICOSPROBLEMAS DE DISEÑO 573 Derive la tabla de estado para el circuito de la figura P8.2. ¿Qué secuencia de valores de entrada en el cable w se detecta con este circuito? w D Reloj Q z Q D Q Q Figura P8.2 Circuito para el problema 8.29. 8.30 Escriba código de VHDL para la FSM mostrada en la figura 8.57, con el estilo del código de la figura 8.29. 8.31 Repita el problema 8.30, con el estilo del código de la figura 8.33. 8.32 Escriba código de VHDL para la FSM que se muestra en la figura 8.58, con el estilo del código de la figura 8.29. 8.33 Repita el problema 8.32, con el estilo del código de la figura 8.33. 8.34 Escriba código de VHDL para la FSM mostrada en la figura P8.1. Utilice el método de asignación de estados mostrado en la figura 8.34. 8.35 Repita el problema 8.34 con el método de asignación de estados mostrado en la figura 8.35. 8.36 Represente la FSM de la figura 8.57 en forma de carta ASM. 8.37 Represente la FSM de la figura 8.58 en forma de carta ASM. 8.38 La FSM árbitro definida en la sección 8.8 (figura 8.72) puede hacer que el dispositivo 3 nunca reciba servicio si los dispositivos 1 y 2 se mantienen continuamente haciendo solicitudes, de modo que en el estado Idle siempre sucede que el dispositivo 1 o 2 tiene una solicitud en puerta. Modifique la FSM pro-