1

11

Conjunto de

instrucciones THUMB

5

Resumen de formato

5-2

Opcode Summary

5-3

5.1

Formato 1: mover el registro desplazado

5-5

5.2

Formato 2: añadir/restar

Formato 3: mover/comparar/añadir/restar

inmediatamente

5-7

5.3

5.4

5.5

5.6

5.7

5.8

5.9

5-9

Formato 4: Operaciones ALU

Formato 5: Operaciones de registro/intercambio de

sucursales

5-11

Formato 6: carga relativa del PC

Formato 7: carga/almacén con desplazamiento de

registro

Formato 8: cargar/almacenar el signo extendido

byte/halfword

Formato 9: carga/almacenamiento con desplazamiento

inmediato

5-16

5-13

5-18

5-20

5-22

5.10 Formato 10: medio término de carga/almacenamiento

5-24

5.11 Formato 11: carga relativa/almacén SP

5-26

5.12 Formato 12: dirección de carga

5-28

5.13 Formato 13: agregar desplazamiento al puntero de pila

5-30

5.14 Formato 14: registros push/pop

5-32

5.15 Formato 15: carga/almacenamiento múltiple

5-34

5.16 Formato 16: rama condicional

5-36

5.17 Formato 17: interrupción de software

5-38

5.18 Formato 18: rama incondicional

5-39

5.19 Formato 19: rama larga con enlace

5-40

5.20 Instruction Set Examples

5-42

Acceso

Abierto

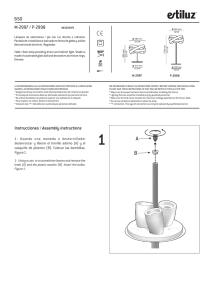

Este capítulo describe el conjunto de instrucciones THUMB.

Hoja de datos de ARM7TDMI

BRAZO DDI 0029E

5-1

Acceso

Abierto

Conjunto de instrucciones THUMB

Resumen de formato

Los formatos de conjunto de instrucciones THUMB se muestran en la siguiente figura.

15

14

13

1

0

0

0

2

0

0

0

3

0

0

1

4

0

1

0

0

0

0

5

0

1

0

0

0

1

6

0

1

0

0

1

7

0

1

0

1

L

B

0

Ro

Rb

Rd

8

0

1

0

1

H

S

1

Ro

Rb

Rd

9

0

1

1

B

L

Offset5

Rb

Rd

10

1

0

0

0

L

Offset5

Rb

Rd

11

1

0

0

1

L

Rd

Word8

12

1

0

1

0

SP

Rd

Word8

13

1

0

1

1

0

0

0

0

14

1

0

1

1

L

1

0

R

15

1

1

0

0

L

16

1

1

0

1

17

1

1

0

1

1

18

1

1

1

0

0

19

12

11

10

9

Op

1

8

7

6

5

Offset5

1

I

Op

1

1

1

H

15

14

13

12

11

2

1

0

Mover el registro

desplazado

Rd

Op Rn/offset3

Rs

Rd

Rd

Offset8

Sumar/restar

Mover/comparar/añad

ir

/restar inmediata

Rs

Rd

Rs/Hs

Rd/Hd

ALU operaciones

Hola operaciones de

registro

/bolsa de sucursales

Op

Op

H1 H2

Word8

S

Dirección de carga

Agregar desplazamiento al

puntero de pila

Rlist

Rb

1

Carga relativa de PC

Cargar/almacenar con

registro

compensar

Ampliado el signo de

carga/almacenamiento

byte/mediapalabra

Carga/almacenamiento

con inmediata

compensar

Medio término de

carga/almacenamient

o

Carga relativa

SP/almacén

SWord7

Registros push/pop

Carga/almacenamient

o múltiple

Rlist

Cond

1

3

Rs

Rd

1

4

1

Soffset8

Rama condicional

Value8

Software Interrupt

Offset11

Rama incondicional

Compens

ar

10

9

8

7

6

5

4

Rama larga con

enlace

3

2

1

0

Figura 5-1: Formatos de conjunto de instrucciones THUMB

5-2

Hoja de datos de ARM7TDMI

BRAZO DDI 0029E

Conjunto de instrucciones

THUMB

Opcode Summary

La siguiente tabla resume el conjunto de instrucciones THUMB. Para obtener

más información sobre una instrucción en particular, consulte las secciones

enumeradas en la columna de la derecha.

Nemotécnic

o

Instrucción

Lo register

Hi register

operando

operando

Véase la sección

Condición

siguiente:

conjunto de

códigos

Añadir con Llevar

5.4

SUMAR

Sumar

5.1.3, 5.5, 5.12, 5.13

Y

Y

5.4

ASR

Desplazamiento

aritmético a la derecha

5.1, 5.4

B

Rama incondicional

5.16

Bxx

Rama condicional

5.17

BIC

Poco claro

5.4

BL

Branch and Link

5.19

BX

Sucursal y Bolsa

5.5

CMN

Comparar Negativo

5.4

CMP

Comparar

5.3, 5.4, 5.5

EOR

EOR

5.4

LDMIA

Cargar múltiples

5.15

LDR

Palabra de carga

5.7, 5.6, 5.9, 5.11

LDRB

Byte de carga

5.7, 5.9

LDRH

Medio término de carga

5.8, 5.10

LSL

Desplazamiento lógico

a la izquierda

5.1, 5.4

LDSB

Señal de carga

extendida

byte

5.8

LDSH

Señal de carga

extendida

medio término

5.8

LSR

Desplazamiento lógico

a la derecha

5.1, 5.4

MOV

Registro de mudanzas

5.3, 5.5

MUL

Multiplicar

5.4

MVN

Mover registro negativo

5.4

Acceso

Abierto

ADC

Tabla 5-1: Opcodes del conjunto de instrucciones THUMB

Hoja de datos de ARM7TDMI

BRAZO DDI 0029E

5-3

Acceso

Abierto

Conjunto de instrucciones THUMB

Nemotécnic

o

Instrucción

Lo register

Hi register

operando

operando

Véase la sección

Condición

siguiente:

conjunto de

códigos

NEGATIVO

Negar

5.4

ORR

O

5.4

POP

Registros pop

5.14

EMPUJAR

Registros push

5.14

ROR

Girar a la derecha

5.4

SBC

Restar con Llevar

5.4

ESTEMIA

Almacenar múltiples

5.15

STR

Palabra de almacén

5.7, 5.9, 5.11

STRB

Almacenar byte

5.7

STRH

Término medio de

tienda

5.8, 5.10

SWI

Software Interrupt

5.17

SUBMARINO Restar

5.1.3, 5.3

TST

5.4

Trozos de prueba

Tabla 5-1: Opcodes del conjunto de instrucciones THUMB

(Continuación)

Los códigos de condición no se ven afectados por las

versiones de formato 5, 12 y 13 de esta instrucción.

Los códigos de condición no se ven afectados por la versión de

formato 5 de esta instrucción.

5-4

Hoja de datos de ARM7TDMI

BRAZO DDI 0029E

Conjunto de instrucciones

THUMB

5.1

Formato 1: mover el registro desplazado

15

14

13

0

0

0

12

11

Op

10

9

8

7

6

Offset5

5

4

3

2

Rs

1

0

Rd

Registro de destino

Registro de fuentes

Valor inmediato

Opcode

Acceso

Abierto

0- LSL

1- LSR

2- ASR

Figura 5-2: Formato 1

5.1.1 Operación

Estas instrucciones mueven un valor desplazado entre los registros Lo. La sintaxis

del ensamblador THUMB se muestra en la Tabla 5-2: Resumen de las

instrucciones del formato 1.

Nota

Todas las instrucciones de este grupo establecen los códigos de condición CPSR.

OP

ENSAMBLADOR DE

PULGARES

EQUIVALENTE DE ARMAS

Acción

00

LSL Rd, Rs, #Offset5

MOVS Rd, Rs, LSL #Offset5

Mayús Rs por un valor inmediato de 5

bits

y almacenar el resultado en Rd.

01

LSR Rd, Rs, #Offset5

MOVS Rd, Rs, LSR #Offset5

10

ASR Rd, Rs, #Offset5

MOVS Rd, Rs, ASR #Offset5

Realizar desplazamiento lógico a la

derecha en Rs por un 5bit valor inmediato y almacenar el

resultado

en Rd.

Realizar desplazamiento aritmético a la

derecha en Rs por un

5-bit valor inmediato y almacenar el

dar lugar a Rd.

Cuadro 5-2: Resumen de las instrucciones del formato 1

Hoja de datos de ARM7TDMI

BRAZO DDI 0029E

5-5

Acceso

Abierto

Conjunto de instrucciones THUMB

5.1.2 Tiempos de ciclo de instrucción

Todas las instrucciones en este formato tienen una instrucción ARM equivalente

como se muestra en la Tabla 5-2: Resumen de las instrucciones de formato 1 en la

página 5-5. Los tiempos de ciclo de instrucción para la instrucción THUMB son

idénticos a los de la instrucción ARM equivalente. Para obtener más información

sobre los tiempos de los ciclos de instrucción, consulte el Capítulo 10, Operaciones

del ciclo de instrucción.

5.1.3 Ejemplos

LSR

R2, R5, #27

contenidos

; Desplazamiento lógico a la derecha de los

; de R5 por 27 y almacenar el resultado en

R2.

; Establezca los códigos de condición en el

resultado.

5-6

Hoja de datos de ARM7TDMI

BRAZO DDI 0029E

Conjunto de instrucciones

THUMB

5.2 Formato 2: añadir/restar

15

14

13

12

11

10

0

0

0

1

1

I

9

Op

8

7

6

5

Rn/Offset3

4

3

2

Rs

1

0

Rd

Registro de destino

Registro de fuentes

Registro/

Valor inmediato

Opcode

0-ADD

1-SUB

Bandera inmediata

0 - Operando de registro

1 - Operando inmediato

Figura 5-3: Formato

2

5.2.1 Operación

Estas instrucciones permiten que el contenido de un registro Lo o un valor

inmediato de 3 bits se añada o reste de un registro Lo. La sintaxis del ensamblador

THUMB se muestra en la Tabla 5-3: Resumen de las instrucciones del formato 2.

Nota

Todas las instrucciones de este grupo establecen los códigos de condición CPSR.

Op

I

ENSAMBLADOR DE

PULGARES

EQUIVALENTE DE

ARMAS

Acción

0

0

ADD Rd, Rs, Rn

ADD Rd, Rs, Rn

Añadir contenido de Rn al contenido de Rs.

Lugar

dar lugar a Rd.

0

1

Agregar Rd, Rs,

#Offset3

Rd añade, Rs, #Offset3

Añadir un valor inmediato de 3 bits al

contenido de

Rs. Lugar resultado en Rd.

1

0

SUB Rd, Rs, Rn

Sub Rd, Rs, Rn

Restar el contenido de Rn del contenido de

Rs. Lugar resultado en Rd.

1

1

SUB Rd, Rs, #Offset3

Rd SUBS, Rs, Offset3

Restar el valor inmediato de 3 bits de

contenido de Rs. Lugar resultado en Rd.

Acceso

Abierto

Hoja de datos de ARM7TDMI

BRAZO DDI 0029E

5-7

Acceso

Abierto

Conjunto de instrucciones THUMB

5.2.2 Tiempos de ciclo de instrucción

Todas las instrucciones en este formato tienen una instrucción ARM equivalente

como se muestra en el cuadro 5-3: Resumen de las instrucciones de formato 2 en

la página 5-7. Los tiempos de ciclo de instrucción para la instrucción THUMB son

idénticos a los de la instrucción ARM equivalente. Para obtener más información

sobre los tiempos de los ciclos de instrucción, consulte el Capítulo 10, Operaciones

del ciclo de instrucción.

5.2.3 Ejemplos

SUMA

R

R0, R3, R4

SUBM

ARIN

O

R6, R2, #6

; R0 := R3 + R4 y establecer los códigos

de condición en

; el resultado.

R6 := R2 - 6 y establece los códigos de

; condición.

5-8

Hoja de datos de ARM7TDMI

BRAZO DDI 0029E

Conjunto de instrucciones

THUMB

5.3

Formato 3: mover/comparar/añadir/restar inmediatamente

15

14

13

0

0

1

12

11

Op

10

9

8

7

6

5

4

Rd

3

2

1

0

Offset8

Valor inmediato

Registro de origen/destino

Opcode

0- MOV

1- CMP

2- AÑADIR

3 SUBMARINO

Figura 5-4: Formato 3

Las instrucciones de este grupo realizan operaciones entre un registro Lo y un

valor inmediato de 8 bits.

La sintaxis del ensamblador THUMB se muestra en la Tabla 5-4: Resumen

de las instrucciones del formato 3.

Nota

Acceso

Abierto

5.3.1 Operaciones

Todas las instrucciones de este grupo establecen los códigos de condición CPSR.

Op

ENSAMBLADOR DE

PULGARES

EQUIVALENTE DE

ARMAS

Acción

00

Descargar MOV Rd,

#Offset8

MOVS Rd, #Offset8

Mueva el valor inmediato de 8 bits a Rd.

01

CMP Rd, #Offset8

CMP Rd, #Offset8

Compare el contenido de Rd con 8 bits

valor inmediato.

10

Rd ADD, #Offset8

Rd, Rd, #Offset8

11

SUB Rd, #Offset8

Rd, Rd, #Offset8

Agregar valor inmediato de 8 bits al

contenido de Rd

y colocar el resultado en Rd.

Restar el valor inmediato de 8 bits de

contenido de Rd y colocar el resultado en

Rd.

Cuadro 5-4: Resumen de las instrucciones del formato 3

Hoja de datos de ARM7TDMI

BRAZO DDI 0029E

5-9

Acceso

Abierto

Conjunto de instrucciones THUMB

5.3.2 Tiempos de ciclo de instrucción

Todas las instrucciones en este formato tienen una instrucción ARM equivalente

como se muestra en el cuadro 5-4: Resumen de las instrucciones de formato 3 en

la página 5-9. Los tiempos de ciclo de instrucción para la instrucción THUMB son

idénticos a los de la instrucción ARM equivalente. Para obtener más información

sobre los tiempos de los ciclos de instrucción, consulte el Capítulo 10, Operaciones

del ciclo de instrucción.

5.3.3 Ejemplos

MOV

R0, #128

CMP

R2, #62

SUMA

R

R1, #255

SUBM

ARIN

O

R6, #145

128 y establecer los

; R0 := códigos de condición

; Establecer los códigos

de condición en

R2-62

y

estable

; R1 := R1 + 255 cer

condición

;

códigos

y

estable

; R6 := R6 - 145 cer

condición

;

códigos

5-10

Hoja de datos de ARM7TDMI

BRAZO DDI 0029E

Conjunto de instrucciones

THUMB

5.4

Formato 4: Operaciones ALU

15

14

13

12

11

10

0

1

0

0

0

0

9

8

7

6

Op

5

4

3

2

Rs

1

0

Rd

Origen/destino

registro

Registro de fuentes 2

Opcode

Figura 5-5: Formato 4

5.4.1 Operación

Nota

Acceso

Abierto

Las siguientes instrucciones realizan operaciones ALU en un par de registros Lo.

Todas las instrucciones de este grupo establecen los códigos de condición CPSR.

OP

ENSAMBLADOR DE

PULGARES

EQUIVALENTE DE ARMAS

Acción

0000

Y Rd, Rs

Rd, Rd, Rs

Rd:= Rd y Rs

0001

EOR Rd, Rs

EORS Rd, Rd, Rs

Rd:= Rd EOR Rs

0010

LSL Rd, Rs

MOVS Rd, Rd, LSL Rs

Rd := Rd << Rs

0011

LSR Rd, Rs

MOVS Rd, Rd, LSR Rs

Rd := Rd >> Rs

0100

ASR Rd, Rs

MOVS Rd, Rd, ASR Rs

Rd := Rd ASR Rs

0101

ADC Rd, Rs

ADCS Rd, Rd, Rs

Rd := Rd + Rs + C-bit

0110

SBC Rd, Rs

SBCS Rd, Rd, Rs

Rd := Rd - Rs - NO C-bit

0111

ROR Rd, Rs

MOVS Rd, Rd, ROR Rs

Rd := Rd ROR Rs

1000

TST Rd, Rs

TST Rd, Rs

Establezca los códigos de condición en

Rd AND Rs

1001

NEG Rd, Rs

Rd RSBS, Rs, #0

Rd = -Rs

Cuadro 5-5: Resumen de las instrucciones del formato 4

Hoja de datos de ARM7TDMI

5-11

BRAZO DDI 0029E

Acceso

Abierto

Conjunto de instrucciones THUMB

OP

ENSAMBLADOR DE

PULGARES

EQUIVALENTE DE ARMAS

Acción

1010

CMP Rd, Rs

CMP Rd, Rs

Establecer códigos de condición en Rd Rs

1011

CMN Rd, Rs

CMN Rd, Rs

Establecer códigos de condición en Rd +

Rs

1100

ORR Rd, Rs

ORRS Rd, Rd, Rs

Rd := Rd o Rs

1101

MUL Rd, Rs

MULS Rd, Rs, Rd

Rd := Rs * Rd

1110

BIC Rd, Rs

BICS Rd, Rd, Rs

Rd := Rd Y NO Rs

1111

MVN Rd, Rs

MVNS Rd, Rs

Rd := NO Rs

Cuadro 5-5: Resumen de las instrucciones del formato 4

(continuación)

5.4.2 Tiempos de ciclo de instrucción

Todas las instrucciones en este formato tienen una instrucción ARM equivalente

como se muestra en el cuadro 5-5: Resumen de las instrucciones del formato 4 en

la página 5-11. Los tiempos de ciclo de instrucción para la instrucción THUMB son

idénticos a los de la instrucción ARM equivalente. Para obtener más información

sobre los tiempos de los ciclos de instrucción, consulte el Capítulo 10, Operaciones

del ciclo de instrucción.

5.4.3 Ejemplos

EOR

R3, R4

ROR

R1,

R0

NEGA

TIVO

R5,

R3

CMP

R2, R6

MUL

R0, R7

y establecer los códigos

;R3:=R3

EOR R4 de condición

; Girar a la

por el valor en R0,

derecha R1 almacenar

el resultado en R1 y

códigos de

; conjunto

condición

contenido

R3 a partir de

; Restar

el de

cero,

; almacenar el resultado en R5. Establecer

códigos de condición

; es decir R5 = -R3

;

Establece

códigos sobre el

r la

condición resultado

; R2 - R6

establecer códigos

; R0 := R7 * R0 y

de condición

de

5-12

Hoja de datos de ARM7TDMI

BRAZO DDI 0029E

Conjunto de instrucciones

THUMB

5.5

Formato 5: Operaciones de registro/intercambio de sucursales

15

14

13

12

11

10

0

1

0

0

0

1

9

8

Op

7

H1

6

H2

5

4

Rs/Hs

3

2

1

0

Rd/Hd

Registro de destino

Registro de fuentes

Hi operand bandera

2

Hi operand bandera

1

Opcode

5.5.1 Operación

Hay cuatro conjuntos de instrucciones en este grupo. Las tres primeras permiten

realizar operaciones ADD, CMP y MOV entre registros Lo y Hi, o un par de

registros Hi. El cuarto, BX, permite realizar una rama que también puede usarse

para cambiar el estado del procesador.

Acceso

Abierto

Figura 5-6: Formato 5

La sintaxis del ensamblador THUMB se muestra en la tabla 5-6: Resumen

de las instrucciones de formato 5

En este grupo solo CMP (Op = 01) establece los códigos de condición CPSR.

Nota

La acción de H1= 0, H2 = 0 para Op = 00 (ADD), Op = 01 (CMP) y Op = 10 (MOV)

no está definida y no debe usarse.

Op

H1

H2

ENSAMBLADOR DE

PULGARES

EQUIVALENTE DE

ARMAS

00

0

1

ADD Rd, Hs

ADD Rd, Rd, Hs

Añadir un registro en el rango 8-15 a un

Registro en el rango 0-7.

00

1

0

ADD Hd, Rs

Agregar Hd, Hd, Rs

Añadir un registro en el rango 0-7 a un

Registro en el rango 8-15.

00

1

1

ADD Hd, Hs

Agregar Hd, Hd, Hs

Añadir dos registros en el rango 8-15

Acción

Cuadro 5-6: Resumen de las instrucciones del formato 5

Hoja de datos de ARM7TDMI

BRAZO DDI 0029E

5-13

Acceso

Abierto

Conjunto de instrucciones THUMB

Op

H1

H2

ENSAMBLADOR DE

PULGARES

EQUIVALENTE DE

ARMAS

01

0

1

CMP Rd, Hs

CMP Rd, Hs

Comparar un registro en el rango 0-7

con un registro en el rango 8-15. Set

las banderas de código de condición en

el resultado.

01

1

0

CMP Hd, Rs

CMP Hd, Rs

Comparar un registro en el rango 8-15

con un registro en el rango 0-7.

Establecer el

Las banderas de código de condición en

el resultado.

01

1

1

CMP Hd, Hs

CMP Hd, Hs

Comparar dos registros en el rango 815. Establezca las banderas de código

de condición en el

resultado.

10

0

1

MOV Rd, Hs

MOV Rd, Hs

Mover un valor desde un registro en el

rango 8-15 a un registro en el rango 07.

10

1

0

MOV Hd, Rs

MOV Hd, Rs

Mover un valor desde un registro en el

rango 0-7 a un registro en el rango 8

15.

10

1

1

MOV Hd, Hs

MOV Hd, Hs

Mover un valor entre dos registros en

el rango 8-15.

11

0

0

BX Rs

BX Rs

Realizar rama (más estado opcional

cambio) a la dirección en un registro en

el

rango 0-7.

11

0

1

BX Hs

BX Hs

Realizar rama (más estado opcional

cambio) a la dirección en un registro en

el

rango 8-15.

Acción

Cuadro 5-6: Resumen de las instrucciones del formato 5

(continuación)

5.5.2 Tiempos de ciclo de instrucción

Todas las instrucciones en este formato tienen una instrucción ARM equivalente

como se muestra en la Tabla 5-6: Resumen de las instrucciones de formato 5 en la

página 5-13. Los tiempos de ciclo de instrucción para la instrucción THUMB son

idénticos a los de la instrucción ARM equivalente. Para obtener más información

sobre los tiempos de los ciclos de instrucción, consulte el Capítulo 10, Operaciones

del ciclo de instrucción.

5.5.3 La instrucción BX

BX realiza una rama a una rutina cuya dirección de inicio se especifica en un

registro Lo o Hi.

El bit 0 de la dirección determina el estado del procesador en la entrada a la rutina:

Bit 0 = 0

hace que el procesador entre en estado ARM.

Bit 0 = 1

hace que el procesador entre en estado THUMB.

N

o

t

a

5-14

La acción de H1 = 1 para esta instrucción es indefinida y no debe usarse.

Hoja de datos de ARM7TDMI

BRAZO DDI 0029E

Conjunto de instrucciones

THUMB

5.5.4 Ejemplos

Hola operaciones de registro

SUMAR

PC, R5

CMP

R4, R12

MOV

R15, R14

; PC := PC + R5 pero no establezca

el

; códigos de condición.

; Establecer los códigos de

condición en el

; resultado de R4 - R12.

; Mover R14 (LR) a R15 (PC)

; pero no establezca los códigos de

condición,

; por ejemplo. retorno de

subrutina.

Sucursal y bolsa

; Cambie de estado PULGAR a BRAZO.

MOV

BX

R1, fuera del THUMB

; Dirección de carga de outofTHUMB

; en R1.

R11,R1

R11

; Transferir el contenido de R11 a

; el PC.

; Bit 0 de R11 determina si

; Se introduce el estado ARM o

THUMB, es decir.

; Estado ARM aquí.

Acceso

Abierto

ADR

...

ALINEAR

CODE32

Fuera de la

THUMB

; Ahora procesando las instrucciones

ARM...

5.5.5 Uso de R15 como operando

Si R15 se usa como operando, el valor será la dirección de la instrucción + 4 con el

bit 0 borrado. Ejecutar un PC BX en estado THUMB desde una dirección no

alineada con palabras dará como resultado una ejecución impredecible.

Hoja de datos de ARM7TDMI

BRAZO DDI 0029E

5-15

Conjunto de instrucciones THUMB

5.6

Formato 6: carga relativa del PC

15

14

13

12

11

0

1

0

0

1

10

9

8

7

6

Rd

5

4

3

2

1

0

Word8

Valor inmediato

Registro de destino

Figura 5-7: Formato 6

5.6.1 Operación

Esta instrucción carga una palabra de una dirección especificada como un

desplazamiento inmediato de 10 bits desde el PC.

Acceso

Abierto

La sintaxis del ensamblador THUMB se muestra a continuación.

ENSAMBLADOR DE

PULGARES

EQUIVALENTE DE

ARMAS

LDR Rd, [PC, #Imm]

LDR Rd, [R15, #Imm]

Acción

Añadir desplazamiento sin firmar

(255 palabras,

1020 bytes) en Imm a la corriente

valor del PC. Cargar la palabra

de la dirección resultante en Rd.

Tabla 5-7: Resumen de la instrucción de carga relativa a PC

Nota

El valor especificado por #Imm es una dirección completa de 10 bits, pero siempre debe

estar alineado con palabras (es decir, con bits 1:0 establecidos en 0), ya que el

ensamblador coloca #Imm >> 2 en el campo Word8.

Note

The value of the PC will be 4 bytes greater than the address of this instruction, but

bit 1 of the PC is forced to 0 to ensure it is word aligned.

5-16

ARM7TDMI Data Sheet

ARM DDI 0029E

THUMB Instruction Set

5.6.2 Instruction cycle times

All instructions in this format have an equivalent ARM instruction as shown in Table

5-7: Summary of PC-relative load instruction on page 5-16. The instruction cycle

times for the THUMB instruction are identical to that of the equivalent ARM

instruction. For more information on instruction cycle times, please refer to Chapter

10, Instruction Cycle Operations.

5.6.3 Examples

LDR R3,[PC,#844]

; Load into R3 the word found at the

address formed by adding 844 to PC.

bit[1] of PC is forced to zero.

Note that the THUMB opcode will contain

211 as the Word8 value.

Open Access

;

;

;

;

ARM7TDMI Data Sheet

ARM DDI 0029E

5-17

THUMB Instruction Set

5.7

Format 7: load/store with register offset

15

14

13

12

11

10

9

0

1

0

1

L

B

0

8

7

6

Ro

5

4

Rb

3

2

1

0

Rd

Source/destination

register

Base register

Offset register

Open Access

Byte/Word flag

0 - Transfer word quantity

1 - Transfer byte quantity

Load/Store flag

0 - Store to memory

1 - Load from memory

Figure 5-8: Format 7

5.7.1 Operation

These instructions transfer byte or word values between registers and memory.

Memory addresses are pre-indexed using an offset register in the range 0-7.

The THUMB assembler syntax is shown in Table 5-8: Summary of format 7

instructions.

L

B

THUMB assembler

ARM equivalent

Action

0

0

STR Rd, [Rb, Ro]

STR Rd, [Rb, Ro]

Pre-indexed word store:

Calculate the target address by

adding together the value in Rb

and the value in Ro. Store the

contents of Rd at the address.

Table 5-8: Summary of format 7 instructions

5-18

ARM7TDMI Data Sheet

ARM DDI 0029E

THUMB Instruction Set

L

B

THUMB assembler

ARM equivalent

Action

0

1

STRB Rd, [Rb, Ro]

STRB Rd, [Rb, Ro]

Pre-indexed byte store:

Calculate the target address by

adding together the value in Rb

and the value in Ro. Store the byte

value in Rd at the resulting

address.

1

0

LDR Rd, [Rb, Ro]

LDR Rd, [Rb, Ro]

Pre-indexed word load:

Calculate the source address by

adding together the value in Rb

and the value in Ro. Load the

contents of the address into Rd.

1

1

LDRB Rd, [Rb, Ro]

LDRB Rd, [Rb, Ro]

Pre-indexed byte load:

Calculate the source address by

adding together the value in Rb

and the value in Ro. Load the byte

value at the resulting address.

5.7.2 Instruction cycle times

All instructions in this format have an equivalent ARM instruction as shown in Table

5-8: Summary of format 7 instructions on page 5-18. The instruction cycle times for

the THUMB instruction are identical to that of the equivalent ARM instruction. For

more information on instruction cycle times, please refer to Chapter 10, Instruction

Cycle Operations.

5.7.3 Examples

STR

R3, [R2,R6]

LDRB

R2, [R0,R7]

; Store word in R3 at the address

; formed by adding R6 to R2.

; Load into R2 the byte found at

; the address formed by adding

; R7 to R0.

ARM7TDMI Data Sheet

ARM DDI 0029E

5-19

Open Access

Table 5-8: Summary of format 7 instructions (Continued)

THUMB Instruction Set

5.8

Format 8: load/store sign-extended byte/halfword

15

14

13

12

11

10

9

0

1

0

1

H

S

1

8

7

6

5

Ro

4

3

2

Rb

1

0

Rd

Destination register

Base register

Offset register

Open Access

Sign-extended flag

0 - Operand not sign-extended

1 - Operand sign-extended

H flag

Figure 5-9: Format 8

5.8.1 Operation

These instructions load optionally sign-extended bytes or halfwords, and store

halfwords. The THUMB assembler syntax is shown below.

S

H

THUMB assembler

ARM equivalent

Action

0

0

STRH Rd, [Rb, Ro]

STRH Rd, [Rb, Ro]

Store halfword:

Add Ro to base address in Rb. Store bits 015 of Rd at the resulting address.

0

1

LDRH Rd, [Rb, Ro]

LDRH Rd, [Rb, Ro]

Load halfword:

Add Ro to base address in Rb. Load bits 015 of Rd from the resulting address, and set

bits 16-31 of Rd to 0.

1

0

LDSB Rd, [Rb, Ro]

LDRSB Rd, [Rb, Ro]

Load sign-extended byte:

Add Ro to base address in Rb. Load bits 07 of Rd from the resulting address, and set

bits 8-31 of Rd to bit 7.

Table 5-9: Summary of format 8 instructions

5-20

ARM7TDMI Data Sheet

ARM DDI 0029E

THUMB Instruction Set

S

H

THUMB assembler

ARM equivalent

Action

1

1

LDSH Rd, [Rb, Ro]

LDRSH Rd, [Rb, Ro]

Load sign-extended halfword:

Add Ro to base address in Rb. Load bits 015 of Rd from the resulting address, and set

bits 16-31 of Rd to bit 15.

Table 5-9: Summary of format 8 instructions (Continued)

5.8.2 Instruction cycle times

All instructions in this format have an equivalent ARM instruction as shown in Table

5-9: Summary of format 8 instructions on page 5-20. The instruction cycle times for

the THUMB instruction are identical to that of the equivalent ARM instruction. For

more information on instruction cycle times, please refer to Chapter 10, Instruction

Cycle Operations.

5.8.3 Examples

R4, [R3, R0]; Store the lower 16 bits of R4 at the ;

address formed by adding R0 to R3.

LDSB

R2, [R7, R1]

; Load into R2 the sign extended byte

; found at the address formed by adding

; R1 to R7.

LDSH

R3, [R4, R2]

; Load into R3 the sign extended halfword

; found at the address formed by adding

; R2 to R4.

ARM7TDMI Data Sheet

ARM DDI 0029E

5-21

Open Access

STRH

THUMB Instruction Set

5.9

Format 9: load/store with immediate offset

15

14

13

12

11

0

1

1

B

L

10

9

8

7

6

Offset5

5

4

Rb

3

2

1

0

Rd

Source/destination

register

Base register

Offset value

Open Access

Load/Store flag

0 - Store to memory

1 - Load from memory

Byte/Word flag

0 - Transfer word quantity

1 - Transfer byte quantity

Figure 5-10: Format 9

5.9.1 Operation

These instructions transfer byte or word values between registers and memory

using an immediate 5 or 7-bit offset.

The THUMB assembler syntax is shown in Table 5-10: Summary of format 9

instructions.

L

B

THUMB assembler

ARM equivalent

Action

0

0

STR Rd, [Rb, #Imm]

STR Rd, [Rb, #Imm]

Calculate the target address by

adding together the value in Rb

and Imm. Store the contents of Rd

at the address.

1

0

LDR Rd, [Rb, #Imm]

LDR Rd, [Rb, #Imm]

Calculate the source address by

adding together the value in Rb

and Imm. Load Rd from the

address.

Table 5-10: Summary of format 9 instructions

5-22

ARM7TDMI Data Sheet

ARM DDI 0029E

THUMB Instruction Set

L

B

THUMB assembler

ARM equivalent

Action

0

1

STRB Rd, [Rb, #Imm]

STRB Rd, [Rb, #Imm]

Calculate the target address by

adding together the value in Rb

and Imm. Store the byte value in

Rd at the address.

1

1

LDRB Rd, [Rb, #Imm]

LDRB Rd, [Rb, #Imm]

Calculate source address by

adding together the value in Rb

and Imm. Load the byte value at

the address into Rd.

Table 5-10: Summary of format 9 instructions (Continued)

Note

For word accesses (B = 0), the value specified by #Imm is a full 7-bit address, but

must be word-aligned (ie with bits 1:0 set to 0), since the assembler places #Imm

>> 2 in the Offset5 field.

All instructions in this format have an equivalent ARM instruction as shown in Table

5-10: Summary of format 9 instructions on page 5-22. The instruction cycle times for

the THUMB instruction are identical to that of the equivalent ARM instruction. For

more information on instruction cycle times, please refer to Chapter 10, Instruction

Cycle Operations.

5.9.3 Examples

LDR

R2, [R5,#116]

; Load into R2 the word found at the

; address formed by adding 116 to R5.

; Note that the THUMB opcode will

; contain 29 as the Offset5 value.

STRB

R1, [R0,#13]

; Store the lower 8 bits of R1 at the

; address formed by adding 13 to R0.

; Note that the THUMB opcode will

; contain 13 as the Offset5 value.

ARM7TDMI Data Sheet

ARM DDI 0029E

5-23

Open Access

5.9.2 Instruction cycle times

THUMB Instruction Set

5.10 Format 10: load/store halfword

15

14

13

12

11

1

0

0

0

L

10

9

8

7

6

5

Offset5

4

Rb

3

2

1

0

Rd

Source/destination

register

Base register

Immediate value

Open Access

Load/Store bit

0 - Store to memory

1 - Load from memory

Figure 5-11: Format 10

5.10.1 Operation

These instructions transfer halfword values between a Lo register and memory.

Addresses are pre-indexed, using a 6-bit immediate value.

The THUMB assembler syntax is shown in Table 5-11: Halfword data transfer

instructions.

L

THUMB assembler

ARM equivalent

Action

0

STRH Rd, [Rb, #Imm]

STRH Rd, [Rb, #Imm]

Add #Imm to base address in Rb and store

bits 0-15 of Rd at the resulting address.

1

LDRH Rd, [Rb, #Imm]

LDRH Rd, [Rb, #Imm]

Add #Imm to base address in Rb. Load bits

0-15 from the resulting address into Rd and

set bits 16-31 to zero.

Table 5-11: Halfword data transfer instructions

Note

5-24

#Imm is a full 6-bit address but must be halfword-aligned (ie with bit 0 set to 0) since

the assembler places #Imm >> 1 in the Offset5 field.

ARM7TDMI Data Sheet

ARM DDI 0029E

THUMB Instruction Set

5.10.2 Instruction cycle times

All instructions in this format have an equivalent ARM instruction as shown in Table

5-11: Halfword data transfer instructions on page 5-24. The instruction cycle times

for the THUMB instruction are identical to that of the equivalent ARM instruction.

For more information on instruction cycle times, please refer to Chapter 10,

Instruction Cycle Operations.

5.10.3 Examples

STRH

R6, [R1, #56]

; Store the lower 16 bits of R4 at

;

;

;

;

LDRH

R4, [R7, #4]

the address formed by adding 56

R1.

Note that the THUMB opcode will

contain 28 as the Offset5 value.

; Load into R4 the halfword found at

Open Access

; the address formed by adding 4 to R7.

; Note that the THUMB opcode will contain

; 2 as the Offset5 value.

ARM7TDMI Data Sheet

ARM DDI 0029E

5-25

THUMB Instruction Set

5.11 Format 11: SP-relative load/store

15

14

13

12

11

1

0

0

1

L

10

9

8

7

6

5

Rd

4

3

2

1

0

Word8

Immediate value

Destination register

Load/Store bit

Open Access

0 - Store to memory

1 - Load from memory

Figure 5-12: Format 11

5.11.1 Operation

The instructions in this group perform an SP-relative load or store.The

THUMB assembler syntax is shown in the following table.

L

THUMB assembler

ARM equivalent

Action

0

STR Rd, [SP, #Imm]

STR Rd, [R13 #Imm]

Add unsigned offset (255 words, 1020

bytes) in Imm to the current value of the SP

(R7). Store the contents of Rd at the

resulting address.

1

LDR Rd, [SP, #Imm]

LDR Rd, [R13 #Imm]

Add unsigned offset (255 words, 1020

bytes) in Imm to the current value of the SP

(R7). Load the word from the resulting

address into Rd.

Table 5-12: SP-relative load/store instructions

Note

5-26

The offset supplied in #Imm is a full 10-bit address, but must always be word-aligned (ie

bits 1:0 set to 0), since the assembler places #Imm >> 2 in the Word8 field.

ARM7TDMI Data Sheet

ARM DDI 0029E

THUMB Instruction Set

5.11.2 Instruction cycle times

All instructions in this format have an equivalent ARM instruction as shown in Table

5-12: SP-relative load/store instructions on page 5-26. The instruction cycle times

for the THUMB instruction are identical to that of the equivalent ARM instruction.

For more information on instruction cycle times, please refer to Chapter 10,

Instruction Cycle Operations.

5.11.3 Examples

STR

R4, [SP,#492]

; Store the contents of R4 at the address

Open Access

; formed by adding 492 to SP (R13).

; Note that the THUMB opcode will contain

; 123 as the Word8 value.

ARM7TDMI Data Sheet

ARM DDI 0029E

5-27

THUMB Instruction Set

5.12 Format 12: load address

15

14

13

12

11

1

0

1

0 SP

10

9

8

7

6

Rd

5

4

3

2

1

0

Word8

8-bit unsigned constant

Destination register

Source

0-PC

1-SP

Figure 5-13: Format 12

5.12.1 Operation

Open Access

These instructions calculate an address by adding an 10-bit constant to either the

PC or the SP, and load the resulting address into a register.

The THUMB assembler syntax is shown in the following table.

SP

THUMB assembler

ARM equivalent

Action

0

ADD Rd, PC, #Imm

ADD Rd, R15, #Imm

Add #Imm to the current value of

the program counter (PC) and load

the result into Rd.

1

ADD Rd, SP, #Imm

ADD Rd, R13, #Imm

Add #Imm to the current value of

the stack pointer (SP) and load the

result into Rd.

Table 5-13: Load address

Note

The value specified by #Imm is a full 10-bit value, but this must be word-aligned (ie

with bits 1:0 set to 0) since the assembler places #Imm >> 2 in field Word8.

Where the PC is used as the source register (SP = 0), bit 1 of the PC is always

read as 0. The value of the PC will be 4 bytes greater than the address of the

instruction before bit 1 is forced to 0.

The CPSR condition codes are unaffected by these instructions.

5-28

ARM7TDMI Data Sheet

ARM DDI 0029E

THUMB Instruction Set

5.12.2 Instruction cycle times

All instructions in this format have an equivalent ARM instruction as shown in Table 5-13:

Load address on page 5-28. The instruction cycle times for the THUMB instruction are

identical to that of the equivalent ARM instruction. For more information on instruction

cycle times, please refer to Chapter 10, Instruction Cycle Operations.

5.12.3 Examples

ADD

R2, PC, #572

; R2 := PC + 572, but don't set the

;

;

;

;

ADD

R6, SP, #212

condition codes. bit[1] of PC is

forced to zero.

Note that the THUMB opcode will

contain 143 as the Word8 value.

; R6 := SP (R13) + 212, but don't

Open Access

; set the condition codes.

; Note that the THUMB opcode will

; contain 53 as the Word8 value.

ARM7TDMI Data Sheet

ARM DDI 0029E

5-29

THUMB Instruction Set

5.13 Format 13: add offset to Stack Pointer

15

14

1

13

0

1

12

1

11

10

0

0

9

0

8

0

7

6

5

S

4

3

2

1

0

SWord7

7-bit immediate value

Sign flag

0 -Offset is positive

1 -Offset is negative

Figure 5-14: Format 13

5.13.1 Operation

Open Access

This instruction adds a 9-bit signed constant to the stack pointer. The following

table shows the THUMB assembler syntax.

S

THUMB assembler

ARM equivalent

Action

0

ADD SP, #Imm

ADD R13, R13, #Imm

Add #Imm to the stack pointer (SP).

1

ADD SP, #-Imm

SUB R13, R13, #Imm

Add #-Imm to the stack pointer (SP).

Table 5-14: The ADD SP instruction

Note

The offset specified by #Imm can be up to -/+ 508, but must be word-aligned (ie with

bits 1:0 set to 0) since the assembler converts #Imm to an 8-bit sign + magnitude

number before placing it in field SWord7.

Note

The condition codes are not set by this instruction.

5.13.2 Instruction cycle times

All instructions in this format have an equivalent ARM instruction as shown in Table

5-14: The ADD SP instruction on page 5-30. The instruction cycle times for the

THUMB instruction are identical to that of the equivalent ARM instruction. For more

information on instruction cycle times, please refer to Chapter 10, Instruction Cycle

Operations

5-30

ARM7TDMI Data Sheet

ARM DDI 0029E

THUMB Instruction Set

5.13.3 Examples

ADD

SP, #268

; SP (R13) := SP + 268, but don't set

; the condition codes.

; Note that the THUMB opcode will

; contain 67 as the Word7 value and S=0.

ADD

SP, #-104

; SP (R13) := SP - 104, but don't set

Open Access

; the condition codes.

; Note that the THUMB opcode will contain

; 26 as the Word7 value and S=1.

ARM7TDMI Data Sheet

ARM DDI 0029E

5-31

THUMB Instruction Set

5.14 Format 14: push/pop registers

15

14

13

12

11

10

9

8

1

0

1

1

L

1

0

R

7

6

5

4

3

2

1

0

Rlist

Register list

PC/LR bit

0 - Do not store LR/load PC

1 - Store LR/Load PC

Load/Store bit

0 - Store to memory

1 - Load from memory

Open Access

Figure 5-15: Format 14

5.14.1 Operation

The instructions in this group allow registers 0-7 and optionally LR to be pushed

onto the stack, and registers 0-7 and optionally PC to be popped off the stack.

The THUMB assembler syntax is shown in Table 5-15: PUSH and POP instructions.

Note

The stack is always assumed to be Full Descending.

L

R

THUMB assembler

ARM equivalent

Action

0

0

PUSH { Rlist }

STMDB R13!, { Rlist }

Push the registers specified by

Rlist onto the stack. Update the

stack pointer.

0

1

PUSH { Rlist, LR }

STMDB R13!, { Rlist, R14 }

Push the Link Register and the

registers specified by Rlist (if any)

onto the stack. Update the stack

pointer.

1

0

POP { Rlist }

LDMIA R13!, { Rlist }

Pop values off the stack into the

registers specified by Rlist. Update

the stack pointer.

1

1

POP { Rlist, PC }

LDMIA R13!, { Rlist, R15 }

Pop values off the stack and load

into the registers specified by Rlist.

Pop the PC off the stack. Update

the stack pointer.

Table 5-15: PUSH and POP instructions

5-32

ARM7TDMI Data Sheet

ARM DDI 0029E

THUMB Instruction Set

5.14.2 Instruction cycle times

All instructions in this format have an equivalent ARM instruction as shown in Table

5-15: PUSH and POP instructions on page 5-32. The instruction cycle times for the

THUMB instruction are identical to that of the equivalent ARM instruction. For more

information on instruction cycle times, please refer to Chapter 10, Instruction Cycle

Operations.

5.14.3 Examples

PUSH

{R0-R4,LR}

; Store R0,R1,R2,R3,R4 and R14 (LR) at

;

;

;

;

POP

{R2,R6,PC}

the stack pointed to by R13 (SP) and

update R13.

Useful at start of a sub-routine to

save workspace and return address.

; Load R2,R6 and R15 (PC) from the stack

Open Access

; pointed to by R13 (SP) and update R13.

; Useful to restore workspace and return

; from sub-routine.

ARM7TDMI Data Sheet

ARM DDI 0029E

5-33

THUMB Instruction Set

5.15 Format 15: multiple load/store

15

14

13

12

11

1

1

0

0

L

10

9

8

7

6

Rb

5

4

3

2

1

0

Rlist

Register list

Base register

Load/Store bit

0 - Store to memory

1 - Load from memory

Figure 5-16: Format 15

5.15.1 Operation

Open Access

These instructions allow multiple loading and storing of Lo registers. The

THUMB assembler syntax is shown in the following table.

L

THUMB assembler

ARM equivalent

Action

0

STMIA Rb!, { Rlist }

STMIA Rb!, { Rlist }

Store the registers specified by

Rlist, starting at the base address

in Rb. Write back the new base

address.

1

LDMIA Rb!, { Rlist }

LDMIA Rb!, { Rlist }

Load the registers specified by

Rlist, starting at the base address

in Rb. Write back the new base

address.

Table 5-16: The multiple load/store instructions

5.15.2 Instruction cycle times

All instructions in this format have an equivalent ARM instruction as shown in Table

5-16: The multiple load/store instructions on page 5-34. The instruction cycle times

for the THUMB instruction are identical to that of the equivalent ARM instruction. For

more information on instruction cycle times, please refer to Chapter 10, Instruction

Cycle Operations

5-34

ARM7TDMI Data Sheet

ARM DDI 0029E

THUMB Instruction Set

5.15.3 Examples

STMIA R0!, {R3-R7}

; Store the contents of registers R3-R7

starting at the address specified in

R0, incrementing the addresses for each

word.

Write back the updated value of R0.

Open Access

;

;

;

;

ARM7TDMI Data Sheet

ARM DDI 0029E

5-35

THUMB Instruction Set

5.16 Format 16: conditional branch

15

14

13

12

1

1

0

1

11

10

9

8

7

6

Cond

5

4

3

2

1

0

SOffset8

8-bit signed immediate

Condition

Figure 5-17: Format 16

5.16.1 Operation

Open Access

The instructions in this group all perform a conditional Branch depending on the state of

the CPSR condition codes. The branch offset must take account of the prefetch

operation, which causes the PC to be 1 word (4 bytes) ahead of the current instruction.

The THUMB assembler syntax is shown in the following table.

Cond

THUMB assembler

ARM equivalent

Action

0000

BEQ label

BEQ label

Branch if Z set (equal)

0001

BNE label

BNE label

Branch if Z clear (not equal)

0010

BCS label

BCS label

Branch if C set (unsigned higher or

same)

0011

BCC label

BCC label

Branch if C clear (unsigned lower)

0100

BMI label

BMI label

Branch if N set (negative)

0101

BPL label

BPL label

Branch if N clear (positive or zero)

0110

BVS label

BVS label

Branch if V set (overflow)

0111

BVC label

BVC label

Branch if V clear (no overflow)

1000

BHI label

BHI label

Branch if C set and Z clear

(unsigned higher)

1001

BLS label

BLS label

Branch if C clear or Z set

(unsigned lower or same)

Table 5-17: The conditional branch instructions

5-36

ARM7TDMI Data Sheet

ARM DDI 0029E

THUMB Instruction Set

Cond

THUMB assembler

ARM equivalent

Action

1010

BGE label

BGE label

Branch if N set and V set, or N

clear and V clear (greater or

equal)

1011

BLT label

BLT label

Branch if N set and V clear, or N

clear and V set (less than)

1100

BGT label

BGT label

Branch if Z clear, and either N set

and V set or N clear and V clear

(greater than)

1101

BLE label

BLE label

Branch if Z set, or N set and V

clear, or N clear and V set (less

than or equal)

Note

While label specifies a full 9-bit two’s complement address, this must always be

halfword-aligned (ie with bit 0 set to 0) since the assembler actually places label >>

1 in field SOffset8.

Note

Cond = 1110 is undefined, and should not be used.

Cond = 1111 creates the SWI instruction: see 5.17 Format 17: software interrupt on

page 5-38.

5.16.2 Instruction cycle times

All instructions in this format have an equivalent ARM instruction as shown in Table

5-17: The conditional branch instructions on page 5-36. The instruction cycle times

for the THUMB instruction are identical to that of the equivalent ARM instruction.

For more information on instruction cycle times, please refer to Chapter 10,

Instruction Cycle Operations

5.16.3 Examples

over

CMP R0, #45

BGT over

...

...

...

...

...

ARM7TDMI Data Sheet

ARM DDI 0029E

; Branch to ’over’ if R0 > 45.

; Note that the THUMB opcode will contain

; the number of halfwords to offset.

; Must be halfword aligned.

5-37

Open Access

Table 5-17: The conditional branch instructions (Continued)

THUMB Instruction Set

5.17 Format 17: software interrupt

15

14

13

12

11

10

9

8

1

1

0

1

1

1

1

1

7

6

5

4

3

2

1

0

Value8

Comment field

Figure 5-18: Format 17

5.17.1 Operation

The SWI instruction performs a software interrupt. On taking the SWI, the processor

switches into ARM state and enters Supervisor (SVC) mode.

Open Access

The THUMB assembler syntax for this instruction is shown below.

THUMB assembler

ARM equivalent

Action

SWI Value8

SWI Value8

Perform Software Interrupt:

Move the address of the next instruction

into LR, move CPSR to SPSR, load the SWI

vector address (0x8) into the PC. Switch to

ARM state and enter SVC mode.

Table 5-18: The SWI instruction

Note

Value8 is used solely by the SWI handler: it is ignored by the processor.

5.17.2 Instruction cycle times

All instructions in this format have an equivalent ARM instruction as shown in Table 518: The SWI instruction on page 5-38. The instruction cycle times for the THUMB

instruction are identical to that of the equivalent ARM instruction. For more information

on instruction cycle times, please refer to Chapter 10, Instruction Cycle Operations

5.17.3 Examples

SWI 18

; Take the software interrupt exception.

; Enter Supervisor mode with 18 as the

; requested SWI number.

5-38

ARM7TDMI Data Sheet

ARM DDI 0029E

THUMB Instruction Set

5.18 Format 18: unconditional branch

15

14

13

12

11

1

1

1

0

0

10

9

8

7

6

5

4

3

2

1

0

Offset11

Immediate value

Figure 5-19: Format 18

This instruction performs a PC-relative Branch. The THUMB assembler syntax is

shown below. The branch offset must take account of the prefetch operation,

which causes the PC to be 1 word (4 bytes) ahead of the current instruction.

THUMB assembler

ARM equivalent

Action

B label

BAL label (halfword

offset)

Branch PC relative +/- Offset11 << 1, where

label is PC +/- 2048 bytes.

Table 5-19: Summary of Branch instruction

Note

The address specified by label is a full 12-bit two’s complement address, but must

always be halfword aligned (ie bit 0 set to 0), since the assembler places label >> 1

in the Offset11 field.

5.18.2 Examples

here

B here

B jimmy

...

jimmy

...

ARM7TDMI Data Sheet

ARM DDI 0029E

;

;

;

;

;

;

;

;

Branch onto itself.

Assembles to 0xE7FE.

(Note effect of PC offset).

Branch to 'jimmy'.

Note that the THUMB opcode will

contain the number of halfwords

to offset.

Must be halfword aligned.

5-39

Open Access

5.18.1 Operation

THUMB Instruction Set

5.19 Format 19: long branch with link

15

14

13

12

11

1

1

1

1

H

10

9

8

7

6

5

4

3

2

1

0

Offset

Long branch and link offset high/low

Low/high offset bit

0 - offset high

1 - offset low

Figure 5-20: Format 19

5.19.1 Operation

This format specifies a long branch with link.

Open Access

The assembler splits the 23-bit two’s complement half-word offset specifed by the

label into two 11-bit halves, ignoring bit 0 (which must be 0), and creates two

THUMB instructions.

Instruction 1 (H = 0)

In the first instruction the Offset field contains the upper 11 bits of the target

address. This is shifted left by 12 bits and added to the current PC address. The

resulting address is placed in LR.

Instruction 2 (H =1)

In the second instruction the Offset field contains an 11-bit representation lower half

of the target address. This is shifted left by 1 bit and added to LR. LR, which now

contains the full 23-bit address, is placed in PC, the address of the instruction

following the BL is placed in LR and bit 0 of LR is set.

The branch offset must take account of the prefetch operation, which causes the PC

to be 1 word (4 bytes) ahead of the current instruction

5-40

ARM7TDMI Data Sheet

ARM DDI 0029E

THUMB Instruction Set

5.19.2 Instruction cycle times

This instruction format does not have an equivalent ARM instruction. For details of

the instruction cycle times, please refer to Chapter 10, Instruction Cycle Operations.

H

THUMB assembler

ARM equivalent

Action

0

BL label

none

LR := PC + OffsetHigh << 12

1

temp := next instruction address

PC := LR + OffsetLow << 1

LR := temp | 1

Table 5-20: The BL instruction

5.19.3 Examples

BL faraway

...

faraway ...

ARM7TDMI Data Sheet

ARM DDI 0029E

; Unconditionally Branch to 'faraway'

; and place following instruction

;

;

;

;

;

;

address, ie ’next’, in R14,the Link

Register and set bit 0 of LR high.

Note that the THUMB opcodes will

contain the number of halfwords to

offset.

Must be Half-word aligned.

Open Access

next

5-41

THUMB Instruction Set

5.20 Instruction Set Examples

The following examples show ways in which the THUMB instructions may be used

to generate small and efficient code. Each example also shows the ARM equivalent

so these may be compared.

5.20.1 Multiplication by a constant using shifts and adds

The following shows code to multiply by various constants using 1, 2 or 3 Thumb

instructions alongside the ARM equivalents. For other constants it is generally

better to use the built-in MUL instruction rather than using a sequence of 4 or more

instructions.

Open Access

Thumb

ARM

1

Multiplicación por 2 n (1,2,4,8,...)

LSL Ra, Rb, LSL #n

MOV Ra, Rb, LSL #n

2

Multiplicación por 2 n+1 (3,5,9,17,...)

LSL Rt, Rb, #n

ADD Ra, Rb, Rb, LSL #n

ADD Ra, Rt, Rb

3

Multiplicación por 2 n-1 (3,7,15,...)

LSL Rt, Rb, #n

RSB Ra, Rb, Rb, LSL #n

SUB Ra, Rt, Rb

4

Multiplicación por -2 n (-2, -4, -8, ...)

LSL Ra, Rb, #n

MOV Ra, Rb, LSL #n

MVN Ra, Ra

RSB Ra, Ra, #0

5

Multiplicación por -2 n-1 (-3, -7, -15, ...)

LSL Rt, Rb, #n

SUB Ra, Rb, Rb, LSL #n

SUB Ra, Rb, Rt

6

Multiplicación por cualquier C = {2 n+1, 2 n-1, -2 n o -2 n-1} * 2 n

Effectively this is any of the multiplications in 2 to 5 followed by a final shift.

This allows the following additional constants to be multiplied.

6, 10, 12, 14, 18, 20, 24, 28, 30, 34, 36, 40, 48, 56, 60, 62 .....

5-42

(2..5)

(2..5)

LSL Ra, Ra, #n

MOV Ra, Ra, LSL #n

ARM7TDMI Data Sheet

ARM DDI 0029E

THUMB Instruction Set

5.20.2 General purpose signed divide

This example shows a general purpose signed divide and remainder routine in

both Thumb and ARM code.

Thumb code

signed_divide

; Signed divide of R1 by R0: returns quotient in R0,

; remainder in R1

; Get abs

ASR

EOR

SUB

value of R0 into R3

R2, R0, #31 ; Get 0 or -1 in R2 depending on sign of R0

R0, R2

; EOR with -1 (0xFFFFFFFF) if negative

R3, R0, R2 ; and ADD 1 (SUB -1) to get abs value

; SUB always sets flag so go & report division by 0 if necessary

BEQ divide_by_zero

; Get abs value of R1 by xoring with 0xFFFFFFFF and adding 1

; if negative

ASR R0, R1, #31 ; Get 0 or -1 in R3 depending on sign of R1

EOR R1, R0

; EOR with -1 (0xFFFFFFFF) if negative

SUB R1, R0

; and ADD 1 (SUB -1) to get abs value

; Save signs (0 or -1 in R0 & R2) for later use in determining

; sign of quotient & remainder.

PUSH {R0, R2}

; Justification, shift 1 bit at a time until divisor (R0 value)

; is just <= than dividend (R1 value). To do this shift dividend

; right by 1 and stop as soon as shifted value becomes >.

LSR R0, R1, #1

MOV R2, R3

B

%FT0

just_l

LSL

0

CMP

BLS

R2, #1

R2, R0

just_l

MOV

B

R0, #0

%FT0

div_l

LSR

0

CMP

BCC

SUB

R2, #1

R1, R2

%FT0

R1, R2

ARM7TDMI Data Sheet

ARM DDI 0029E

; Set accumulator to 0

; Branch into division loop

; Test subtract

; If successful do a real

; subtract

5-43

Open Access

;

THUMB Instruction Set

0

CMP

BNE

ADC

R2, R3

div_l

R0, R0; Shift result and add 1 if

; subtract succeeded

; Terminate when R2 == R3 (ie we have just

; tested subtracting the 'ones' value).

; Now fixup the signs of the quotient (R0) and remainder (R1)

POP

{R2, R3} ; Get dividend/divisor signs back

EOR

EOR

SUB

R3, R2

R0, R3

R0, R3

; Result sign

; Negate if result sign = -1

EOR

SUB

R1, R2

R1, R2

; Negate remainder if dividend sign = -1

MOV

pc, lr

ARM code

Open Access

signed_divide

; effectively

ANDS

RSBMI

EORS

; ip bit 31 =

; ip bit 30 =

RSBCS

zero a4

a4, a1,

a1, a1,

ip, a4,

sign of

sign of

a2, a2,

as top bit will be shifted out later

#&80000000

#0

a2, ASR #32

result

a2

#0

; central part is identical code to udiv

; (without MOV a4, #0 which comes for free as part of signed

; entry sequence)

MOVS

a3, a1

BEQ

divide_by_zero

just_l

; justification stage shifts 1 bit at a time

CMP

a3, a2, LSR #1

MOVLS

a3, a3, LSL #1

; NB: LSL #1 is always OK if LS succeeds

BLOs_loop

div_l

5-44

CMP

ADC

SUBCS

a2, a3

a4, a4, a4

a2, a2, a3

TEQ

MOVNE

a3, a1

a3, a3, LSR #1

ARM7TDMI Data Sheet

ARM DDI 0029E

THUMB Instruction Set

BNE

MOV

s_loop2

a1, a4

MOVS

RSBCS

RSBMI

ip, ip, ASL #1

a1, a1, #0

a2, a2, #0

MOV

pc, lr

5.20.3 Division by a constant

Division by a constant can often be performed by a short fixed sequence of shifts,

adds and subtracts. For an explanation of the algorithm see The ARM Cookbook

(ARM DUYI-0005B), section entitiled Division by a constant.

Here is an example of a divide by 10 routine based on the algorithm in the

ARM Cookbook in both Thumb and ARM code.

Thumb code

ARM7TDMI Data Sheet

ARM DDI 0029E

Open Access

udiv10

; takes argument in a1

; returns quotient in a1, remainder in a2

MOV

a2, a1

LSR

a3, a1, #2

SUB

a1, a3

LSR

a3, a1, #4

ADD

a1, a3

LSR

a3, a1, #8

ADD

a1, a3

LSR

a3, a1, #16

ADD

a1, a3

LSR

a1, #3

ASL

a3, a1, #2

ADD

a3, a1

ASL

a3, #1

SUB

a2, a3

CMP

a2, #10

BLT

%FT0

ADD

a1, #1

SUB

a2, #10

0

MOV

pc, lr

5-45

THUMB Instruction Set

ARM code

remainder in a2

lsr

lsr

lsr

lsr

#3

asl

asl

#2

#4

#8

#16

#2

#1

Open Access

udiv10

; takes argument in a1

; returns quotient in a1,

SUB

a2, a1, #10

SUB

a1, a1, a1,

ADD

a1, a1, a1,

ADD

a1, a1, a1,

ADD

a1, a1, a1,

MOV

a1, a1, lsr

ADD

a3, a1, a1,

SUBS

a2, a2, a3,

ADDPL

a1, a1, #1

ADDMI

a2, a2, #10

MOV

pc, lr

5-46

ARM7TDMI Data Sheet

ARM DDI 0029E