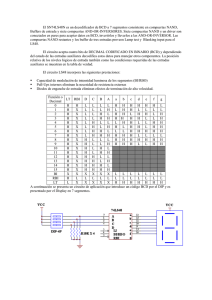

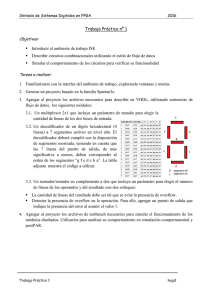

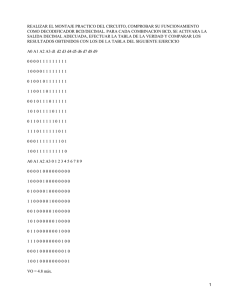

BENEMÉRITA UNIVERSIDAD AUTÓNOMA DE PUEBLA Facultad de ciencias de la computación. Sistemas digitales JOSE J. OIDOR GARCIA Practica 2: Codificador BCD a 7 segmentos Codificador hexadecimal a 7 segmentos Medio sumador de 1 bit Sumador secuencial de 1x1 Equipo 2: Melissa Arce Arce 201503386 arce.melisaaoutlok.com Cinthia Salamanca López 201547305 citsal11gmail.com Contenido Objetivo .............................................................................................................................................. 3 Resumen ............................................................................................................................................. 3 Introducción........................................................................................................................................ 4 Marco teórico ..................................................................................................................................... 4 Tabla de verdad del flip-flop tipo D .................................. Ошибка! Закладка не определена. Diagrama temporal del flip-flop tipo D ............................. Ошибка! Закладка не определена. Resultados................................................................................. Ошибка! Закладка не определена. Compuertas. .......................................................................... Ошибка! Закладка не определена. Registros y flip-flop tipo D. .................................................... Ошибка! Закладка не определена. Memoria ................................................................................ Ошибка! Закладка не определена. Discusión de resultados...................................................................................................................... 4 Conclusión ........................................................................................................................................... 5 Bibliografía .......................................................................................................................................... 6 Apéndice ............................................................................................................................................. 7 Objetivo Realizar un decodificador a BCD a 7 segmentos y un hexadecimal a 7 segmentos, para poder comprender los estados lógicos las entradas y salidas, también realizar sumadores para conocer los circuitos aritméticos y sus funcionalidades. Resumen DECODIFICADOR Es un elemento digital que funciona a base de estados lógicos, con los cuales indica una salida determinada basándose en un dato de entrada característico, su función operacional se basa en la introducción a sus entradas de un número en código binario correspondiente a su equivalente en decimal para mostrar en los siete pines de salida establecidos para el integrado, una serie de estados lógicos que están diseñados para conectarse a un elemento alfanumérico en el que se visualizará el número introducido en las entradas del decodificador. El elemento alfanumérico que se conecta a las siete salidas del decodificador también está diseñado para trabajar con estados lógicos, es un dispositivo elaborado con un arreglo de LED de tal manera que muestre los números decimales desde el cero hasta el nueve dependiendo del dato recibido desde el decodificador, a este elemento se le conoce con el nombre de display ó dispositivo alfanumérico de 7 segmentos. El decodificador está formado internamente por compuertas lógicas y sus conexiones internas son un sistema predefinido por el diseñador para que su función operacional sea un acople perfecto y efectivo con el display, observe como se muestran a continuación en las especificaciones del fabricante. SUMADORES Un sumador es un circuito que realiza la suma de dos palabras binarias. Es distinta de la operación OR, con la que no nos debemos confundir. La operación suma de números binarios tiene la misma mecánica que la de números decimales. Por lo que en la suma de números binarios con dos o más bits, puede ocurrir el mismo caso que podemos encontrar en la suma de números decimales con varias cifras: cuando al sumar los dos primeros dígitos se obtiene una cantidad mayor de 9, se da como resultado el dígito de menor peso y “me llevo" el anterior a la siguiente columna, para sumarlo allí. En la suma binaria de los dígitos 1 + 1, el resultado es 0 y me llevo 1, que debo sumar en la columna siguiente y pudiéndose escribir 10, solamente cuando sea la última columna a sumar. A este bit más significativo de la operación de sumar, se le conoce en inglés como carry (acarreo), equivalente al “me llevo una” de la suma decimal. Introducción Los circuitos lógicos electrónicos son aquellos que solo funcionan con 0 y 1, es decir en notación binaria, en otras palabras, los circuitos lógicos o digitales solo encienden si están en 1, eléctricamente hablando cuando se alimenta con 5 V y apagados en 0 cuando no están alimentados y van a tierra o ground. Con el uso del lenguaje de programación VHDL y las tarjetas digitales, es posible implementar las compuertas básicas por medio del desarrollo de un código y el uso de la arquitectura de la tarjeta digital Nexys 3, que son las compuertas AND, OR y el inversor los cuales definiremos a detalle más adelante. Marco teórico // En este proyecto se desea visualizar los número del 0 al 9 en un display 7 segmentos, de acuerdo a las posiciones de un dip switch. Decodificador bcd a 7 segmentos . Para el decodificar utilizamos una entrada y una salida las cuales las llamamos BDC y SieteSeg. BCD incluye 4 bits del 0 al 3 ya que serán los que utilizaremos de entrada. SieteSeg tiene 7 bits del 0 al 6 que serán de salida al display de 7 segmentos Creamos una función Deco la cual contendrá los bits de entrada y salida para que se puedan visualizar en el display Decodificador HEXADECIMAL a 7 segmentos MEDIO SUMADOR SUMADOR COMPLETO. Discusión de resultados Dado la teoría los resultados de la implementación de las practicas realizadas dio el resultado esperado. Tomando como datos de entrada las palancas de la Nexys y por medio de la lógica de la programación, se realizaron las compuertas y se comprobó que responden según su tabal de verdad que se especificó. CÓDIGO BCD 7 SEGMENTOS CÓDIGO HEXADECIJMAL 7 SEGMENTOS CÓDIGO SUMADOR COMPLETO library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity SumCompleto is Port ( a : in STD_LOGIC; b : in STD_LOGIC; cin : in STD_LOGIC; f : out STD_LOGIC; cout : out STD_LOGIC); end SumCompleto; architecture Behavioral of SumCompleto is begin f <=a xor b xor cin; cout<= (a and b) or (cin and (a xor b)); end Behavioral; CÓDIGO MEDIO SUMADOR library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity Mediosum is Port ( A : in STD_LOGIC; B : in STD_LOGIC; Cout : out STD_LOGIC; S : out STD_LOGIC); end Mediosum; architecture Behavioral of Mediosum is begin if(A AND then Cout <= 1; else Cout <=0; end if Mediosum: process begin Cout <= A AND B; S <= A XOR B; wait; end process; end Behavioral; Conclusión // Luego de elaborado esta práctica, llegamos a las conclusiones sobre la importancia para programar en Xilinx con lenguaje VHDL, no solo se debe tener conocimientos informáticos, sino también de compuertas lógicas, sistemas de numeración. Para poder implementar los Flip-Flop se requirió tener conocimiento de las compuertas y de el uso de estos para poder implementar los registros y la memoria. Además del uso adecuado de el lenguaje de programación VHDL que dado la versión en la que estemos trabajando podría cambiar alguna característica. Bibliografía // David G. Maximinez Jessica Alcalá. (2002). VHDL El arte de programar Sistemas Digitales. México: Continental. Baule R. Edison Rodríguez F. Cheyn. (2012). Circuitos Lógicos Electrónicos. Panamá: Azuero. Apéndice