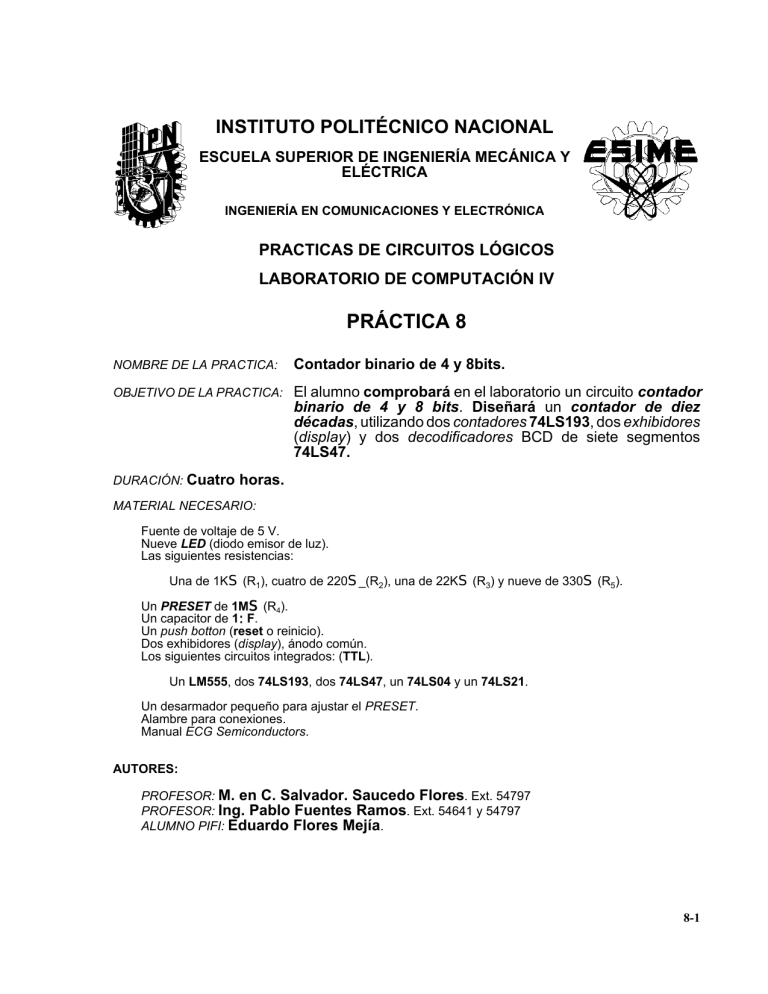

INSTITUTO POLITÉCNICO NACIONAL ESCUELA SUPERIOR DE INGENIERÍA MECÁNICA Y ELÉCTRICA INGENIERÍA EN COMUNICACIONES Y ELECTRÓNICA PRACTICAS DE CIRCUITOS LÓGICOS LABORATORIO DE COMPUTACIÓN IV PRÁCTICA 8 NOMBRE DE LA PRACTICA: Contador binario de 4 y 8bits. OBJETIVO DE LA PRACTICA: El alumno comprobará en el laboratorio un circuito contador binario de 4 y 8 bits. Diseñará un contador de diez décadas, utilizando dos contadores 74LS193, dos exhibidores (display) y dos decodificadores BCD de siete segmentos 74LS47. DURACIÓN: Cuatro horas. MATERIAL NECESARIO: Fuente de voltaje de 5 V. Nueve LED (diodo emisor de luz). Las siguientes resistencias: Una de 1KS (R1), cuatro de 220S_(R2), una de 22KS (R3) y nueve de 330S (R5). Un PRESET de 1MS (R4). Un capacitor de 1:F. Un push botton (reset o reinicio). Dos exhibidores (display), ánodo común. Los siguientes circuitos integrados: (TTL). Un LM555, dos 74LS193, dos 74LS47, un 74LS04 y un 74LS21. Un desarmador pequeño para ajustar el PRESET. Alambre para conexiones. Manual ECG Semiconductors. AUTORES: PROFESOR: M. en C. Salvador. Saucedo Flores. Ext. 54797 PROFESOR: Ing. Pablo Fuentes Ramos. Ext. 54641 y 54797 ALUMNO PIFI: Eduardo Flores Mejía. 8-1 CONTADOR 74193 (LS193/HC193) La Figura 8-1, muestra un contador ascendente/descendente preiniciable 74193, indicando: (a) símbolo lógico, (b) descripción entrada/salida y (c) tabla de selección de modos. La Figura 8-1, muestra el símbolo lógico y la descripción de entrada y salida del contador 74193. Este contador puede describirse como un contador ascendente/ descendente preiniciable MOD-16 con conteo síncrono, preiniciación asíncrona y reiniciación maestra asíncrona. Observemos la función de cada entrada y salida: ENTRADAS DE RELOJ CPU y CPD El contador responderá a las TPP (Transición de Pendiente Positiva) en una de las dos entradas de reloj. CPU es la entrada de reloj de conteo ascendente. Cuando se apliquen los pulsos a esta entrada, el contador se incrementará (contará hacia arriba) en cada TPP hasta llegar a un conteo máximo de 1111; entonces se recicla a 0000 y vuelve a comenzar. CPD es la entrada de reloj de conteo descendente. Cuando se apliquen los pulsos a esta entrada, el contador decrementará (contará hacia abajo) en cada TPP hasta llegar a un conteo mínimo de 0000; entonces se recicla a 1111 y vuelve a comenzar. De este modo se usará una entrada de reloj para contar en tanto la otra esté inactiva (se conserva en ALTO). REINICIACIÓN MAESTRA (MR). Esta es una entrada asíncrona activa en ALTO que reinicia al contador en el estado 0000. MR es un reiniciador de cd (corriente directa), de manera que tendrá al contador en 0000 en tanto que MR=1. También elimina todas las otras entradas. ENTRADAS PREINICIABLES. Los multivibradores (flip-flop) del contador pueden preiniciarse en los niveles lógicos presentes en las entradas de datos paralelas P0-P3 pulsando momentáneamente la entrada de carga paralela de ALTO a BAJO. Esta es una preiniciación asíncrona que elimina la operación de conteo. No obstante, en su estado activo en ALTO. no tendrá efecto si la entrada MR se encuentra SALIDAS DEL CONTEO. El conteo regular siempre esta presente en las salidas Q0-Q3 de los MVB (MultiViBrador), donde Q3 es el LSB (bit menos significativo) y Q0 el MSB (bit más significativo). M. en C. Salvador Saucedo Flores e Ing. Pablo Fuentes Ramos 8-2 SALIDAS FINALES DEL CONTEO. Estas salidas se utilizan cuando dos o más unidades del 74LS193 se conectan como contador con etapas múltiples para producir un número MOD mayor. En el modo de conteo ascendente, la salida del contador de orden inferior se conecta a la entrada CPU del siguiente contador de orden superior. En el modo de conteo descendente, la salida del contador de orden inferior se conecta a la entrada CPD del siguiente contador de orden superior. es el conteo ascendente final (también llamado acarreo). Se genera en el 74193 utilizando la lógica que se muestra en la Figura 8-2 (a). Evidentemente será BAJO sólo cuando el contador se encuentre en el estado 1111 y CPU sea BAJO. Así, permanecerá en ALTO cuando el contador cuente hacia arriba de 0000 a 0001. En la siguiente TPP de CPU, el conteo pasa a 1111, pero no pasa a BAJO sino hasta que CPU retorna a BAJO. La siguiente TPP en CPU recicla el contador a 0000 y también ocasiona que retorne a ALTO. Esta TPP en ocurre cuando el contador se recicla de 1111 a 0000 y se puede utilizar para cronometrar un segundo contador ascendente 74193 a su siguiente conteo superior. es la salida del conteo descendente final (también llamado préstamo). Se genera como se muestra en la Figura 8-2 (b). Normalmente es ALTO y no pasa a BAJO sino hasta que el contador haya contado hacia a abajo hasta el estado 0000 y CPD sea BAJO. Cuando la siguiente TPP en CPD recicla el contador a 1111, ocasiona que retorne a ALTO. Esta TPP en TCD se puede usar para cronometrar un segundo contador descendente 74193 en su siguiente conteo inferior. DIRECCIÓN DEL CONTEO (+ o -). Las entradas CPU y CPD se muestran como dos etiquetas distintas porque tienen efectos internos diferentes. Primero se considerará la etiqueta superior. Esta etiqueta para la entrada CPU es 2+. El signo (+) indica que una TPP en esta entrada incrementará en uno el conteo; en otras palabras, causará que el contador cuente de manera ascendente. Del mismo modo, la etiqueta superior para la entrada CPD tiene un signo menos (-) para señalar que esta entrada disminuye en 1 el valor del conteo; en otras palabras; causa que el conteo sea descendente. M. en C. Salvador Saucedo Flores e Ing. Pablo Fuentes Ramos 8-3 PROCEDIMIENTO EXPERIMENTAL Armar el siguiente circuito: Circuito topológico 1. Contador binario de 0 a 15. Ajustar la resistencia en el preset con el desarmador de tal forma que se pueda observar el conteo binario en los LED. Comprobar la numeración binaria de 0 a 15. Conectar P1 y P2 (terminales 1 y 10) a Vcc. Desconectar (terminal 11) de Vcc. Y conectarla a (terminal 12). Observar y anotar lo que sucede en los LED. Regresar P1 y P2 a GND (tierra) y desconectar de y conectar a Vcc. Conectar la señal del reloj a CPD (terminal 4, conteo descendente), y CPU (terminal 5, conteo ascendente) a Vcc. Observar y comprobar el conteo binario descendente de 15 a 0. Conectar P1 y P2 a Vcc (terminales 1 y 10), desconectar conectarla a de Vcc. (Terminal 11) y (terminal 13). Anotar lo que sucede. M. en C. Salvador Saucedo Flores e Ing. Pablo Fuentes Ramos 8-4 Armar el siguiente circuito. Circuito topológico 2. Contador binario de 0 a 255 Observar el conteo binario ascendente en los ocho LED. Realizar las conexiones necesarias para que el conteo binario sea descendente (de 255 a 0). Armar el siguiente circuito Diagrama topológico 3. Circuito que cuenta de 0 a 99. Con el desarmador modificar la resistencia del preset y al mismo tiempo observar los exhibidores (display). Como las salidas Q0 Q1 Q2 Q3, realizan su conteo binario de 0 a 15 y para un conteo decimal nada más se necesita de 0 a 9; entonces se le adapta una compuerta Y (AND) de 4 entradas al contador de tal forma que cuando se encuentre el conteo en 10b (1010) se ajusta la conexión con dos inversores para poder activar la compuerta Y y su salida se utiliza para activar a MR (reiniciación maestra) para llevar al contador a 0000 obteniendo un ciclo en el contador de 0 a 9. M. en C. Salvador Saucedo Flores e Ing. Pablo Fuentes Ramos 8-5 Esta misma salida invertida incrementará el contador de las decenas (contador 2). Usando el 74LS192 el diseño se hubiera facilitado mucho. De esta misma manera se obtiene el ciclo de 0 a 9 para las decenas, lo cual se observa en el logigrama siguiente. CUESTIONARIO En el circuito topológico 3 1. ¿Qué sucede al aumentar la resistencia en el preset? 2. ¿Qué sucede al disminuir la resistencia en el preset? 3. ¿Cuál es la cantidad máxima que aparece en los exhibidores (display)? En el circuito integrado 74193 4. ¿Qué utilidad tienen las entradas preiniciables? 5. ¿Qué relación tiene CPU y 6. ¿Qué relación tiene CPD y . . M. en C. Salvador Saucedo Flores e Ing. Pablo Fuentes Ramos 8-6 7. ¿Qué relación tiene CPU y . 8. ¿Que utilidades le puedes dar a este contador? Menciona tres de ellas. 9. Diseñar un circuito de contador de seis décadas, (0 a 60), basándose en el diseño del circuito topológico 3 y su logigrama. 10. Diseñar un reloj que contenga seis exhibidores (display), dos que indiquen las horas, dos que indiquen los minutos y dos que indiquen los segundos. Recordar que el conteo en los dos exhibidores de las horas son de 1 a 12 ó de 0 a 24, y en los minutos y segundos de 0 a 60. M. en C. Salvador Saucedo Flores e Ing. Pablo Fuentes Ramos 8-7