Dispositivos Lógicos Programables - Universidad Nacional del Litoral

Anuncio

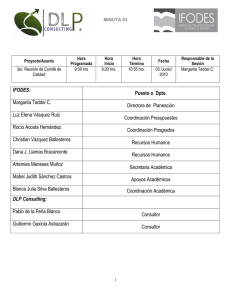

Dispositivos Lógicos Programables Dispositivos Lógicos Programables 2011 Facultad de Ingeniería y Ciencias Hídricas Universidad Nacional del Litoral Hoy, 17 de agosto veremos… • ¿Cuál es la gama de dispositivos lógicos programables que ofrece el mercado? – PAL, PLA, GAL, CPLD y FPGA • ¿Qué herramientas están disponibles para programarlos? – Genéricas – Propias de los fabricantes de DLP: MaxPlus, ISE • Breve introdución a los lenguajes de descripción de hardware – VHDL DLP 2011 Slides de la Unidad 1 Santiago Roatta PLDs vs. ASICs (2003) DLP 2011 Slides de la Unidad 1 Santiago Roatta Clasificación de los Dispositivos Lógicos Programables Simples: PLA, PAL, GAL Complejos: CPLD FPGA DLP 2011 Slides de la Unidad 1 Santiago Roatta PLA Es un dispositivo AND-OR combinacional de dos niveles, el cual se puede programar para que realice cualquier expresión lógica de suma de productos, sujeta a limitaciones de tamaño del dispositivo. Las limitaciones son: número de entradas (n) número de salidas (m) número de términos de producto (p) DLP 2011 Slides de la Unidad 1 Santiago Roatta Circuito Interno de una PLA 4 x 8 x 4 DLP 2011 Slides de la Unidad 1 Santiago Roatta Ejercicio: Implementar un sumador con una PLA DLP 2011 Slides de la Unidad 1 Santiago Roatta Tabla de verdad del sumador DLP 2011 Slides de la Unidad 1 Santiago Roatta Implementación del sumador DLP 2011 Slides de la Unidad 1 Santiago Roatta PLA, PAL y GAL PLA: Dispositivo AND-OR de dos niveles, en donde las matrices AND y OR son ambas programables. PAL: Solo la matriz AND es programable GAL: Es reprogramable ¡ Incluyen una macrocelda OLMC de salida para implementar sistemas secuenciales ! DLP 2011 Slides de la Unidad 1 Santiago Roatta Arquitectura de una PLA DLP 2011 Slides de la Unidad 1 Santiago Roatta Arquitectura de una PAL DLP 2011 Slides de la Unidad 1 Santiago Roatta Arquitectura de una GAL: GAL 16V8 DLP 2011 Slides de la Unidad 1 Santiago Roatta Macrocelda de una PALCE16V8 DLP 2011 Slides de la Unidad 1 Santiago Roatta Configuración de la macrocelda DLP 2011 Slides de la Unidad 1 Santiago Roatta Configuración de la macrocelda DLP 2011 Slides de la Unidad 1 Santiago Roatta Arquitectura de un CPLD DLP 2011 Slides de la Unidad 1 Santiago Roatta Arquitectura CPLD típica DLP 2011 Slides de la Unidad 1 Santiago Roatta Bloque lógico CPLD DLP 2011 Slides de la Unidad 1 Santiago Roatta CPLD: LAB con dos macroceldas DLP 2011 Slides de la Unidad 1 Santiago Roatta CPLDs de Altera DLP 2011 Slides de la Unidad 1 Santiago Roatta CPLDs de Xilinx DLP 2011 Slides de la Unidad 1 Santiago Roatta FPGA DLP 2011 Slides de la Unidad 1 Santiago Roatta FPGA: Celda I/O DLP 2011 Slides de la Unidad 1 Santiago Roatta FPGAs de Xilinx DLP 2011 Slides de la Unidad 1 Santiago Roatta ¿Cómo programar un DLP? DLP 2011 Slides de la Unidad 1 Santiago Roatta ISE 8.2 Herramienta de Xilinx para implementar aplicaciones sobre dispositivos lógicos programables Está instalada en el Laboratorio III DLP 2011 Slides de la Unidad 1 Santiago Roatta VHDL • Es un lenguaje de descripción de hardware, no un lenguaje de programación • Permite especificar con precisión el comportamiento de un sistema digital. • Los diseños pueden descomponerse jerárquicamente. • Es posible diseñar y sintetizar desde un circuito combinacional hasta un microprocesador completo en un chip. • Cada elemento tiene: – Una interfaz bien definida (para conectarlo a otros elementos) – Una especificación de comportamiento DLP 2011 Slides de la Unidad 1 Santiago Roatta VHDL • Cada componente tiene su entidad y su arquitectura. • La definición de la arquitectura de un componente puede realizarse de diferentes maneras: – Estructural (structural modeling) – Funcional o de comportamiento (behavioral modeling) – A nivel de transferencia de registros (RTL) o de flujo de datos (dataflow modeling) DLP 2011 Slides de la Unidad 1 Santiago Roatta VHDL DLP 2011 Slides de la Unidad 1 Santiago Roatta VHDL DLP 2011 Slides de la Unidad 1 Santiago Roatta Ejemplo VHDL: puerta AND DLP 2011 Slides de la Unidad 1 Santiago Roatta Ejemplo VHDL: puerta AND con retardo DLP 2011 Slides de la Unidad 1 Santiago Roatta VHDL concurrente y secuencial • Una arquitectura definida con un estilo funcional o de comportamiento (behavioral modeling) es secuencial. • La definición estructural (structural modeling) es concurrente. DLP 2011 Slides de la Unidad 1 Santiago Roatta Descripción de Comportamiento • Utiliza el proceso: es una sentencia concurrente, pero lo que está dentro es secuencial • Algunas sentencias secuenciales: – Condicionales: wait, if-then-else, case – Bucles: loop, for, while, exit, next – Importante!! Las variables se pueden definir solamente dentro de un proceso. DLP 2011 Slides de la Unidad 1 Santiago Roatta Descripción Estructural • Es concurrente y refleja adecuadamente el hardware. • Está organizada: – Zona de definiciones: señales internas y componentes a utilizar; y definición de la arquitectura de los componentes. – Instanciar los componentes: (conectarlos entre sí) – Definiciones concurrentes, por ejemplo: • • • DLP 2011 Bloques When With… select (es equivalente a if-then-else) (es equivalente a case) Slides de la Unidad 1 Santiago Roatta Ejemplo: Máquina de estado DLP 2011 Slides de la Unidad 1 Santiago Roatta Ejemplo: Máquina de estado DLP 2011 Slides de la Unidad 1 Santiago Roatta Ejemplo: Descripción en VHDL de la máquina de estado DLP 2011 Slides de la Unidad 1 Santiago Roatta DLP 2011 Slides de la Unidad 1 Santiago Roatta DLP 2011 Slides de la Unidad 1 Santiago Roatta Ejemplo de Descripción Estructural DLP 2011 Slides de la Unidad 1 Santiago Roatta Ejemplo de Descripción Estructural DLP 2011 Slides de la Unidad 1 Santiago Roatta