1.2 Análisis de los Componentes.

Anuncio

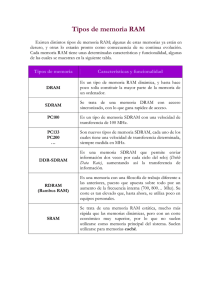

1.2 Análisis de los Componentes. Arquitectura de Computadoras Rafael Vazquez Perez 1.2.2 Memorias • 1 Conceptos básicos de manejo de la memoria • 2 Memoria principal semiconductora • 3 Memoria Cache Conceptos Básicos del Manejo de la memoria • Una memoria es un dispositivo que puede mantenerse en por lo menos dos estados estables por un cierto periodo de tiempo. • Cada uno de estos estados estables puede utilizarse para representar un bit. • A un dispositivo con la capacidad de almacenar por lo menos un bit se le conoce como celda básica de memoria. Conceptos Básicos del Manejo de la memoria • Un dispositivo de memoria completo se forma con varias celdas básicas y los circuitos asociados para poder leer y escribir dichas celdas básicas, agrupadas como localidades de memoria que permitan almacenar un grupo de N bits. • El número de bits que puede almacenar cada localidad de memoria es conocido como el ancho de palabra de la memoria. • Coincide con el ancho del bus de datos. Conceptos Básicos del Manejo de la memoria Conceptos Básicos del Manejo de la memoria Decodificación por filas y columnas Conceptos Básicos del Manejo de la memoria • Uno de los circuitos auxiliares que integran la memoria es el decodificador de direcciones. • Su función es la de activar a las celdas básicas que van a ser leídas o escritas a partir de la dirección presente en el bus de direcciones. • Tiene como entradas las n lineas del bus de direcciones y 2n lineas de habilitación de localidad, cada una correspondiente a una combinación binaria distinta de los bits de direcciones. • Por lo tanto, el número de localidades de memoria disponibles en un dispositivo (T) se relaciona con el número de lineas de dirección 2n . Resumen sobre conceptos básicos de la memoria Resumen sobre conceptos básicos de la memoria Jerarquías de Memoria Memoria Principal Semiconductora • Memoria semiconductora: matriz de celdas que contienen 1 ó 0, donde cada celda se especifica por una dirección compuesta por su fila (ROW) y su columna (COLUMN). Para su implementación se usan de transistores en semiconductores. • Operaciones básicas: lectura y escritura de datos. Conexión al exterior mediante bus de datos, direcciones y control. • • • Memoria Principal Semiconductora Existen 2 categorías principales: ROM (read-only memory): los datos se almacenan de forma permanente o semipermanentememorias no volátiles. RAM (random-access memory): se tarda lo mismo en acceder a cualquier dirección de memoria (acceso en cualquier orden), capacidad de lectura y escritura, memorias volátiles. Existen 2 tipos de memoria ram : SRAM (estáticas) y DRAM (dinámicas). Memorias de acceso aleatorio estáticas (SRAM, static RAM) • • • • • Utilización de flip-flops para almacenar celdas. Rapidez de acceso a los datos. Tecnología con la que se implementan las memorias caché. Dos tipos: asíncronas y síncronas de ráfaga. Diferencia: utilización de la señal de reloj del sistema para sincronizar todas las entradas este reloj. Modo ráfaga en las SRAM síncronas: leer o escribir en varias posiciones de memoria (hasta 4) utilizando una única dirección. También presente en memorias DRAM. Estructura externa de una SRAM asíncrona Estructura interna de una SRAM asíncrona Diagrama de tiempos de R/W en una SRAM asíncrona • Tiempo de acceso: tiempo transcurrido desde que se hace la petición(dirección a la entrada del bus de direcciones) hasta que se accede al dato. • Tiempo de ciclo (ciclo de lectura/escritura): tiempo mínimo que debe transcurrir entre dos peticiones de lectura y escritura. Diagrama de tiempos de R/W en una SRAM asíncrona Fundamentos de memorias DRAM • • • • • Celdas implementadas mediante un condensador en vez de un latch/flip flop, mayor densidad de almacenamiento a un menor costo. Se pasa de 6 transistores a 1 transistor. Transistor MOS (MOSFET). El transistor actúa como interruptor. Guarda la mínima carga eléctrica posible para luego poder ser leída mediante un circuito de amplificación: cargado (1) o descargado (0). Acceso por fila (linea de palabra) y por columna (línea de bit). • • • • • Fundamentos de memorias DRAM Memorias más lentas que las SRAM: se prioriza el bajo costo y la mayor capacidad de almacenamiento. Requieren refresco periódico (Dynamic RAM): el condensador se descarga. Tiempo de ciclo > tiempo de acceso. Multiplexación de direcciones: ahorro de pines en los chips de memoria. Las SRAM al tener menor capacidad, no tenían ese problema. Una dirección se divide/multiplexa en dos partes: fila (parte alta) y columna (parte baja). Señales necesarias: RAS# y CAS#. RAS# (row access strobe): validación de la fila. CAS# (column access strobe): validación de la columna. Asíncronas y síncronas: intercambio de señales entre la memoria y el procesador ó utilización de una señal de reloj • • Memorias DRAM asincronas Memorias FPM RAM • Una operación de lectura/escritura consiste en una secuencia de accesos donde sólo el primero especifica la fila y la columna. El resto se realizan sobre la misma fila (página) especificando sólo la columna. • • • El primer acceso es el más lento. Se puede llegar a ahorrar hasta un 50% en el tiempo de acceso. Problema/desventaja: a la subida de CAS se quita el dato de salida del bus de datos. Esto limitaba el tiempo que tenían los procesadores para leer el dato antes de ser quitado de la salida del bus de datos. Memorias EDO RAM • Similares a las FPM. Mantiene el dato válido más tiempo: se guarda el dato en un buffer y no así no se elimina del bus a la subida de la señal CASExtended Out. Así la CPU tiene más tiempo para leer dato. • Aumenta la frecuencia de funcionamiento hasta los 40 mhz consiguiendo una mejora en el rendimiento de un 40% respecto FPM. Memorias BEDO RAM (Burst EDO RAM) • Una vez que se haya proporcionado una dirección de columna las siguientes direcciones se generan internamente mediante un contador modo ráfaga (burst). Frecuencia 66mhz. Refresco de DRAM • • • • • • • • • • Operación de re-escritura periódica de la información de la DRAM. La realiza un circuito de refresco que puede ser independiente o estar dentro de la memoria DRAM. Actualmente integrado dentro. El refresco puede interferir con los ciclos de acceso a la memoria. Con cada acceso a la DRAM, para lectura o escritura, se refresca una fila completa de la matriz de bits. Se refrescan simultáneamente todos los chips (del SIMM ó DIMM). Supone una bajada en el rendimiento de la RDAM: a veces la DRAM no está disponible. Diseñadores intentan que sea menos del 5% del tiempo total. Tiempo de refresco (TR): Tiempo máximo que puede transcurrir entre dos accesos consecutivos a una misma fila de la DRAM. Si no se respeta el tiempo de refresco, la memoria pierde la información por descarga del condensador de la celda de bit. Precarga Controlador de la memoria • • • Los chips de DRAM no se conectan directamente al bus. El controlador de memoria adapta las señales del procesador a las de la memoria. Funciones: Traducción de la dirección que envía el procesador en filas y columnas. Activar señales de control: RAS#, CAS#, ... Sincronización con todos los chips de DRAM. Selección módulo DRAM (en DIMMs). Refresco. A veces esta función (o parte de ella) ya va incluida en los propios chips de DRAM. Verificar paridad. • • • • • Estructura de un controlador de memoria DRAM Módulos de Memoria DRAM • • • Los chips de memoria DRAM se agrupan en circuitos impresos que constituyen módulos de memoria y que son usados para ser directamente insertados len el motherboard. Antiguamente (procesadores anteriores a los Intel 386) la memoria DRAM iba soldada a la placa base como el resto de circuitos. Estos módulos están estandarizados y han evolucionado en paralelo a los diferentes tipos de DRAMs. Módulos de Memoria DRAM • • • • • SIP (Single In-Line Package): hasta 256KB. Bus de datos de 8 bits. Usados en i80386 e i80486. SIMM (Single In-Line Memory Module): 30 contactos: memorias FPM/EDO, bus datos de 8 bits, 4-6 MB. Usados en i80386 e i80486. 72 contactos: memorias FPM/EDO, bus datos de 32 bits, 4- 32 MB. Usados en i80486 y primeros Pentium. DIMM (Dual In-Line Memory Module) : memorias SDRAM, 168 contactos, bus de datos de 32 ó 64 bits efectivos (sin bits paridad), 4-512 MB. Procesadores Pentium. DIMM DDR (DIMM Double Data Rate): memorias DDR. Hasta 240 contactos. Bus de datos de 64 bits efectivos. Módulos de hasta 2 GBs. Procesadores Pentium 4. RIMM ó PS/2 (Rambus In-Line Memory Module): memorias RAMBUS. Bus de datos de 32 bits. Primeros procesadores Pentium 4 y Play Station 2. • • Módulos de Memoria DRAM • • Ejemplo conexión memoria DRAM en Pentium IV La conexión de la memoria DRAM a un Pentium IV se hace a través de la placa base/madre ó chipset. Es un circuito impreso (PCB: Printed Circuit Board) que soporta y conecta los elementos básicos de un PC. Contiene generalmente dos chips principales llamados coloquialmente “puente norte” y “puente sur”. Están comunicados entre si a través de un bus interno y sirven de nexo entre todos los componentes del PC, incluída la memoria. El “puente norte” sirve de nexo de unión entre los dispositivos “rápidos”. Incorpora el controlador de memoria, la interfaz con el procesador y el controlador gráfico. A veces incluso incorpora el propio procesador gráfico. El fabricante Intel lo suele denominar al chip MCH ó GMCH. El ”puente sur” sirve de nexo de conexión a los dispositivos “lentos”, generalmente dispositivos de E/S. Tiene soporte para EIDE, Serial ATA, USB, DMA, IRQ, ..., integra bus PCI, audio y moden, ... El fabricante Intel lo suele denominar ICH. • • Memorias DDR SDRAM • • • • • Evolución natural de las SDRAM: simplemente aprovechan también los flancos de bajada de la señal de reloj para doblar frecuencia de funcionamiento y ancho de banda se envían dos datos por cada señal de reloj. Ejemplo: una DDR 266 es básicamente una PC133 (última SDRAM fabricada) con señales CK y CK#. Se añaden algunas nuevas señales y se quitan otras. Como por cada ciclo de reloj se pueden recoger (leer) ó enviar (escribir) dos datos, es preciso añadir circuitería extra (ver diagrama de bloques). Subir los MHz físicos es más difícil (y caro) de fabricación de su éxito. Varias familias en función de su frecuencia virtual: DDR1 (200mhz – 400mhz), DDR2 (400mhz – 667mhz), DDR3 (a partir de 800mhz).