Electrónica Digital - Ing. Telecomunicación

Anuncio

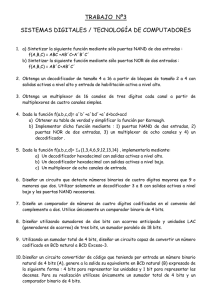

INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL PRACTICA Nº2: DISEÑO Y SIMULACIÓN DE SISTEMAS DIGITALES CON DISPOSITIVOS PROGRAMABLES El objetivo de esta práctica es ilustrar las técnicas actuales de diseño y simulación de sistemas digitales, haciendo uso de una herramienta para la síntesis de sistemas digitales sobre FPGAs y una placa de evaluación. Sesión 2.1: introducción al uso del paquete MAX+plus II para el diseño y simulación de sistemas digitales; diseño y simulación de un codificador de binario a BCD y un decodificador de BCD para su uso con un display de 7 segmentos. Sesión 2.2: diseño y simulación de circuitos aritméticos. Sesión 2.3: implementación con FPGAs sobre una placa de evaluación de circuitos aritméticos. Sesión 2.4: diseño y simulación de un contador de segundos e implementación con FPGAs sobre una placa de evaluación. Sesión 2.5: introducción a VHDL; diseño y simulación de una máquina de estados finitos e implementación sobre una placa de evaluación. SESIÓN 2.1: Introducción a MAX+plus II Instrumental de laboratorio: • Software de diseño de sistemas digitales MAX+plus II 2.1.1. MAX+plus II MAX+plus II es un paquete para del desarrollo de sistemas digitales sobre dispositivos lógicos programables, permitiendo el diseño, simulación, síntesis y generación de los ficheros de configuración para una aplicación específica. Esta herramienta permite el diseño jerárquico con diferentes posibilidades de descripción del sistema: diseño con esquemáticos, lenguajes de descripción de hardware, etc., disponiendo de diferentes 2.1 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL tipos de primitivas (puertas lógicas individuales, componentes de las familias 74, módulos LPM, etc.); por otra parte, la herramienta incluye un simulador que permite la verificación del diseño teniendo en cuenta las especificaciones temporales del dispositivo objetivo. CREACIÓN DE UN PROYECTO El diseño con MAX+plus II está basado en la creación de un proyecto. Para ello no es necesario más que crear un fichero de diseño (esquemáticos, .gdf, o de texto para el uso de algún lenguaje de descripción de hardware) en la carpeta deseada y utilizar el botón de la barra de herramientas, que crea un proyecto correspondiente a dicho fichero o abre el proyecto si éste ya existe. Una vez creado el proyecto e iniciado el diseño con esquemáticos, es posible insertar diferentes elementos con el comando “Symbol − Enter Symbol” del menú, o también desplegando el menú de contexto (botón derecho) en el editor gráfico de esquemáticos o haciendo doble click sobre el fondo del diseño; esta acción despliega la ventana de selección de componente, reflejada en la figura 2.1, ventana en la que aparecerán varias librerías de elementos disponibles: • los símbolos asociados al proyecto en curso, según el procedimiento que se verá a continuación; • c:\maxplus2\max2lib\prim, que contiene puertas lógicas individuales de varios Figura 2.1: selección de símbolos a insertar. 2.2 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL tipos, diferentes tipos de biestables, elementos de entrada y salida, etc., y será la que se empleará básicamente en esta práctica; • c:\maxplus2\max2lib\mf, que contiene macrofunciones que implementan los diferentes circuitos integrados de las familias 74 de componentes digitales discretos; • c:\maxplus2\max2lib\mega_lpm, que contiene diferentes módulos parametrizables (multiplexores, circuitos aritméticos, registros, etc.); • c:\maxplus2\max2lib\edif, con elementos similares a los de la librería c:\maxplus2\max2lib\mf. Dentro de la librería c:\maxplus2\max2lib\prim, además de las diferentes puertas lógicas, los elementos más destacados para el desarrollo de estas prácticas son: • input y output, que permiten definir entradas y salidas individuales para el circuito descrito en cada fichero .gdf; • diferentes biestables, con y sin señal de ENABLE: dff, dffe, jkff, jkffe, srff, srffe, tff ó tffe. La figura 2.2 muestra un ejemplo de cómo se puede introducir un determinado circuito lógico en el editor gráfico. Obsérvese que al situarse en la ventana del editor gráfico, Figura 2.2: ejemplo de diseño con MAX+plus II. 2.3 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL Figura 2.3: ejemplo de diseño jerárquico con MAX+plus II. en la parte derecha de MAX+plus II Manager aparece una barra de herramientas adecuada, al tiempo que para conectar los diferentes elementos del circuito, sólo hay que arrastrar el ratón sobre sus terminales, cambiando éste a una cruz y siendo posible realizar la conexión sin más que arrastrar el ratón hasta el punto deseado. DISEÑO JERÁRQUICO MAX+plus II permite el diseño jerárquico, es decir, emplear en un proyecto determinados bloques del mismo como elementos constitutivos de otros bloques del proyecto. Para ello, dado un determinado bloque, como el mostrado en la figura 2.2, es posible utilizarlo como componente de otros circuitos más complejos creando el símbolo adecuado; para ello sólo hay que usar el comando “File − Create Default Symbol”, que creará el fichero .sym correspondiente. Dicho símbolo puede editarse con el comando “File − Edit Symbol” y queda incluido en la librería de trabajo del proyecto en curso. De este modo, es posible emplear los símbolos creados en un nuevo diseño, como muestra la figura 2.3. En general, cuando se esté realizando un diseño jerárquico, el nombre del proyecto deberá corresponder al nombre del fichero que corresponde al nivel máximo de dicha jerarquía que, además, se abrirá empleando el botón de la barra de herramientas. COMPILACIÓN Y SIMULACIÓN Una vez que el diseño incluido en un proyecto está finalizado, MAX+plus II permite la simulación del mismo y su compilación y síntesis para su uso sobre un dispositivo 2.4 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL Figura 2.4: aspecto típico de la ventana del compilador de MAX+plus II. lógico programable. En las siguientes sesiones se especificarán los parámetros a definir para la correcta implementación hardware del diseño, a través del menú “Assign” y sus diferentes posibilidades. En cualquier caso, la síntesis del proyecto se realiza a través del compilador, que puede abrirse con el botón de la barra de herramientas o a través del menú “MAX+plus II”; también puede iniciarse con los o botones , que guardan y comprueban (conexionado, sintaxis, etc.) y guardan y compilan, respectivamente, el proyecto. La figura 2.4 muestra el aspecto típico de la ventana del compilador y los mensajes correspondientes. Dada la transparencia para el usuario de MAX+plus II, el proceso de compilación, que se inicia con el botón “Start”, realiza de manera automática todos los pasos implicados en el mismo: • extracción de los nodos del circuito y creación de una base de datos de los mismos; • síntesis de la lógica necesaria para la creación del diseño utilizando las primitivas de diseño disponibles en la familia de dispositivos objetivo; • emplazamiento del diseño en el chip concreto objetivo y enrutado de las conexiones entre los diferentes módulos; • extracción de las características temporales del circuito final para su simulación; 2.5 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL Figura 2.5: elección de las señales a mostrar en la simulación. • creación de los ficheros de programación necesarios para el volcado del diseño en el chip objetivo. En caso de producirse algún error durante la compilación, en la ventana de mensajes del compilador se mostrarán las causas del mismo y la etapa de compilación en la que se produjo el error. Una vez que el proyecto ha sido compilado con éxito, es posible simular el mismo creando un fichero .scf (Waveform Editor File) adecuado; dicho fichero habrá de llevar el nombre del proyecto a simular y podrá modificarse con el módulo Waveform Editor, que se inicia a través del menú “MAX+plus II” o al abrir algún fichero .scf. Una vez iniciado el Waveform Editor, podemos insertar en el mismo las diferentes señales del circuito a visualizar, a través del comando “Node − Insert nodes from SNF”, que inicia la ventana de la figura 2.5 en la que es posible buscar en la base de datos de nodos del diseño las señales a insertar, tanto entradas como salidas, grupos de señales, salidas de registros, etc. Antes de iniciar la definición de las entradas para la simulación, es necesario fijar la duración de la misma con el comando “File − End Figura 2.6: simulación con MAX+plus II. 2.6 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL time”; posteriormente, se podrán definir las diferentes entradas a través de las diferentes opciones del comando “Edit − Overwrite”. Tras definir las entradas convenientemente y seleccionar las salidas a mostrar en el fichero .scf, no hay más que proceder a la simulación, bien iniciando el simulador con el botón , a través del menú “MAX+plus II” o con el botón , que guarda y simula el proyecto actual. Una vez realizada la simulación, se podrá comprobar el correcto funcionamiento del diseño. La figura 2.6 muestra los resultados de simulación para el circuito de la figura 2.3. FAMILIARIZACIÓN CON MAX+plus II Antes de proceder con el resto de las tareas de esta primera sesión, es conveniente familiarizarse con el paquete MAX+plus II comprobando el efecto de lo expuesto hasta ahora. 2.1.2. Codificador de binario a BCD OBJETIVO Creación de un módulo codificador de binario a BCD que pueda emplearse como bloque constitutivo en diseños posteriores. PROCEDIMIENTO Como primera tarea a realizar con MAX+plus II, se diseñará un módulo codificador de binario a BCD que se empleará en sesiones posteriores para la implementación de otros sistemas más complejos. En concreto, las especificaciones del sistema son las siguientes: • el codificador ha de tener cuatro entradas, que representan un número en binario natural, y cuatro salidas, que corresponden a la representación en BCD de la entrada; • para entradas que no representen números decimales la salida ha de ser 0000. 2.7 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL El procedimiento a seguir es el siguiente: • diseñar el circuito empleando un esquemático en un fichero .gdf, a partir de las primitivas de la librería c:\maxplus2\max2lib\prim, y crear un proyecto con dicho fichero; • crear un fichero .scf en el que se visualicen las entradas y salidas del codificador BCD, configurando las entradas convenientemente para comprobar todas las posibilidades de la tabla verdad (para ello podrá usarse el comando “Edit − Overwrite − Clock” utilizando como multiplicador diferentes potencias de dos); • simular el diseño y comprobar el correcto funcionamiento del mismo (para facilitar la comprobación usar el comando “Node − Enter group” tras seleccionar un grupo de señales a agrupar, tomando la precaución de colocar las más significativas en la parte superior); • crear un símbolo para el codificador y guardar los ficheros .gdf y .sym para su uso en sesiones posteriores. CUESTIONES 1. Utilizando el Waveform Editor tras la simulación, estime el retardo que existe en el circuito diseñado entre un cambio en las entradas y el cambio correspondiente en las salidas. 2.1.3. Decodificador de BCD a 7 segmentos OBJETIVO Creación de un módulo decodificador de BCD para su uso con displays de 7 segmentos que pueda emplearse como bloque constitutivo en diseños posteriores. 2.8 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL PROCEDIMIENTO Para finalizar la sesión se diseñará un módulo decodificador de BCD para su uso con displays de 7 segmentos que se empleará en sesiones posteriores para la implementación de otros sistemas más complejos. En concreto, las especificaciones del sistema son las siguientes: • el decodificador ha de seguir la nomenclatura estándar para los displays de 7 segmentos que se muestra en la figura 2.7; • en el diseño se supondrá que cada segmento se ilumina cuando se le Figura 2.7: display de 7 segmentos. asigna un 0 lógico, permaneciendo apagado mientras se le asigne un 1 lógico. El procedimiento a seguir es el siguiente: • diseñar el circuito empleando un esquemático en un fichero .gdf, a partir de las primitivas de la librería c:\maxplus2\max2lib\prim, y crear un proyecto con dicho fichero; • crear un fichero .scf en el que se visualicen las entradas y salidas del decodificador BCD, configurando las entradas convenientemente para comprobar todas las posibilidades de la tabla verdad; • simular el diseño y comprobar el correcto funcionamiento del mismo; • crear un símbolo para el decodificador de BCD a 7 segmentos y guardar los ficheros .gdf y .sym para su uso en sesiones posteriores. 2.9 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL CUESTIONES 1. Utilizando el Waveform Editor tras la simulación, estime el retardo que existe en el circuito diseñado entre un cambio en las entradas y el cambio correspondiente en las salidas. 2. Estime el cambio en coste del circuito si los segmentos hubiesen de iluminarse con un 1 lógico en lugar de un 0 lógico. 2.10 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL SESIÓN 2.2: Diseño y simulación de circuitos aritméticos (I) Instrumental de laboratorio: • Software de diseño de sistemas digitales MAX+plus II OBJETIVO En esta sesión se construirán, de manera jerárquica, diferentes circuitos aritméticos. Para ello, los módulos que se vayan diseñando irán formando los bloques constitutivos de los siguientes, haciendo uso también de algunos módulos diseñados en la sesión anterior. Todos los circuitos serán verificados mediante su simulación. Finalmente, el diseño total se trasladará a la placa de evaluación Altera Design Laboratory Package UP1 en la siguiente sesión. 2.2.1. Sumador completo de un bit OBJETIVO Diseñar un módulo sumador completo de un bit que pueda emplearse para la construcción de sumadores de mayor precisión. PROCEDIMIENTO El sumador completo de un bit es un módulo con tres entradas (los dos bits a sumar, x e y, y el bit de acarreo de entrada, cin) y dos bits de salida (el bit de suma, s, y el bit de acarreo de salida, cout); las salidas están definidas por las siguientes funciones de conmutación: s=x⊕y⊕cin cout=xy+xcin+ycin (2.1) El procedimiento a seguir es el siguiente: • diseñar el circuito empleando un esquemático en un fichero .gdf, a partir de las primitivas de la librería c:\maxplus2\max2lib\prim, y crear un proyecto con dicho fichero; 2.11 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL • crear un fichero .scf en el que se visualicen las entradas y salidas del sumador completo, configurando las entradas convenientemente para comprobar todas las posibilidades de la tabla verdad; • simular el diseño y comprobar el correcto funcionamiento del mismo; • crear un símbolo para el sumador completo de un bit y guardar los ficheros .gdf y .sym para su uso posterior en la sesión. 2.2.2. Sumador de 4 bits OBJETIVO Diseñar, a partir del sumador completo anterior, un sumador de 4 bits para su uso en un sumador BCD de una cifra. PROCEDIMIENTO A partir del sumador completo de un bit definido anteriormente se creará un sumador de 4 bits, tal y como muestra la figura 2.8. Para ello, el procedimiento a seguir es: • crear un nuevo esquemático en un fichero .gdf y guardarlo en la misma carpeta que el proyecto anterior, asignando el proyecto actual al nuevo fichero Figura 2.8: sumador de 4 bits. 2.12 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL Figura 2.9: ejemplo de simulación del sumador de 4 bits. con el botón de la barra de herramientas; • diseñar el sumador de 4 bits a partir del símbolo anteriormente creado, que debe aparecer en la librería de trabajo del proyecto actual del cuadro de diálogo “Enter Symbol”, tal y como muestra la figura 2.1; • crear un fichero .scf en el que se visualicen las entradas y salidas del sumador de 4 bits y, usando el comando “Node − Enter group” para mayor comodidad, introducir diferentes combinaciones de entradas y comprobar en la simulación la validez de los resultados, como se ilustra en la figura 2.9; • crear un símbolo para el sumador de 4 bits y guardar los ficheros .gdf y .sym para su uso posterior en la sesión. CUESTIONES 1. Utilizando el Waveform Editor tras la simulación, estime el retardo que existe en el sumador de 4 bits entre un cambio en las entradas y el cambio correspondiente en las salidas. 2.2.3. Sumador BCD de un dígito OBJETIVO Creación de un sumador decimal de un dígito a partir de los módulos definidos. 2.13 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL PROCEDIMIENTO A partir del sumador de 4 bits definido anteriormente, ha de diseñarse un sumador BCD de un dígito, es decir, un sistema que satisfaga las especificaciones siguientes: • dos entradas de 4 bits, que representan los dos dígitos decimales codificados en BCD a sumar, y una entrada de 1 bit que represente el posible acarreo de entrada de la suma; • una salida de 4 bits que corresponda al dígito decimal codificado en BCD resultado de la suma de las entradas y una salida de 1 bit que represente el posible acarreo de salida de la suma. Para diseñar el circuito se seguirá una estructura puramente combinacional que ha de incluir los siguientes módulos: • un primer sumador de 4 bits que realice la suma de las dos entradas BCD y el posible acarreo de entrada; • un segundo sumador de 4 bits que implemente la suma del resultado del sumador anterior con 6 (0110), proporcionando el resultado correcto de la suma en BCD si el primer resultado no lo era; • un módulo que determine si el resultado del primer sumador de 4 bits es una cifra decimal correcta (nótese que el resultado de este primer sumador es incorrecto en BCD si los 4 bits de suma son, en binario, mayores que 9 o si el acarreo de salida de dicho sumador es 1); • finalmente, un multiplexor con dos entradas de 4 bits que, en función de la salida del módulo comparador anterior, seleccione entre las salidas de los dos sumadores de 4 bits. Es evidente que para la implementación de este sumador BCD según lo expuesto, es posible usar sin más el sumador de 4 bits anteriormente definido como bloque básico, siendo sólo necesario el diseño del multiplexor de 2 a 1 para palabras de 4 bits y el módulo comparador que genere la señal de control de dicho multiplexor; estos módulos se diseñarán siguiendo el procedimiento ya descrito para el diseño del 2.14 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL sumador completo o el sumador de 4 bits. Una vez que todos los módulos hayan sido definidos: • crear un nuevo esquemático en un fichero .gdf y guardarlo en la misma carpeta que los proyectos anteriores, asignando el proyecto actual al nuevo fichero con el botón de la barra de herramientas; • diseñar el sumador BCD de un dígito a partir de los símbolos del sumador de 4 bits, multiplexor y comparador definidos; • crear un fichero .scf en el que se visualicen las entradas y salidas del sumador BCD e introducir diferentes combinaciones de entradas a fin de comprobar en la simulación la validez de los resultados, tal y como se hizo para el sumador de 4 bits. 2.15 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL 2.16 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL SESIÓN 2.3: Diseño y simulación de circuitos aritméticos (II) Instrumental de laboratorio: • Software de diseño de sistemas digitales MAX+plus II • Placa de evaluación Altera Design Laboratory Packager UP1 y accesorios OBJETIVO En esta sesión se trasladará el sumador BCD de un dígito desarrollado en la sesión anterior a la placa de evaluación Altera Design Laboratory Package UP1 para su implementación sobre FPGAs. DESIGN LABORATORY PACKAGE UP1 La placa de evaluación Altera Design Laboratory Package UP1, que se muestra en la figura 2.10, es una placa para el prototipado de sistemas digitales que incluye dos FPGAs: una de la familia MAX7000 y otra de la familia FLEX10K, ambas fabricadas por Altera. El sistema permite configurar ambos chips por separado a través del puerto paralelo de un PC desde MAX+plus II, o bien a través de otra placa UP1. Los chips disponibles en la placa UP1, tal y como corresponde a las FPGAs, son completamente programables, pudiendo alterarse el circuito digital que contienen sin más que rescribir en ellos la configuración adecuada; además, al cesar la alimentación de la placa, la configuración de ambos chips se pierde al estar basados en tecnología SRAM. Ambos chips cuentan con gran números de pines de E/S, que en su mayoría están disponibles para su conexionado externo a través de los conectores de expansión. Los pines no disponibles se hayan conectados a los recursos disponibles en la placa, que incluyen displays de 7 segmentos, pulsadores, conmutadores para fijar valores lógicos, una señal de reloj de 25.175 MHz o LEDs para comprobar diferentes valores lógicos. Para el desarrollo de estas prácticas se hará uso del chip de la familia FLEX10K, situado en la mitad derecha de la placa UP1 y al que se hayan conectados: • 2 pulsadores (FLEX_PB1 y FLEX_PB2 en la figura 2.10, conectados a los pines 28 y 29 del dispositivo, respectivamente); 2.17 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL Figura 2.10: Altera Design Laboratory Package UP1. • 8 conmutadores (FLEX_SWITCH en la figura 2.10, la asignación de pines es la de la tabla 2.1); • 2 displays de 7 segmentos con punto decimal (FLEX_DIGIT en la figura 2.10, la asignación de pines es la de la tabla 2.2 siguiendo la nomenclatura de la figura 2.7). De esta manera, para poder implementar sobre este chip un determinado diseño sólo habrá que seguir las instrucciones de configuración del proyecto que se darán a 2.18 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL Conmutador Pin FLEX_SWITCH-1 41 FLEX_SWITCH-2 40 FLEX_SWITCH-3 39 FLEX_SWITCH-4 38 FLEX_SWITCH-5 36 FLEX_SWITCH-6 35 FLEX_SWITCH-7 34 FLEX_SWITCH-8 33 Tabla 2.1: asignación de pines para FLEX_SWITCH. Segmento Pin Dígito 1 (izqda.) Dígito 2 (dcha.) a 6 17 b 7 18 c 8 19 d 9 20 e 11 21 f 12 23 g 13 24 Punto decimal 14 25 Tabla 2.2: asignación de pines para FLEX_DIGIT. continuación, eligiendo el dispositivo adecuado y asignado las diferentes entradas y salidas a los pines deseados. CONFIGURACIÓN DE UN PROYECTO Como ya se comentó en la descripción de MAX+plus II realizada en la documentación de la sesión anterior, el menú “Assign” de MAX+plus II Manager permite la Figura 2.11: selección de dispositivo. 2.19 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL Figura 2.12: asignación de pines. configuración avanzada de los aspectos hardware de un determinado proyecto. Para el desarrollo de estas prácticas sólo es necesario configurar correctamente el dispositivo objetivo del diseño y la asignación de las entradas y salidas del diseño a los pines del dispositivo deseados. En lo que se refiere a la elección del dispositivo, el comando “Assign − Device” abre el cuadro de diálogo para la selección de dispositivo que se muestra en la figura 2.11, donde se podrá elegir la familia y el dispositivo concreto para el que se va a sintetizar el diseño. Para la asignación de pines a entradas y salidas del diseño habrá de usarse el comando “Assign − Pin/Location/Chip...”, que abre el cuadro de diálogo que se ilustra en la figura 2.12. En dicho cuadro de diálogo se puede asignar cada nodo de entrada o salida a un pin concreto del dispositivo objetivo del diseño. Figura 2.13: programador de MAX+plus II. 2.20 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL PROGRAMACIÓN DE UN DISPOSITIVO Una vez que un determinado proyecto ha sido correctamente compilado con las asignaciones definitivas de dispositivos y pines, MAX+plus II permite la programación del dispositivo a través del módulo Programmer, que se inicia con el botón de la barra de herramientas o a través del menú “MAX+plus II”. El aspecto de dicha ventana es el de la figura 2.13, en la que se puede comprobar que este módulo permite programar y configurar un dispositivo, comprobar su programación, etc. PROCEDIMIENTO En virtud de lo expuesto anteriormente, a continuación se trasladará el sumador BCD de un dígito diseñado en la sesión anterior a la placa Altera Design Laboratory Package UP1. Para ello se fijará a cero la entrada de acarreo del sumador anterior y se volverá a compilar el proyecto atendiendo a las siguientes restricciones: • el sumador se trasladará al dispositivo FLEX10K de la placa UP1, para lo que habrá que configurar el proyecto como se ha indicado anteriormente; • los dos dígitos BCD que sirven de entrada al sumador decimal de un dígito se conectarán a los conmutadores FLEX_SWITCH, con lo que dichas entradas del diseño habrán de ser asignadas según la asignación de la tabla 2.1. A fin de evitar que entradas no válidas en BCD lleguen al sumador, se insertará el codificador de binario a BCD diseñado en la sesión 2.1 entre las entradas del diseño y las del sumador BCD en sí; • el resultado de la suma se visualizará en los dos displays de 7 segmentos FLEX_DIGIT, con lo que habrá de usarse el decodificador de BCD a 7 segmentos diseñado en la sesión 2.1, asignando las salidas de dicho decodificador según la asignación de pines de la tabla 2.2. Una vez que al sumador BCD de un dígito le hayan sido añadidos los codificadores de binario a BCD y los decodificadores de BCD a 7 segmentos en la entrada y la salida, respectivamente, y las entradas y salidas hayan sido asignadas a los pines adecuados según lo anteriormente expuesto, se volverá a compilar el proyecto y con el fichero .sof 2.21 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL generado se procederá a programar el dispositivo FLEX10K de la placa UP1 para la comprobación del circuito. 2.22 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL SESIÓN 2.4: Diseño y simulación de circuitos secuenciales Instrumental de laboratorio: • Software de diseño de sistemas digitales MAX+plus II • Placa de evaluación Altera Design Laboratory Packager UP1 y accesorios OBJETIVO En esta sesión se diseñará, a partir de contadores de 2, 3 y 4 bits, un contador de segundos, que será verificado mediante simulación y se trasladará a la placa de evaluación Altera Design Laboratory Package UP1. FUNDAMENTO La placa UP1 (figura 2.10) incluye un oscilador de cristal que proporciona una señal de reloj de 25.175 MHz; dicha señal de reloj está disponible en el chip de la familia FLEX10K de la placa UP1 en el pin 91. Aprovechando dicha señal de reloj y utilizando sólo contadores de 2, 3 y 4 bits con biestables tipo D (primitiva dff de la librería c:\maxplus2\max2lib\prim), se pretende construir un contador de segundos, de modo que en los dos displays de 7 segmentos asociados al chip de la familia FLEX10K se visualice la cuenta de segundos. El biestable D disponible en la librería c:\maxplus2\max2lib\prim se muestra en la figura 2.14, y consta de dos entradas asíncronas activas en bajo: PRN y CLRN. La entrada PRN fija la salida Q al valor 1 lógico cuando se hace 0, mientras que CLRN fija la salida a 0 lógico si esta entrada se hace 0, permaneciendo inactivas mientras ambas permanezcan a 1 o no se conecten en el circuito. Por otra parte, el biestable se dispara por los flancos de Figura 2.14: biestable D dff. subida de la señal conectada a la entrada de reloj, copiándose en dicho flanco el valor de la entrada D a la salida Q, como corresponde a un biestable tipo D. Este biestable será el elemento básico de los contadores a diseñar: 2.23 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL • contador ascendente de 4 bits con señal de CLEAR (puesta a 0) global; • contador ascendente de 2 bits con señal de CLEAR (puesta a 0) global; • contador ascendente módulo 6 de 3 bits con señal de CLEAR (puesta a 0) global; • contador ascendente módulo 10 de 4 bits con señal de CLEAR (puesta a 0) global. Utilizando estos módulos como contadores básicos se pretende diseñar un contador de segundos, que constará de los siguientes bloques: • generador de una señal de reloj de 1 Hz de frecuencia a partir de la señal de reloj de 25.175 MHz disponible en la placa UP1; • contador decimal módulo 60, que puede construirse a partir de un contador módulo 10 que tenga como señal de reloj la señal generada de 1 Hz y un contador módulo 6 que obtenga su señal de reloj a partir de la salida del otro contador; • dos módulos decodificadores de BCD a 7 segmentos, diseñados en la sesión 2.1, que permitirán visualizar el estado de la cuenta en los displays de la placa UP1. PROCEDIMIENTO 2.4.1. Generación de un reloj de 1 Hz A partir de la señal de reloj de 25.175 MHz disponible en la placa UP1, en primer lugar se pretende generar una señal de reloj de 1 Hz. Para ello, no hay más que comprobar que 25.175·106/6·222≅1, con lo que un contador de 22 bits con señal de reloj de 25.175 MHz proporcionaría en su bit más significativo una frecuencia de 6 Hz. Dada la dificultad de generar un contador más de 22 bits, éste se construirá a partir de contadores más simples encadenados; en concreto, a partir de contadores de 4 y 2 2.24 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL bits, a los que se añadirá un contador de 3 bits módulo 6, que usen como entrada de reloj el bit más significativo del contador precedente y con uno de ellos teniendo como entrada de reloj la señal de 25.175 MHz es posible realizar esta operación. Para ello, se diseñarán dos contadores de 4 y 2 bits y un contador de 3 bits módulo 6: • diseñar los contadores en sendos ficheros .gdf, a partir de las primitivas de la librería c:\maxplus2\max2lib\prim; dichos módulos han de contar con una entrada de CLEAR, que se conectará a la entrada CLRN de los biestables dff, una entrada que será la señal de reloj de entrada y una única salida, el bit más significativo, que se usará como señal de reloj en el módulo siguiente al encadenarlos; • simular los diseños y comprobar el correcto funcionamiento de los mismos; • crear los símbolos correspondientes para los contadores y guardar los ficheros .gdf y .sym para su uso posterior en la sesión. Una vez disponibles estos módulos, diseñar un módulo que, haciendo uso de los contadores de 2 y 4 bits encadenados con un contador final de tres bits módulo 6, genere una señal de reloj de 1 Hz a partir de la señal de 25.175 MHz. Para ello: • diseñar el módulo en un fichero .gdf a partir de los símbolos de los contadores de 2 y 4 bits y el contador módulo 6; el módulo tendrá un entrada de CLEAR, conectada a la entrada correspondiente de todos los contadores, una entrada que corresponderá a la señal de reloj de la placa UP1, y una única salida, que será una señal de reloj de 1 Hz (la salida del contador de 3 bits módulo 6); • crear el símbolo correspondiente y guardar los ficheros .gdf y .sym para su uso posterior en la sesión. 2.4.2. Contador decimal de segundos Una vez que el módulo que genera una señal de reloj de 1 Hz está disponible, a continuación se diseñará un contador decimal de segundos módulo 60, a partir de dos contadores ascendentes en módulo 6 y módulo 10; el contador módulo 10 usará como 2.25 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL reloj la señal de 1 Hz, y habrá de generarse a partir de la salida de éste una señal de reloj para el contador módulo 6, de manera similar a lo hecho en la primera práctica (sesión 1.2) con el entrenador lógico DET 2020. Para ello: • diseñar el contador decimal de segundos en un fichero .gdf, a partir de las primitivas de la librería c:\maxplus2\max2lib\prim; dicho módulo habrá de contar con una entrada de CLEAR, que se conectará a la entrada CLRN de los biestables dff, una entrada de reloj, que será usada por el contador módulo 10, y 8 salidas correspondientes a los dos dígitos BCD que forman la cuenta decimal; • simular el contador decimal de segundos y comprobar el correcto funcionamiento del mismo; • crear el símbolo correspondiente y guardar los ficheros .gdf y .sym para su uso posterior en la sesión. 2.4.3. Implementación con FPGA Para la visualización del contador sobre la placa UP1, se creará un último proyecto en el que se incluirán los módulos anteriormente creados, con las siguientes consideraciones: • asignar el proyecto al chip de la familia FLEX10K disponible en la placa UP1, según lo descrito en la documentación de la sesión anterior (figura 2.11); • la entrada de reloj del módulo que genera la señal de reloj de 1 Hz habrá de asignarse, según el procedimiento descrito en la documentación de la sesión anterior (figura 2.12) al pin 91, en el que se halla disponible la señal de reloj de 25.175 MHz; • dado que todos los módulos generados cuentan con una señal de CLEAR, asignar a este nuevo proyecto una entrada de CLEAR global, que habrá de asignarse al pin 28, en el que está disponible la señal del pulsador FLEX_PB1 2.26 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL (figura 2.10), de modo que este pulsador pueda emplearse para poner a 0 el contador de segundos en cualquier momento; • conectar a la salida del módulo contador decimal de segundos dos módulos decodificadores de BCD a 7 segmentos, creados en la sesión anterior, y asignar las salidas de los mismos a los pines correspondientes a los displays de 7 segmentos, como recoge la tabla 2.2. Una vez realizado lo anterior, se volverá a compilar el proyecto y con el fichero .sof generado se procederá a programar el dispositivo FLEX10K de la placa UP1 para la comprobación del funcionamiento del contador de segundos. 2.27 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL 2.28 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL SESIÓN 2.5: Introducción a VHDL Instrumental de laboratorio: • Software de diseño de sistemas digitales MAX+plus II • Placa de evaluación Altera Design Laboratory Packager UP1 y accesorios OBJETIVO En esta sesión se comprobará como es posible definir un sistema digital utilizando el lenguaje de descripción de hardware VHDL. 2.5.1. VHDL (Very high speed Hardware Description Language) VHDL (Very high speed Hardware Description Language) es un lenguaje de descripción de hardware, preferentemente de sistemas digitales, aunque también se han desarrollado recientemente variantes analógicas. Una de las mayores ventajas de VHDL es que permite diferentes niveles de abstracción en la descripción de un circuito, siendo posibles dos tipos extremos de descripción: • descripciones estructurales (structural): equivalen a los esquemáticos creados en sesiones anteriores, en los que se enumeran los componentes del circuito y sus interconexiones, siendo labor del diseñador el definir la estructura del circuito a partir del comportamiento deseado; • descripciones completamente comportamentales (behavioral): en éstas se describe simplemente el comportamiento o funcionamiento del circuito, siendo posteriormente el compilador el que determine la estructura final del mismo que corresponda a dicho comportamiento. De este modo, VHDL se asemeja a los lenguajes de programación de alto nivel (C, Java, etc.), en los que el programador/diseñador define en una serie de sentencias un determinado comportamiento, siendo el compilador el que determina finalmente la secuencia de instrucciones que se proporcionan a un microprocesador, en el caso de software, o el circuito que sintetiza dicho comportamiento, en el caso de hardware. 2.29 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL La descripción de un circuito en VHDL ha de seguir unas ciertas pautas, que se ejemplifican a continuación: -- Electrónica Digital, Ing. Telecomunicación -- Ejemplo de VHDL -- Los comentarios se inician con “—-“ y alcanzan hasta el final de la línea LIBRARY ieee; USE ieee.std_logic_1164.ALL; USE ieee.std_logic_arith.ALL; ------------ -- En primer lugar se incluyen -- las librerías necesarias Cada fichero describe una entidad, que se indica con la palabra clave ENTITY y cuya declaración finaliza en END “nombre_entidad” La declaración incluyen dos partes: * GENERIC: declaración de constantes y parámetros de la entidad * PORT: lista de entradas y salidas de la entidad, indicando el tipo de cada una de ellas (pueden depender de los GENERIC) Entre los tipos básicos destacan * INTEGER: entero * STD_LOGIC: valor lógico estándar (bit) * STD_LOGIC_VECTOR: vector de valores lógicos, formado por bits muy útil en la definición de buses, etc. ENTITY ejemplo IS GENERIC ( ANCHO ); PORT ( in0 in1 output sel ); END ejemplo; : INTEGER := 16 : : : : IN IN OUT IN -- Ancho de palabra STD_LOGIC_VECTOR(ANCHO-1 downto 0); STD_LOGIC_VECTOR(ANCHO-1 downto 0); STD_LOGIC_VECTOR(ANCHO-1 downto 0); STD_LOGIC -- A cada entidad le corresponden una o varias arquitecturas (indicadas con la -- palabra clave ARCHITECTURE y delimitadas por BEGIN y -- END “nombre_arquitectura”) ARCHITECTURE circuito OF ejemplo IS -- Se pueden definir señales (SIGNAL) auxiliares, que básicamente -- corresponden a interconexiones en el circuito SIGNAL aux1 : STD_LOGIC_VECTOR(ANCHO-1 downto 0); SIGNAL aux2 : STD_LOGIC_VECTOR(ANCHO-1 downto 0); BEGIN ----- La arquitectura está formada por asignaciones en las que intervienen construcciones del tipo IF, FOR, WHILE, WHEN, etc., o por llamadas a otras entidades, como en este ejemplo para ilustrar un multiplexor de 2 a 1 para palabras de ANCHO bits aux1 <= in0 WHEN sel=’0’ ELSE in1; mux1 : multiplexor GENERIC MAP PORT MAP -- Asignación de señales -- Llamada a “multiplexor” ( WIDTHDATA => ANCHO, WIDTHSEL => 1 ) ( data_0 => in0, data_1 => in1, data_out => aux2 ); END circuito; 2.30 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL Nótese que al crear un fichero de texto en MAX+plus II Manager (Text Editor File) y guardar éste con extensión .vhd (VHDL), el texto adquiere diferentes colores según la sintaxis. Por otra parte, a través del comando “Template − VHDL Template...”, MAX+plus II ofrece construcciones predefinidas de la mayoría de estructuras posibles en VHDL. Aparte de lo anteriormente expuesto, otra herramienta útil es el proceso. Un proceso en VHDL incluye una serie de sentencias que sólo “ocurren” cuando se produce un cambio en las señales que forman la lista de sensibilidad del proceso. El código siguiente ilustra el funcionamiento de un biestable tipo D: -- Electrónica Digital, Ing. Telecomunicación -- Ejemplo de proceso (biestable D) LIBRARY ieee; USE ieee.std_logic_1164.ALL; USE ieee.std_logic_arith.ALL; ENTITY biestableD IS PORT ( d : q : clk : ); END biestableD; IN OUT IN STD_LOGIC; STD_LOGIC; STD_LOGIC ARCHITECTURE proceso OF biestableD IS BEGIN proceso_biestableD : PROCESS (clk) BEGIN -- Lista de sensibilidad IF clk'event AND CLK='1' THEN q <= d; END IF; END PROCESS proceso_biestableD; -- Flanco de subida de clk -- La entrada D se copia en Q -- Fin del proceso END proceso; Figura 2.16: simulación de un biestable D definido en VHDL. 2.31 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL La figura 2.16 muestra la simulación del código VHDL anterior, siendo evidente el funcionamiento de la entidad biestableD como un biestable de tipo D, siendo clk la entrada de reloj y d la entrada de datos. CUESTIONES 1. ¿Cómo describiría en VHDL un multiplexor de 2 a 1 para señales de un bit? Como indicación, use asignaciones entre señales con el operador <= y use los operadores lógicos AND, OR y NOT. 2. Compruebe, mediante simulación, el funcionamiento correcto de dicho multiplexor. 2.5.2. Máquina de estados finitos OBJETIVO Diseñar una máquina de estados finitos utilizando biestables D definidos en VHDL. PROCEDIMIENTO 2.5.2.1. Definición de un biestable tipo D con CLEAR asíncrono A partir del código anterior que recoge un biestable tipo D, habrá de definirse un nuevo biestable tipo D con una señal de CLEAR asíncrono activa en bajo. El procedimiento a seguir es: • crear un fichero de texto y guardarlo con extensión .vhd; copiar el código anterior en el que se define un biestable tipo D y modificarlo para añadir una entrada de CLEAR asíncrona activa en bajo, es decir, una señal que haga Q=0 en cualquier momento, independientemente de la señal de reloj y del valor de D. • crear un nuevo proyecto con dicho fichero, simular el biestable definido y comprobar el correcto funcionamiento del mismo; 2.32 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL 1 A,00 0 1 C,10 1 0 B,01 0 Figura 2.15: diagrama de estados. • crear un símbolos para el nuevo biestable definido y guardar los ficheros .vhd y .sym para su uso posterior en la sesión. 2.5.2.2. Diseño de la máquina de estados Una vez que se ha definido el nuevo biestable tipo D y su símbolo correspondiente ha sido generado, éste se va a usar en el diseño de un sistema secuencial síncrono que sintetice la máquina de estados descrita en la figura 2.15: • el circuito cuenta con dos salidas que están asociadas al estado, de modo que en el estado A la salida es 00, en el estado B es 01 y en el estado C es 10; • el sistema ha de contar con una entrada de CLEAR asíncrono que devuelva el circuito al estado A. Una vez definida la estructura del circuito: • dibujar el circuito en un fichero .gdf, a partir de las primitivas de la librería c:\maxplus2\max2lib\prim; • simular el circuito y comprobar el correcto funcionamiento del mismo; 2.33 INGENIERIA DE TELECOMUNICACION ELECTRONICA DIGITAL • crear el símbolo correspondiente y guardar los ficheros .gdf y .sym para su uso posterior en la sesión. 2.3.2.2. Implementación con FPGA Tras la creación del módulo anterior que sintetiza la máquina de estados de la figura 2.15, se procederá a crear un nuevo proyecto para el dispositivo de la familia FLEX10K de la placa UP1, proyecto en el que se incluirán los siguientes módulos: • el módulo diseñado en la sesión 2.4 que genera un reloj de 1 Hz a partir del reloj de 25.175 MHz disponible en la placa UP1, a fin de comprobar en una escala de tiempos razonable el funcionamiento de la máquina de estados; de este modo, la entrada de este módulo habrá de asignarse al pin 91, en el que se halla disponible la señal de reloj de 25.175 MHz, y su salida se usará como reloj para el módulo definido anteriormente que realiza la máquina de estados; • el módulo definido anteriormente que realiza la máquina de estados, tomando como entrada de reloj la salida del módulo para generar un reloj de 1 Hz y asignando la entrada de la máquina de estados al pin 41 del dispositivo, que está conectado al conmutador FLEX_SWITCH-1, como indica la tabla 2.1, y la entrada de CLEAR asíncrono al pin 33 que corresponde al conmutador FLEX_SWITCH-3; • el módulo decodificador de BCD a 7 segmentos usado ya en diferentes ocasiones, que se empleará para visualizar la salida (y por tanto, el estado) de la máquina de estados en uno de los displays de 7 segmentos disponibles; por tanto, la salida de la máquina de estados se usará como entrada de este módulo, y sus salidas habrán de conectarse según la asignación de pines de la tabla 2.2. Una vez realizado lo anterior, se compilará este nuevo proyecto y con el fichero .sof generado se procederá a programar el dispositivo FLEX10K de la placa UP1 para la comprobación del funcionamiento de la máquina de estados, usando como entradas los conmutadores FLEX_SWITCH asignados en la compilación y visualizando su salida en el display de 7 segmentos. 2.34