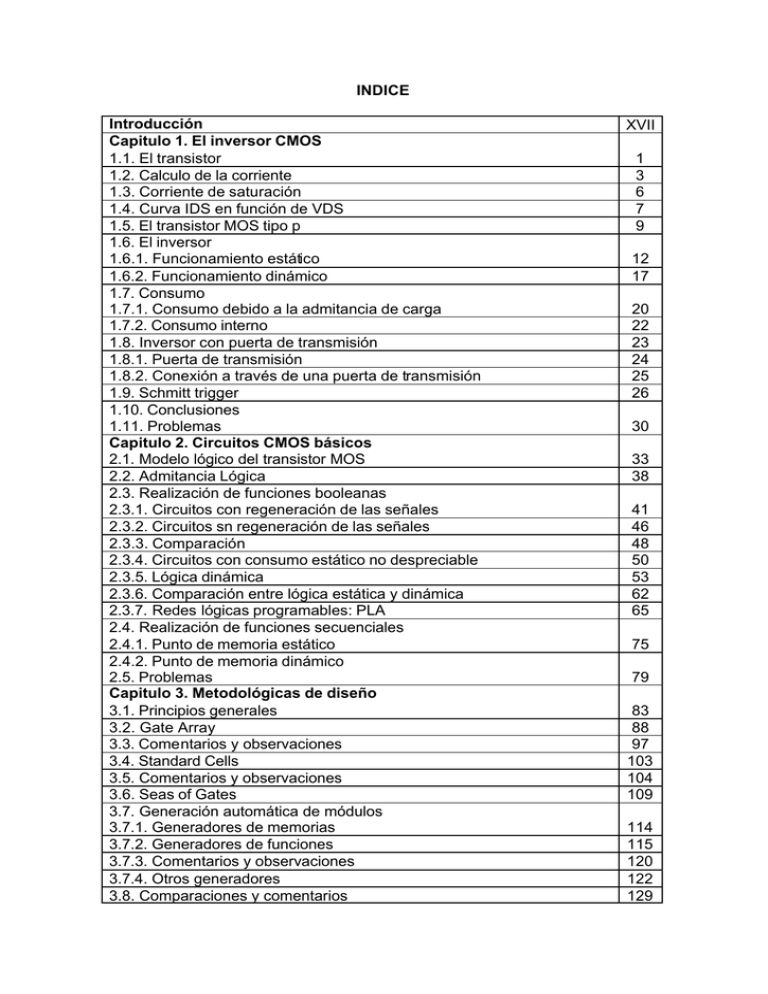

INDICE Introducción XVII Capitulo 1. El inversor CMOS 1.1

Anuncio

INDICE Introducción Capitulo 1. El inversor CMOS 1.1. El transistor 1.2. Calculo de la corriente 1.3. Corriente de saturación 1.4. Curva IDS en función de VDS 1.5. El transistor MOS tipo p 1.6. El inversor 1.6.1. Funcionamiento estático 1.6.2. Funcionamiento dinámico 1.7. Consumo 1.7.1. Consumo debido a la admitancia de carga 1.7.2. Consumo interno 1.8. Inversor con puerta de transmisión 1.8.1. Puerta de transmisión 1.8.2. Conexión a través de una puerta de transmisión 1.9. Schmitt trigger 1.10. Conclusiones 1.11. Problemas Capitulo 2. Circuitos CMOS básicos 2.1. Modelo lógico del transistor MOS 2.2. Admitancia Lógica 2.3. Realización de funciones booleanas 2.3.1. Circuitos con regeneración de las señales 2.3.2. Circuitos sn regeneración de las señales 2.3.3. Comparación 2.3.4. Circuitos con consumo estático no despreciable 2.3.5. Lógica dinámica 2.3.6. Comparación entre lógica estática y dinámica 2.3.7. Redes lógicas programables: PLA 2.4. Realización de funciones secuenciales 2.4.1. Punto de memoria estático 2.4.2. Punto de memoria dinámico 2.5. Problemas Capitulo 3. Metodológicas de diseño 3.1. Principios generales 3.2. Gate Array 3.3. Comentarios y observaciones 3.4. Standard Cells 3.5. Comentarios y observaciones 3.6. Seas of Gates 3.7. Generación automática de módulos 3.7.1. Generadores de memorias 3.7.2. Generadores de funciones 3.7.3. Comentarios y observaciones 3.7.4. Otros generadores 3.8. Comparaciones y comentarios XVII 1 3 6 7 9 12 17 20 22 23 24 25 26 30 33 38 41 46 48 50 53 62 65 75 79 83 88 97 103 104 109 114 115 120 122 129 3.9. Problemas Capitulo 4. Diseño 4.1. Aspectos particulares 4.1.1. Maquinas secuenciales síncronas 4.1.2. Esquemas de reparto de la señal de reloj 4.1.3. Contadores 4.1.3.1. Contadores binarios síncronos 4.1.3.2. Contadores síncronos no binarios 4.1.3.3. Contadores asíncronos 4.1.4. Ideas de diseño 4.1.4.1. Temporizadores 4.1.4.2. Convertidor analógico-digital 4.1.4.3. Pilas 4.1.4.4. Metaestabilidad 4.2. Test de circuitos integrados 4.2.1. Máquina de test 4.2.2. Algunos conceptos importantes 4.2.3. Reglas de diseño 4.2.4. Técnicas de diseño especificas 4.2.4.1. Camino de análisis (scan path) 4.2.4.2. Test interno (Built In Self Test) 4.2.4.3. Descomposición en bloques 4.2.5. P roblemas relacionados con la máquina de test 4.2.6. Salidas conmutadas simultaneas 4.2.7. Test al nivel del circuito impreso 4.3. Método general y herramientas informáticas 4.3.1. Diseño lógico 4.3.1.1. Especificaciones técnicas 4.31.2. Definición del circuito 4.3.1.2.1. Lista de hilos 4.3.1.2.2. Lista de hilos jerárquica 4.3.1.2.3. Soft macros 4.3.1.2.4. Primitivas parametrizables 4.3.1.2.5. Construcciones del alto nivel 4.3.1.2.6. Síntesis lógica 4.3.1.2.7. Resumen 4.3.1.2.8. Depuración de la definición del circuito 4.3.1.3. Comunicación con el mundo eterno 4.3.1.4. Generación de los vectores de test 4.3.1.4.1. Definición de los vectores 4.3.1.4.2. Evaluación de los vectores 4.3.2. Trazado físico 4.3.3. Retroanotación 4.4. Problemas Capitulo 5. Dispositivos programables por el usuario 5.1. Arquitectura 5.2. Programación 5.2.1. Módulos programables simples 5.2.2. Maquinas de estado programables 131 135 136 140 144 154 158 162 166 175 178 180 182 189 190 192 198 200 203 208 212 215 217 222 224 226 231 238 241 259 261 265 267 268 275 278 280 5.3. Tecnologías 5.4. Ejemplos 5.5. Diseño 5.6. Comentarios 5.7. Problemas Capitulo 6. El lenguaje VHDL 6.1. Introducción 6.2. Un primer ejemplo 6.2.1. Arquitectura basad en la escritura 6.2.2. Biblioteca 6.2.3. Configuración 6.2.4. Resumen 6.2.5. Comentarios 6.2.6. Arquitectura basada en asignaciones de señales 6.2.7. Arquitectura basada en el comportamiento 6.2.8. Comentario 6.3. Un segundo ejemplo 6.3.1. Definición de un paquete 6.3.2. Multiplicador de N bits 6.3.3. Multiplicador de 8 bits 6.4. Análisis y simulación 6.5. Comentarios 6.6. Problemas Capitulo 7. Integrador de sistemas 7.1. Ejemplo introductivo 7.2. Secuencialización de las operaciones 7.3. Un primer ejemplo 7.2.2. Un segundo ejemplo 7.2.3. Máquinas algorítmicas 7.3. Circuitos “pipe line” 7.4. Unidad de proceso secuencializada 7.4.1. Ejemplo 7.4.2. Buses 7.4.3. Arquitectura de un bus 7.4.4. Arquitectura de 2 buses 7.5. Diferentes tipos de realización del control 7.5.1. Microprograma de control 7.5.2. Decodificadores de ordenes 7.5.3. Contador de programa 7.5.4. Subrutinas 7.5.5. Conclusión 7.6. Procesador “bit-slice” 7.7. Problemas Bibliografía Índice alfabético 282 286 297 299 301 303 304 306 307 308 309 311 312 313 314 315 318 319 326 329 330 334 335 338 342 345 350 353 355 360 361 362 364 366 369 371 372 376 383 383