Certamen 03 ELO311 Estructuras de Computadores I. Segundo

Anuncio

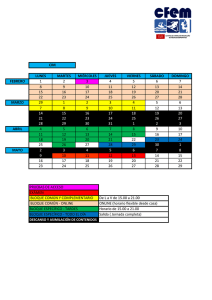

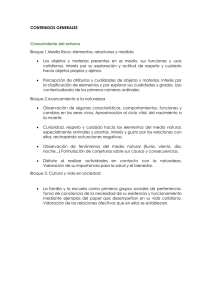

Certamen 03 ELO311 Estructuras de Computadores I. Segundo Semestre 2000. 1. Para un procesador pipeline(segmentado) con anticipación de operandos hacia la unidad aritmética y anticipación de datos para escribir en memoria; con bifurcaciones retardadas y saltos con descarte(con flushing); y con detenciones(stall). El arreglo de registros está construido con latchs transparentes. La señal equal se genera en el segmento de decodificación y lectura de registros. Las instrucciones de tipo R e inmediatas pasan por los cinco segmentos de la cañería. La memoria de datos está separada de la memoria de instrucciones. Determinar si existe o no conflicto(y de qué tipo) en la siguiente secuencia, fundamentando su respuesta. En caso de existir conflicto, indicar cómo y quién lo resuelve(el procesador o el compilador), para optimizar el comportamiento de la cañería. Si los conflictos se resuelven por anticipación de datos indicar el tipo de anticipación, indicando la unidad en que se encuentra el dato que se anticipa, y la unidad en que se introduce el dato anticipadamente. Si los conflictos se resuelven por detenciones, indicar la instrucción que se decodifica dos o más veces y la instrucción que se lee dos o más veces desde la memoria de instrucciones. add sw lw ori Solución. $t1, $t1, $t1 $t1, 0( $t1 ) $t1, 0( $t1) $t1, $t1, 0x1 add $t1, $t1, $t1 ;(1) sw $t1, 0($t1) ;(2) lw $t1, 0($t1) ;(3) ori $t1, $t1, 0x1 ;(4) ; (1) ; (2) ; (3) ; (4) M I M I tiempo M D R L R L M I M D M D R L M I R L M D orden de ejecución Anticipaciones hacia la unidad de operaciones(para leer el contenido del registro $t1): entre la (1) y (2); entre (1) y (3); y entre (3) y (4). Anticipación hacia la unidad de memoria(para leer el contenido del registro $t1): entre la (1) y (2) Estando la (1) en operaciones y la (2) en decodificación, se adelanta la salida de la alu hacia la entrada de la alu ( A = AluOut). Estando la (1) en memoria, la (2) en operaciones y la (3) en decodificación, se adelanta la salida de la memoria: hacia la entrada de la alu ( A = MOut) y hacia la entrada de la memoria(M = Mout) Soluciones Tercer Certamen. 1 Estando la (3) en operaciones y la (4) en decodificación, se detiene por un ciclo los segmentos de búsqueda y decodificación, y se invalida la órden de escritura en registros de la (4). Esto implica que la (4) se decodifica dos veces, y la (5) se busca dos veces en la memoria de instrucciones. Estando la (3) en memoria y la (4) en decodificación, se adelanta la salida de la memoria hacia la entrada de la alu ( A = MOut). La secuencia serealiza en 9 ciclos de reloj, dando un CPI promedio de 9/4. Debe notarse que un compilador que optimice el código, habría eliminado la instrucción lw, ya que ésta lee en $t1(desde la dirección efectiva en la memoria), el valor de $t1, que fue depositado en la misma dirección efectiva por la instrucción sw anterior. La instrucción sw no puede eliminarse, ya que se escribe en memoria, modificando el valor de la variable allí almacenada. add $t1, $t1, $t1 ;(1) sw $t1, 0($t1) ;(2) ori $t1, $t1, 0x1 ;(4) 1 2 M I R L M I 3 4 5 6 tiempo M D R L M I 7 M D R L M D orden de ejecución La secuencia se efectúa en 7 ciclos. El CPI promedio es 7/3. 2. Se tiene una memoria cache de datos de 128 Bytes de datos en total. Está organizada en forma asociativa por conjuntos de dos vías, empleándose la política de reemplazo del menos recientemente usado. El bloque está formado por dos palabras de 32 bits cada una. a) Determinar el número de bits necesarios para especificar los campos: offset de byte, offset de bloque, índice de la cache y marca. Se tiene que 128 Bytes son 128*8/32 = 32 Palabras de 32 bits. Y como cada bloque está formado por 2 palabras, se tienen 16 bloques en total. Y como se reparten en dos vías, se tendrá 8 bloques en cada vía; por lo tanto se requieren tres bits para especificar el índice de la cache. Basta un bit para especificar el offset del bloque. La marca se determina por diferencia: 32 - 3 - 1- 2 = 26 marca índice offset bloque offset byte 26 3 1 2 b) Determinar la cantidad de bits necesarios para almacenar todas las marcas y los bits de validez. Para las marcas se requieren: 26*8*2 = 416 bits. Para los bits de validez se requieren: 8*1*2 = 16 bits. Soluciones Tercer Certamen. 2 La organización puede representarse según el siguiente diagrama: # 0 1 2 3 4 5 6 7 3 V 1 1 marca ..00 ..01 dato 0 M[00] M[48] dato 1 M[04] M[4C] 1 ..00 M[28] M[2C] 1 1 .01 26 M[78] 32 M[7C] 32 # V 0 1 1 2 3 4 5 1 6 7 3 1 marca dato 0 dato 1 ..11 M[C8] M[CC] ..10 M[A8] M[AC] 32 32 26 En el cual se ilustran algunos bloques(de dos palabras) almacenados. c) Para una entrada válida, con marca igual a 0x2 e índice igual a 0x3, indicar las direcciones de los bytes almacenados en esa entrada. marca índice offset bloque offset byte Dirección Hex. ....00010 011 0 00 0.1001.1000 0x98 ....00010 011 0 01 0.1001.1001 0x99 ....00010 011 0 10 0.1001.1010 0x9A ....00010 011 0 11 0.1001.1011 0x9B ....00010 011 1 00 0.1001.1100 0x9C ....00010 011 1 01 0.1001.1101 0x9D ....00010 011 1 10 0.1001.1110 0x9E ....00010 011 1 11 0.1001.1111 0x9F d) Determinar en qué dirección de la cache se almacena el contenido de la dirección 0x1D8 y cual es el valor de la marca. Indicar las siguientes cuatro direcciones de palabras de memoria que deberían almacenarse en la misma dirección de la cache, dando el valor de las marcas respectivas. 0x1D8 = ...0000.0001.1101.1000 Corresponde índice 3. Marca 0x7. Bloque 0. La siguiente palabra, con igual índice está 4 bytes más adelante, resulta: 0x1DC = ...0000.0001.1101.1100 Corresponde índice 3. Marca 0x7. Bloque 1. La siguiente, se obtiene con bloque 0 y marca ...0001000, es decir: 0x218 = ...0000.0010.0001.1000 Corresponde índice 3. Marca 0x8. Bloque 0. La siguiente, se obtiene con bloque 1 y marca ...0001000, es decir: 0x21C = ...0000.0010.0001.1100 Corresponde índice 3. Marca 0x8. Bloque 1. La siguiente, se obtiene con bloque 0 y marca ...0001001, es decir: 0x258 = ...0000.0010.0101.1000 Corresponde índice 3. Marca 0x9. Bloque 0. e) Si el número de vías se aumenta a 4 y se desea que el campo marca sea de 20 bits y que el tamaño del bloque sea de 16 palabras de 32 bits cada una. Determinar el rango de direcciones para la cache, y el número total de bytes dedicados a datos. Soluciones Tercer Certamen. 3 marca + índice + offset bloque + offset byte = 32 offset byte = 2; 16 palabras implica: offset bloque = 4 20 + índice + 4 + 2 = 32; entonces índice = 6. Número de entradas de la cache = 2 6 = 64. Capacidad de la cache = 4(vías)* 64(entradas) * 16(palabras) * 32 bits = 4*64*16*4 Bytes = 16.384 Bytes sin considerar bits de marca y validez. Soluciones Tercer Certamen. 4