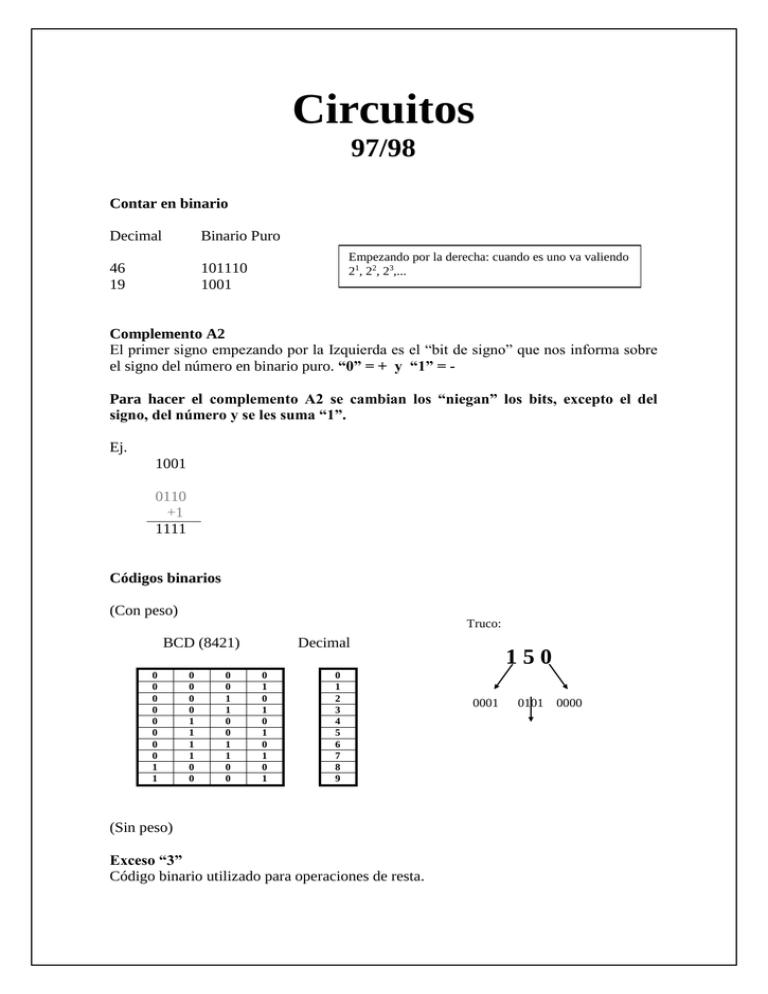

Circuitos 97/98

Anuncio