práctica 5

Anuncio

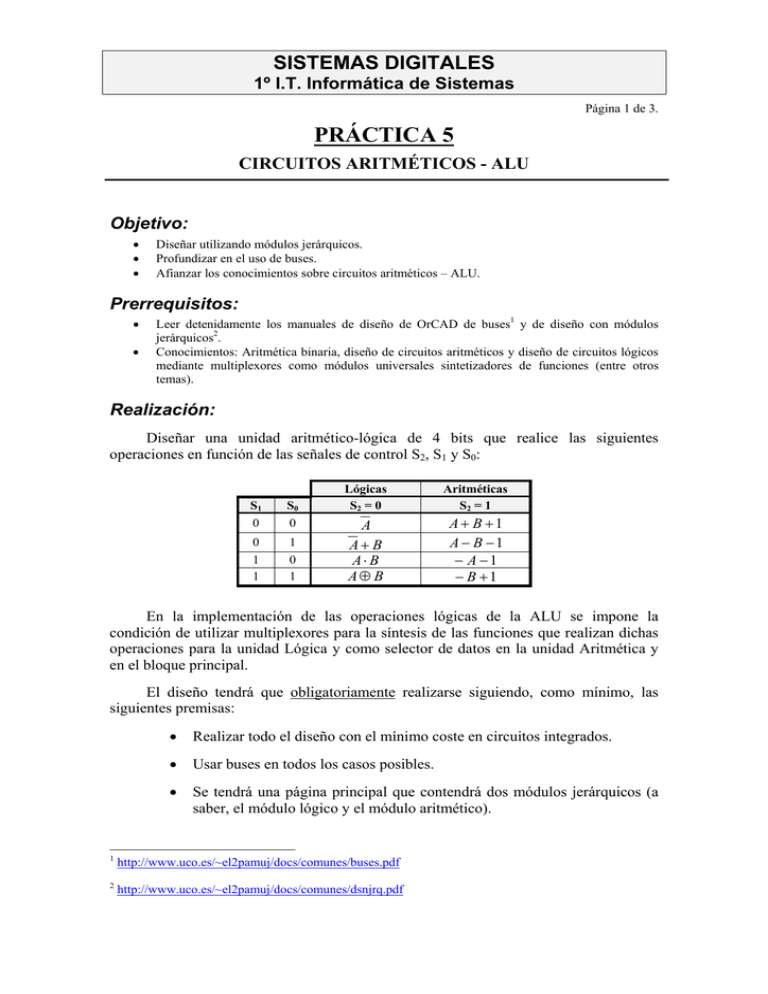

SISTEMAS DIGITALES 1º I.T. Informática de Sistemas Página 1 de 3. PRÁCTICA 5 CIRCUITOS ARITMÉTICOS - ALU Objetivo: • • • Diseñar utilizando módulos jerárquicos. Profundizar en el uso de buses. Afianzar los conocimientos sobre circuitos aritméticos – ALU. Prerrequisitos: • • Leer detenidamente los manuales de diseño de OrCAD de buses1 y de diseño con módulos jerárquicos2. Conocimientos: Aritmética binaria, diseño de circuitos aritméticos y diseño de circuitos lógicos mediante multiplexores como módulos universales sintetizadores de funciones (entre otros temas). Realización: Diseñar una unidad aritmético-lógica de 4 bits que realice las siguientes operaciones en función de las señales de control S2, S1 y S0: S1 S0 0 0 0 1 1 1 0 1 Lógicas S2 = 0 Aritméticas S2 = 1 A A+ B A⋅ B A⊕ B A + B +1 A − B −1 − A −1 − B +1 En la implementación de las operaciones lógicas de la ALU se impone la condición de utilizar multiplexores para la síntesis de las funciones que realizan dichas operaciones para la unidad Lógica y como selector de datos en la unidad Aritmética y en el bloque principal. El diseño tendrá que obligatoriamente realizarse siguiendo, como mínimo, las siguientes premisas: • Realizar todo el diseño con el mínimo coste en circuitos integrados. • Usar buses en todos los casos posibles. • Se tendrá una página principal que contendrá dos módulos jerárquicos (a saber, el módulo lógico y el módulo aritmético). 1 http://www.uco.es/~el2pamuj/docs/comunes/buses.pdf 2 http://www.uco.es/~el2pamuj/docs/comunes/dsnjrq.pdf SISTEMAS DIGITALES 1º I.T. Informática de Sistemas Página 2 de 3. PRÁCTICA 5 CIRCUITOS ARITMÉTICOS - ALU • El diseño del módulo lógico contendrá los módulos jerárquicos necesarios para cada uno de los bits. Cada uno de dichos módulos contendrá un multiplexor interconectado de manera que actúe como sintetizador universal de funciones. • Para el módulo aritmético se empleará el circuito integrado sumador completo de 4 bits 74LS83. Entradas/Salidas: • • • • • (Entrada) A[3:0]: Operando A. (Entrada) B[3:0]: Operando B. (Entrada) S[2:0]: Selección de la operación (Señales S2, S1 y S0). (Salida) R[3:0]: Resultado de la operación entre A y B. (Salida) Cout: Acarreo de salida. Estímulos: Tiempo 0 ns 400 ns 800 ns 1200 ns 1600 ns 2000 ns 2400 ns 2800 ns 3200 ns 3600 ns 4000 ns 4400 ns Valores de las señales S[2:0] A[3:0] B[3:0] 0 5 3 1 5 3 2 5 3 3 5 3 4 2 3 4 12 3 5 5 3 5 3 2 6 2 5 6 5 5 7 4 5 7 13 5 Catálogo de Componentes que se pueden utilizar: Puertas NAND (2 entradas) ⇒ 74LS00 Puertas NAND (3 entradas) ⇒ 74LS10 Puertas NAND (4 entradas) ⇒ 74LS20 Puertas NAND (8 entradas) ⇒ 74LS30 Puertas AND (2 entradas) ⇒ 74LS08 Puertas OR (2 entradas) ⇒ 74LS32 Puertas XOR (2 entradas) ⇒ 74LS86 Inversores ⇒ 74LS04 Sumador de 4 bits ⇒ 74LS83 SISTEMAS DIGITALES 1º I.T. Informática de Sistemas Página 3 de 3. PRÁCTICA 5 CIRCUITOS ARITMÉTICOS - ALU Catálogo de Componentes que se pueden utilizar (Continuación): Multiplexor 8:1 ⇒ 74LS151 Para el correcto funcionamiento del multiplexor, la entrada G ha de situarse a nivel bajo. C 0 0 0 0 1 1 1 1 Entradas B 0 0 1 1 0 0 1 1 A 0 1 0 1 0 1 0 1 Salida Y D0 D1 D2 D3 D4 D5 D6 D7 Doble Multiplexor 4:1 ⇒ 74LS153 Para el correcto funcionamiento del multiplexor, la entrada G ha de situarse a nivel bajo. Entradas B A 0 0 0 1 1 0 1 1 Salida Y C0 C1 C2 C3 Cuádruple Multiplexor 2:1 ⇒ 74LS157 Para el correcto funcionamiento del multiplexor, la entrada G ha de situarse a nivel bajo. Entrada A’/B 0 1 Salida Y A B