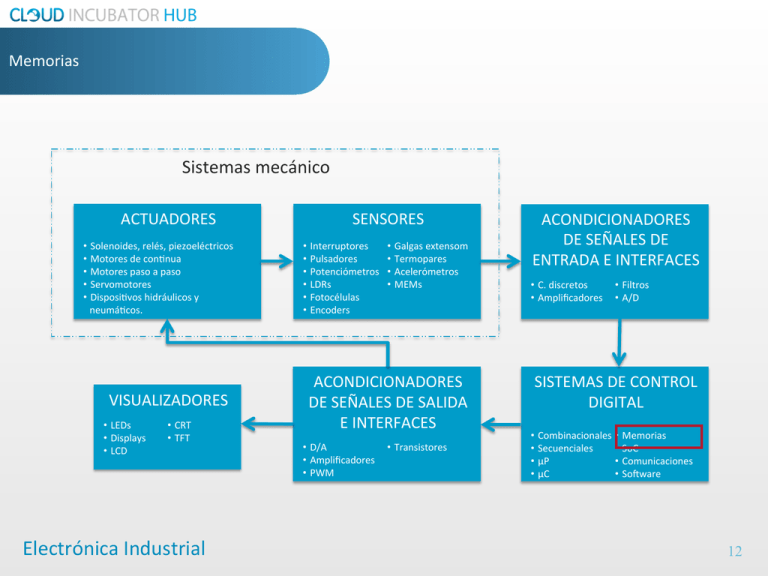

Electrónica Industrial

Anuncio

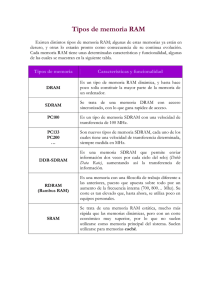

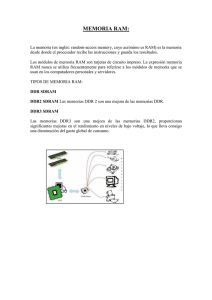

Memorias Sistemas mecánico ACTUADORES • Solenoides, relés, piezoeléctricos • Motores de con@nua • Motores paso a paso • Servomotores • Disposi@vos hidráulicos y neumá@cos. VISUALIZADORES • LEDs • Displays • LCD • CRT • TFT Electrónica Industrial SENSORES • Interruptores • Pulsadores • Potenciómetros • LDRs • Fotocélulas • Encoders • Galgas extensom • Termopares • Acelerómetros • MEMs ACONDICIONADORES DE SEÑALES DE SALIDA E INTERFACES • D/A • Transistores • Amplificadores • PWM ACONDICIONADORES DE SEÑALES DE ENTRADA E INTERFACES • C. discretos • Filtros • Amplificadores • A/D SISTEMAS DE CONTROL DIGITAL • Combinacionales • Memorias • Secuenciales • SoC • μP • Comunicaciones • μC • Soaware 12 Conceptos generales Memorias • • Una memoria es un disposi@vo capaz de almacenar información binaria durante cierto @empo y del cual se puede obtener información cuando se necesite para ser procesada. Esta formada por un conjunto de celdas binarias con la capacidad de almacenar un dato de muy diferentes tamaños (generalmente 8, 16, 32 y 64 bits). Bus de Direcciones A0 A1 2n x b RAM An-­‐1 Bus de Datos Señales de control Dirección Decodificador de direcciones Memoria en modo Array Dato CS R/W Read Electrónica Industrial Write 13 Conceptos generales Memorias 101 Bus de direcciones 0110 0001 0 1 Decodific 2 3 de 4 5 direcciones 6 7 1 0 1 1 1 0 1 1 0 1 1 1 0 0 0 0 0 0 0 0 1 1 0 0 0 1 0 1 0 0 0 0 1 0 0 0 1 1 1 0 0 1 1 0 0 0 0 1 1 0 0 1 1 0 1 0 1 1 1 0 0 1 1 1 Read/Write Bus de datos 001 Bus de direcciones Electrónica Industrial 0111 0000 0 1 Decodific 2 3 de 4 5 direcciones 6 7 1 0 1 1 1 0 1 1 0 1 1 1 0 0 0 0 0 0 0 0 1 1 0 0 0 1 0 1 0 0 0 0 1 0 0 0 1 1 1 0 0 1 1 0 0 0 0 1 1 0 0 1 1 0 1 0 1 1 1 0 0 1 1 1 Read/Write Bus de datos 14 Conceptos generales Memorias • Desde el punto de vista funcional, los sistemas digitales requieren de muy diferentes @pos de memoria y/o elementos de almacenamiento en cuanto a tamaño y velocidad de acceso, así por ejemplo en una computadora tenemos muy diferentes @pos de memoria en función de su funcionalidad. CACHE DE INSTRUC. REGISTROS CACHE DE NIVEL 2 MEMORIA RAM/ROM CACHE DE DATOS DISCO DURO CD DVD Aumenta el tamaño Aumenta la velocidad de acceso y el coste por byte Electrónica Industrial 15 Memorias Tipos de memoria Existen básicamente tres @pos de memorias: • RAM (Random Access Memory). Pierden la información almacenada cuando se les desconecta de la alimentación y se u@lizan para almacenamiento temporal de datos a corto plazo. • ROM (Read Only Memory). Memoria que conserva el contenido aun cuando se desconecta. • Memorias FLASH. Son memorias de lectura/escritura de alta densidad no volá@les. Se suelen u@lizar en lugar de las unidades de disco duro de baja capacidad. Electrónica Industrial 16 Memorias RAM Memorias Tipos de memorias RAM. Resumen Memoria de Acceso Aleatorio (RAM) RAM Está@ca (SRAM) RAM Está@ca Asíncrona (ASRAM) RAM Está@ca Síncrona a Ráfagas (SB SRAM) Electrónica Industrial RAM Dinámica (DRAM) Fast Page Mode DRAM (FPM DRAM) Extended Data Out DRAM (FPM DRAM) Burst EDO DRAM (BEDO DRAM) DRAM Síncrona (SDRAM) 17 Memorias Memorias RAM Tipos de memorias RAM RAM Está@cas (SRAM). • U@lizan flip-­‐flops como elementos de almacenamiento, siendo capaces de mantener los datos mientras la memoria está alimentada y sin necesidad de un circuito de refresco. • Son memorias volá@les ya que pierden la información si se les interrumpe la alimentación eléctrica. • Son más caras, pero más rápidas y consumen menos que las DRAM (especialmente en reposo). • Debido a su compleja estructura interna, son menos densas que las DRAM, y por lo tanto no se u@lizan cuando es necesario manejar una gran can@dad de datos. RAM Dinámicas (DRAM). • Los datos se almacenan en condensadores, que requieren recargarse (refrescarse) periódicamente para mantener el dato. • La celda de este @po de memorias es muy sencilla, lo que permite construir en un chip matrices de memorias muy grandes y densas a un costo por bit más bajo que en las memorias está@cas. • Se u@lizan cuando es necesaria una gran capacidad de datos, como por ejemplo en la memoria principal de los computadores personales y estaciones de trabajo. • Se dis@nguen dos sub@pos: Asíncronas y Síncronas. Electrónica Industrial 18 RAM Está@ca (I) Memorias Selección fila 0 Celda y matriz básica Selección fila 1 Selección Selección fila 2 Selección fila n Entrada Salida Entrada / Salida de datos Electrónica Industrial Bit 0 Bit 1 Bit 2 Bit 3 19 Memorias RAM Está@ca (II) Tipos de SRAM SRAM Asíncrona. • Independientes de la frecuencia del reloj. • Están disponibles en tamaños desde 4Kb hasta 32Mb. • Con un @empo reducido de acceso, son adecuadas para el uso en equipos de comunicaciones, como switches, routers, teléfonos IP, tarjetas DSLAM, y en electrónica de automoción. • Solo necesitan tres señales de control: Chip Enable (CE), Write Enable (WE), y Output Enable (OE). SRAM Síncrona. • Todas las operaciones son controladas por el reloj del sistema. • Además de las señales de control Chip Enable (CE), Write Enable (WE), y Output Enable (OE) se hace necesaria la señal de reloj (CLK) Sus caracterís@cas dependen fuertemente del @po de transistor que se u@lice en su construcción: • • Transistor Bipolar de Unión o BJT (de @po TTL o ECL). Muy rápidos, pero con un consumo muy alto. MOSFET (de @po CMOS). Consumo reducido, los más u@lizados actualmente. Electrónica Industrial 20 Memorias RAM Está@ca (III) Modos en que se encuentran las SRAM Como memorias de propósito general en forma de chip. • Las SRAM asíncronas ofrecen transferencias de hasta 16Mbit por chip. • Las SRAM síncronas se consiguen transferencias de hasta 18Mbit por chip. Se usan principalmente como caches y otras aplicaciones que requieran transferencias rápidas. Integradas dentro de un chip. • Como memoria RAM o de cache en microcontroladores. • Como cache primaria en microcontroladores, como por ejemplo la familia x86. • Para almacenar los registros de microprocesadores. • En FPGAs y CPLDs. Electrónica Industrial 21 Ejemplo de SRAM Asíncrona (I) Memorias μPD43256B, 32K x 8 bits Bus de Direcciones A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 CS Señales de control 215 = 32.767 I/O0 I/O1 I/O2 I/O3 I/O4 I/O5 I/O6 I/O7 Bus de Datos Chip Select Write R / W OE Electrónica Industrial RAM 32K x 8 Read Output Enable 22 Ejemplo de SRAM Asíncrona (II) Memorias Organización interna A0 A2 A3 Bus de direcciones A4 Banco de Memoria 256 Filas x 128 Columnas x 8 Bits Decodif Filas 256 Filas A1 Banco de Memoria A5 A6 128 Columnas A7 I/O0 Bus de Datos 8 Bits I/O Control de datos de entrada Decodificador Columnas I/O7 CS Bus de Control Datos de Salida A7 A8 A9 A10 A11 A12 A13 WE OE Electrónica Industrial 23 Ejemplo de SRAM Asíncrona (III) Memorias Ciclo de lectura tRC Dirección Válida Dirección tAQ CS (Chip Select) tEQ tGQ OE (Output Enable) Dato de salida Electrónica Industrial Dato Válido 24 Ejemplo de SRAM Asíncrona (IV) Memorias Ciclo de escritura tWC Dirección Dirección Válida CS (Chip Select) WE (Write Enable) ts(A) tWD Dato de entrada Electrónica Industrial Th(D) Dato Válido 25 RAM Dinámica (I) Memorias Ciclo de escritura en una DRAM Columna Refresco Fila DOUT R / W BAJO Refresco Fila ALTO Escritura de un 1 Electrónica Industrial BAJO ALTO DOUT BAJO BAJO DIN ALTO Columna ALTO R / W DIN BAJO BAJO Escritura de un 1 26 RAM Dinámica (II) Memorias Ciclo de lectura y refresco en una DRAM Columna Refres Fila BAJO Refres Fila ALTO DOUT ALTO R / W ALTO DIN Lectura de un 1 Electrónica Industrial Columna ALTO DOUT ALTO R / W ALTO ALTO ALTO DIN ALTO Refresco de un 1 27 RAM Dinámica (III) Memorias Organización básica de una DRAM de 1M x 1 bit Controlador de refresco Contador de refresco A0 / A10 A1 / A11 A2 / A12 A3 / A13 A4 / A 14 A5 / A15 A6 / A16 A7 / A17 A8 / A18 A9 / A19 Selector de Datos Dec Filas Banco de Memoria 1024 Filas x 1024 Columnas Dec Col Buffers de entrada / salida Latch Dir. Col. Latch Dir. Filas DOUT DIN CAS Electrónica Industrial RAS R / W E 28 RAM Dinámica (IV) Memorias Mul@plexación del bus de direcciones Dirección Dirección de la fila Dirección de la columna RAS CAS La dirección de la fila se captura cuando la señal de RAS es 0 La dirección de la columna se captura cuando la señal de CAS es 0 Electrónica Industrial 29 RAM Dinámica (V) Memorias Ciclo de lectura con bus de direcciones mul@plexado tRC Dirección Dirección de la Fila Dirección de la Columna RAS CAS R / W DOUT Electrónica Industrial Dato válido 30 RAM Dinámica (VI) Memorias Ciclo de escritura con bus de direcciones mul@plexado tWC Dirección Dirección de la Fila Dirección de la Columna RAS CAS R / W DIN Electrónica Industrial Dato válido 31 RAM Dinámica (VII) Memorias Memorias del @po RAM Dinámica Asíncrona Acrónimo Nombre Vigencia DRAM Dynamic RAM 1969-­‐1990 Son las primeras, se u@lizan para almacenamiento masivo FPM-­‐RAM Fast Page Mode RAM 1989-­‐1995 70 o 60 ns. Fueron muy populares. Se comenzaron a u@lizar en los 486 y los primeros Pen@um EDO-­‐RAM Extended Data Output RAM 1995-­‐2000 40 0 30 ns. Supone una mejora sobre su antecesora la FPM BEDO-­‐ RAM Burst Extended Data Output RAM 1997-­‐2000 Supone una mejora sobre su antecesora la EDO. Compite con la SDRAM. Electrónica Industrial Tiempos de acceso Observaciones 32 RAM Dinámica (VIII) Memorias Memorias del @po RAM Dinámica Síncrona Acrónimo Nombre Vigencia SDRAM Synchronous Dynamic RAM 1993-­‐ DDR SDRAM Double Data Rate SDRAM 7.5, 6 y 5 ns DDR2 SDRAM Double Data Rate 2 SDRAM 5, 3.75, 3 y 2.5 ns DDR3 SDRAM Double Data Rate 3 SDRAM 2.5, 1.87, 1.5 y 1.25 ns DDR4 SDRAM Double Data Rate 3 SDRAM Electrónica Industrial Tiempos de acceso Observaciones A par@r del año 2000 sus@tuye a prác@camente todas las DRAM Se conoce también como DDR1 SDRAM. Disponible a par@r de 2014 33 Memorias RAM Dinámica (IX) Tipos de formatos DIP (Dual in Package, 14 o 16 pines). Años 80. SIPP (Single In-­‐line Pin Package32 pines, 8 bits). DRAMs soldadas en un PCB. 80286. No estaban estandarizadas. SIPP 32 Pines SIMM (Single In-­‐line Memory Module, 32 y 72 pines). Placas de circuito impreso sobre las que se montan los integrados de memoria DRAM, FPM-­‐RAM y EDO-­‐RAM. Principios de los 80 hasta finales de los 90. Fueron estandarizadas por JEDEC. SIMM 32 Pines SIMM 72 Pines DIMM (Dual in-­‐line Memory Module, 72, 100, 144 y 168 pines). U@lizan memorias síncronas (SDRAM, SDR SDRAM) DDR DIMM (DDR Dual in-­‐line Memory Module, 184, 200, 204, 240 y 244 pines). U@lizan memorias síncronas (DDR SDRAM) Electrónica Industrial DIMM 168 Pines DIMM 184 Pines 34 Memorias ROM (I) Memorias Tipos de memorias ROM. Memorias de Solo Lectura (ROM) ROM de máscara ROM programable (PROM) PROM borrable (EPROM) Borrable con ultravioletas (UV EPROM) Electrónica Industrial Borrable eléctricamente (EEPROM) 35 Memorias Memorias ROM (II) Tipos de memorias ROM • PROM (Programable Read Only Memory) Funcionamiento basado en el principio de fusibles No puede borrarse ni reprogramarse • UV EPROM (UV Erasable-­‐Programable Read Only Memory) Funcionamiento basado en el principio de fusibles Puede borrarse mediante luz ultravioleta Se reprograma eléctricamente • EEPROM (Electrically Erasable-­‐Programable Read Only Memory) Funcionamiento basado en el principio de fusibles Puede borrarse con impulsos eléctricos controlados Se reprograma eléctricamente Electrónica Industrial 36 Memorias FLASH (I) Memorias Célula de memoria Flash Drenador Compuerta Drenador Compuerta Fuente Muchos electrones = un 0 almacenado Electrónica Industrial Fuente Pocos electrones = un 1 almacenado 37 Memorias FLASH (II) Memorias Procesos de escritura de un 0 o un 1 en una célula flash VD VD +VPROG 0 V. Procesos de lectura de un 0 o un 1 en una célula flash VD +VREAD +VREAD Electrónica Industrial VD 0 V. I 0 V. 38 Memorias FLASH (II) Memorias Procesos de escritura de un 0 o un 1 en una célula flash 0 V +VERASE Electrónica Industrial 39 Dr. Andrés Iborra Universidad Politécnica de Cartagena Campus Muralla del Mar, s/n 30202 Cartagena Tel. Fax. E-­‐mail Twiyer Lista de correo Www +34 968 32 56 54 +34 968 32 53 45 [email protected] @CincubatorHUB @aiborra cloud-­‐[email protected] www.cincubator.com