Universidad de Costa Rica Facultad de Ingeniería Escuela de

Anuncio

Universidad de Costa Rica

Facultad de Ingeniería

Escuela de Ingeniería Eléctrica

Procedimiento de diseño e implementación de circuitos digitales utilizando herramientas EDA de

código abierto

Por:

Gerardo Castro Jiménez

Ciudad Universitaria Rodrigo Facio

Junio del 2008

Procedimiento de diseño e implementación de circuitos digitales utilizando herramientas EDA de

código abierto

Por:

Gerardo Castro Jiménez

Sometido a la Escuela de Ingeniería Eléctrica

de la Facultad de Ingeniería

de la Universidad de Costa Rica

como requisito parcial para optar por el grado de:

LICENCIADO EN INGENIERÍA ELÉCTRICA

Aprobado por el Tribunal:

_________________________________

Ing. Enrique Coen Alfaro, M.Sc.

Representante del Director, Escuela de Ingeniería Eléctrica

_________________________________

Ing. Randolph Steinvorth Fernández, PhD.

Director, Comité Asesor

_________________________________

Ing. Jorge Romero Chacón, PhD.

Miembro, Comité Asesor

Director, Escuela de Ingeniería Eléctrica

_________________________________

Lic. Roberto Rodríguez Rodríguez

Miembro, Comité Asesor

_________________________________

Ing. José Luis López Sauma, M.Sc.

Miembro del Tribunal

ii

DEDICATORIA

A Dios por guiarme y por ser la luz de mi camino.

A mi familia por estar siempre conmigo, por su apoyo y ser incondicionales.

A mis amigos por las experiencias que hemos vivido.

“Creo más en la imaginación que en el conocimiento”

iii

RECONOCIMIENTOS

A todos los educadores y personas que invirtieron tiempo valioso de sus vidas para transmitirme sus conocimientos y experiencias.

Este trabajo es el reflejo de todo lo que me enseñaron.

Que Dios los bendiga.

iv

ÍNDICE GENERAL

ÍNDICE DE FIGURAS................................................................................ viii

ÍNDICE DE TABLAS......................................................................................x

NOMENCLATURA........................................................................................xi

RESUMEN.................................................................................................... xiii

CAPÍTULO 1: Introducción ...........................................................................1

1.1

1.2

Alcances..................................................................................................................1

Objetivos.................................................................................................................1

1.2.1

Objetivo general..............................................................................................1

1.2.2

Objetivos específicos ......................................................................................1

1.3

Justificación ............................................................................................................1

1.4

Planteamiento del problema....................................................................................2

1.5

Metodología ............................................................................................................3

CAPÍTULO 2: Desarrollo teórico ..................................................................6

2.1 Historia y estado del arte de los FPGAs ...........................................................................6

2.2 Antecedentes en la UCR ...................................................................................................6

2.3 FPGAs...............................................................................................................................7

2.4 Flujo de diseño mediante FPGAs utilizando las herramientas de Xilinx .......................11

2.5 Introducción a la codificación de predicción lineal (LPC) de la voz humana................14

CAPÍTULO 3: Planteamiento de un procedimiento basado en

herramientas de código abierto ....................................................................17

CAPÍTULO 4: Diseño del codificador/decodificador de voz.....................21

4.1 Descripción general ........................................................................................................21

4.2 Componentes ..................................................................................................................21

4.3 Diagrama de estados general ..........................................................................................23

4.4 Descripción de los circuitos digitales .............................................................................25

4.5 Arquitectura de las máquinas de estado y de la asignación de registros ........................28

4.5.1 Protocolo de comunicación entre circuitos..........................................................28

4.5.2 Protocolo de cambio de estado y asignación de estado .......................................29

CAPÍTULO 5: Compilación y Simulación Funcional ................................30

5.1

5.2

Descripción en Verilog .........................................................................................30

Etapa de Compilación y Simulación Funcional....................................................32

5.2.1

Simulación funcional ....................................................................................32

v

CAPÍTULO 6: Síntesis en Icarus Verilog....................................................36

6.1

6.2

Descripción del proceso de síntesis con Icarus Verilog .......................................36

Descripción del proceso de síntesis para la arquitectura Virtex ...........................37

6.2.1

Características del sintetizador de Icarus Verilog.........................................37

6.2.2

Verilog sintetizable para la arquitectura Virtex ............................................39

6.2.3

Adición de parámetros y restricciones en el proceso de síntesis para la

arquitectura Virtex ........................................................................................................47

CAPÍTULO 7: Implementación, Programación y Simulaciones postimplementación...............................................................................................50

7.1 Proceso de implementación ...........................................................................................50

Proceso de Traducción: Translate.................................................................................50

7.1.2 Proceso de Mapeo: Map ......................................................................................52

7.1.3 Proceso de Posicionamiento y Enrutamiento: Place and Route ..........................54

7.1.4

Programación del FPGA y pruebas en circuito ............................................55

CAPÍTULO 8: Conclusiones y recomendaciones .......................................56

BIBLIOGRAFÍA............................................................................................58

APÉNDICE A: Diagrama de estados de los circuitos ................................60

A.1 Controlador A/D ............................................................................................................60

A.1.1 Registros: ............................................................................................................60

A.1.2 Diagrama de Estado: ...........................................................................................60

A.2 Controlador D/A ............................................................................................................61

A.2.1 Registros: ............................................................................................................61

A.2.2 Diagrama de Estado: ...........................................................................................61

A.3 Controlador de Memoria................................................................................................62

A.3.1 Registros: ............................................................................................................62

A.3.2 Diagrama de Estado: ...........................................................................................63

A.4 Controlador de Reproducción ........................................................................................64

A.4.1 Registros .............................................................................................................64

A.4.2 Diagrama de Estado ............................................................................................64

A.5 Controlador de Codificación..........................................................................................66

A.5.1 Registros .............................................................................................................66

A.5.2 Diagrama de Estado ............................................................................................67

A.6 Sonido con/sin Voz ........................................................................................................69

A.6.1 Registros .............................................................................................................69

A.6.2 Diagrama de Estado ............................................................................................70

A.7 Detección del Pitch ........................................................................................................71

A.7.1 Registros .............................................................................................................72

A.7.2 Diagrama de Estado ............................................................................................72

A.8 Coeficientes R ................................................................................................................74

vi

A.8.1 Registros .............................................................................................................74

A.8.2 Diagrama de Estado ............................................................................................75

A.9 Coeficientes LPC ...........................................................................................................76

A.9.1 Registros .............................................................................................................76

A.9.2 Diagrama de Estado ............................................................................................77

A.10 Filtro de Análisis..........................................................................................................79

A.10.1 Registros ...........................................................................................................79

A.10.2 Diagrama de Estado ..........................................................................................80

A.11 Filtro de Síntesis ..........................................................................................................82

A.11.1 Registros ...........................................................................................................82

A.11.2 Diagrama de Estado ..........................................................................................83

A.12 Sumador/Restador........................................................................................................85

A.12.1 Registros ...........................................................................................................85

A.12.2 Diagrama de Estado ..........................................................................................85

A.13 Multiplicador................................................................................................................87

A.13.1 Registros ...........................................................................................................87

A.13.2 Diagrama de Estado ..........................................................................................87

A.14 Divisor..........................................................................................................................88

A.14.1 Registros ...........................................................................................................88

A.14.2 Diagrama de Estado ..........................................................................................88

A.15 Raíz Cuadrada..............................................................................................................89

A.15.1 Registros ...........................................................................................................89

A.15.2 Diagrama de Estado ..........................................................................................90

APÉNDICE B: Modelos Matemáticos y Algoritmos de LPC ....................92

APÉNDICE C: Código en Matlab, equivalente en Software del circuito

diseñado...........................................................................................................96

APÉNDICE D: Problemas de temporización durante la etapa de

implementación.............................................................................................102

D.1 Problema de convergencia de la arquitectura microprogramada .................................102

D.2 Problema de alineación entre relojes ...........................................................................103

APÉNDICE E: Guía del procedimiento de diseño e implementación de

circuitos digitales utilizando herramientas EDA de código abierto........106

vii

ÍNDICE DE FIGURAS

Figura 1.1: Flujo de diseño e implementación mediante FPGAs [8] ...................................3

Figura 1.2: Metodología de diseño .....................................................................................4

Figura 2.1: Diagrama de un FPGA [8] .................................................................................7

Figura 2.2: Estructuras de FPGAS [8]..................................................................................8

Figura 2.3: Estructuras de CLB [8] ......................................................................................8

Figura 2.4: Líneas de interconexión [9] ...............................................................................9

Figura 2.5: Fabricantes de FPGAs [8] ................................................................................10

Figura 2.6: Flujo de diseño mediante FPGAs [8] ...............................................................11

Figura 2.7: Modelo del tracto vocal [3] ..............................................................................14

Figura 2.9: Esquema de decodificación LPC [3] ...............................................................16

Figura 3.1 Flujo de diseño basado en herramientas EDA de código abierto....................18

Figura 4.1 Diagrama de bloques del diseño......................................................................23

Figura 4.2 Diagrama de estado general del diseño ...........................................................24

Figura 4.3 Arquitectura de la asignación de registros ......................................................28

Figura 4.4 Protocolo de comunicación entre los circuitos................................................29

Figura 4.5 Protocolo de cambio de estado y asignación de estado..................................29

Figura 5.1 Estructura de la descripción en Verilog para los circuitos diseñados ............30

Figura 5.2 Estructura jerárquica establecida para el proyecto .........................................31

Figura 5.3 Esquema jerárquico para simulación funcional...............................................32

Figura 5.4 Simulación funcional del controlador de memoria DRAM en GTKWave ....33

Figura 5.5 Simulación funcional del divisor de 32bits ....................................................34

Figura 5.6 Simulación funcional del codificador/decodificador de voz en GTKWave...35

Figura 6.1 Proceso de Síntesis con Icarus Verilog ..........................................................36

Figura 6.2 Archivo EDIF para multiplexor 4 a 1 (if-else) ................................................43

Figura 6.3 Esquemático del archivo de síntesis para multiplexor 4 a 1 (if-else) ..............43

Figura 6.4 Archivo EDIF, sección para multiplexor 4 a1 (case) .....................................44

viii

Figura 6.5 Esquemático del archivo de síntesis para multiplexor 4 a 1 (case) .................44

Figura 6.6 Esquemático de celdas de tipo PAD en la arquitectura Virtex........................48

Figura 7.1 Resumen de recursos utilizados en el FPGA, circuito completo ....................54

Figura 7.2 Reporte final de relojes del WebPack, circuito completo ...............................54

Figura 6. Filtro de análisis de voz.....................................................................................94

Figura 7. Filtro IIR todo polos para síntesis de voz..........................................................94

Figura D.1 Arquitectura microprogramada ....................................................................102

Figura D.2 Arquitectura one-hot.....................................................................................103

Figura D.3 Diagrama temporal, problema de alineación de relojes ...............................104

Figura D.4 Diagrama temporal, solución al problema de alineación de relojes .............105

ix

ÍNDICE DE TABLAS

Tabla 4.1 Circuitos diseñados para el codificador/decodificador de voz .........................22

Tabla 5.1 Nombre de los módulos en Verilog para cada circuito....................................31

Tabla 6.1 Celdas de la librería Virtex que maneja Icarus Verilog....................................40

Tabla A.1 Diagrama de Estado del Controlador A/D.......................................................61

Tabla A.2 Diagrama de Estado del Controlador D/A.......................................................62

Tabla A.3 Diagrama de Estado del Controlador de Memoria ..........................................64

Tabla A.4 Diagrama de Estado del Controlador de Reproducción...................................66

Tabla A.5 Diagrama de Estado del Controlador de Codificación ....................................69

Tabla A.6 Diagrama de Estado de Sonido con/sin Voz....................................................71

Tabla A.7 Diagrama de Estado de Detección del Pitch....................................................74

Tabla A.8 Diagrama de Estado de Coeficientes R............................................................76

Tabla A.9 Diagrama de Estado de Coeficientes LPC.......................................................79

Tabla A.10 Diagrama de Estado del Filtro de Análisis ....................................................82

Tabla A.11 Diagrama de Estado del Filtro de Síntesis .....................................................85

Tabla A.12 Diagrama de Estado del Sumador/Restador ..................................................87

Tabla A.13 Diagrama de Estado del Multiplicador ..........................................................88

Tabla A.14 Diagrama de Estado del Divisor ....................................................................89

Tabla A.15 Diagrama de Estado de la Raíz Cuadrada......................................................91

x

NOMENCLATURA

CLB Configurable Logic Block – Bloque Lógico Configurable

CMOS Complementary Metal Oxide Semiconductor – Semiconductor de Óxido Metálico Complementario

EDA Electronic Design Automation - Automatización del Diseño Electrónico

EDIF Electronic Design Interchange Format - Formato de Intercambio de Diseño

Electrónico

EEPROM Electric Erasable Programmable Read Only Memory - Memoria de Solo

Lectura Eléctricamente Borrable

EPROM Erasable Programmable Read Only Memory – Memoria de Solo Lectura

Borrable

FPGA Field Programmable Gate Array - Arreglo de Puertas Programables por

Campo

FPLA Field Programmable Logic Array – Arreglo de Lógica Programable por

Campo

GAL Gate Array Logic – Arreglo de Puertas Lógicas

HDL Hardware Description Language – Lenguaje de Descripción de Hardware

IIR Infinite Impulse Response – Respuesta Infinita al Impulso

IOB Input/Output Block - Bloque Entrada/Salida

LPC Linear Prediction Coding – Codificación por Predicción Lineal

LPM Library of Parameterized Modules – Librería de Módulos Parametrizable

PAL Programmable Array Logic – Arreglo de Lógica Programable

PCM Pulse Code Modulation – Codificación por modulación de pulsos

xi

PEEL Programmable Electric Erasable Logic – Lógica Programable Eléctricamente Borrable

PLD Programmable Logic Device – Dispositivo Lógico Programable

RAM Random Access Memory – Memoria de Acceso Aleatorio

VLSI Very Large Scale Integration – Integración a Escala Muy Alta

xii

RESUMEN

Este trabajo presenta un procedimiento de diseño e implementación

de circuitos digitales utilizando herramientas de código abierto. Para

su desarrollo se utilizó el diseño de un codificador/decodificador de

voz. Como herramientas de código abierto se emplearon Icarus Verilog como simulador y sintetizador en HDL Verilog y GTKWave

como visor de ondas en combinación con la herramienta propietaria

WebPack de Xilinx. Se describieron en Verilog un conjunto de circuitos digitales de forma conductual y jerárquica que utilizaban codificación predictiva lineal para codificar y decodificar la voz. Se

realizaron simulaciones funcionales y con Icarus Verilog se sintetizó

el circuito completo para la arquitectura Virtex de Xilinx. La implementación se realizó para un FPGA SPARTAN3E de Xilinx. Se programó físicamente el circuito diseñado con resultados de

funcionamiento exitosos. Durante este proceso se revelaron las capacidades y limitaciones de las herramientas de código abierto. Como

resultado se obtiene una guía detallada del procedimiento para que

sea utilizada en trabajos futuros y en cursos en la Universidad.

Se concluye que el procedimiento y las herramientas tienen la capacidad suficiente para el desarrollo de circuitos digitales, pero se recomienda completar y mejorarlas para que el procedimiento sea más

robusto.

xiii

CAPÍTULO 1: Introducción

1.1 Alcances

En este proyecto se presenta un procedimiento de diseño e implementación de circuitos digitales utilizando herramientas EDA de código abierto.

El procedimiento se desarrolló a través de una aplicación de procesamiento digital de

señales. La aplicación que se seleccionó fue un codificador/decodificador de voz, cuyo diseño parte del modelo teórico de predicción lineal de la voz humana. No constituyó un objetivo de este proyecto el analizar u optimizar el algoritmo utilizado ya que

este fue únicamente un vehículo para demostrar el procedimiento de diseño que se

presenta.

Se utiliza Verilog, como lenguaje de descripción de hardware estándar, para describir

la arquitectura del circuito digital.

Las etapas de compilación, simulación y síntesis se realizaron mediante herramientas

EDA de código abierto y con formatos estándar que permiten intercambiar la información con otras herramientas disponibles en la industria. Las herramientas EDA de

código abierto están disponibles al público en general sin costo alguno. Esto constituye la base del procedimiento y su principal distinción.

Se obtuvo un circuito digital en el FPGA: SPARTAN3E de Xilinx como resultado final del procedimiento desarrollado.

1

1.2 Objetivos

1.2.1

Objetivo general

Desarrollar un procedimiento de diseño e implementación de circuitos digitales basa-

do en herramientas EDA de código abierto, utilizando como ejemplo un codificador/decodificador de voz

1.2.2

•

Objetivos específicos

Diseñar la arquitectura de un circuito digital que realice en hardware el algoritmo de

codificación/decodificación de voz a partir del método de codificación de predicción lineal de la voz humana.

•

Describir el circuito digital del codificador/decodificador de voz mediante el lenguaje de descripción de hardware Verilog.

•

Utilizar herramientas de código abierto de uso general que permitan construir el circuito digital en cualquier dispositivo independientemente del fabricante del mismo.

•

Establecer la etapa de síntesis del procedimiento de diseño para que se pueda programar en el FPGA SPARTAN3E de Xilinx.

•

Verificar mediante pruebas cualitativas que el circuito programado en el FPGA realiza el algoritmo de codificación de voz utilizado.

•

Documentar el procedimiento de diseño propuesto para que pueda ser utilizado ampliamente y permita profundizar en el estudio de los dispositivos lógicos programables.

1.3 Justificación

El proyecto surgió a partir de la dependencia que tiene el flujo de diseño e implementación en FPGAs de Xilinx. El flujo actual utiliza herramientas y formatos

propietarios del fabricante limitando así la portabilidad de los diseños a otras plataformas. Esto motivó a buscar un procedimiento que utilice herramientas EDA de có1

2

digo abierto y formatos estándar de la industria que lograra obtener mayor flexibilidad. Con el uso de herramientas EDA de código abierto se obtiene independencia del

fabricante y libertad para modificar y mejorar sus capacidades por parte de la Universidad de Costa Rica. Los formatos estándar, que no dependen del fabricante, permiten

que el diseño se pueda transportar a otras marcas o tipos de dispositivos programables

y hasta a VLSI. Está claro que existen etapas del flujo que siempre van a depender de

la marca del dispositivo pero lograr una independencia en la mayoría de las fases es

el principio para diseñar e implementar en cualquier tipo y marca de dispositivo programable.

Por otro lado, las ventajas que presentan los FPGAs en el diseño de circuitos digitales

y su potencial a nivel académico, se ve limitado por los pocos proyectos realizados en

la Universidad de Costa Rica. Esta situación genera la necesidad de ampliar la documentación y profundizar en este campo. La documentación de este procedimiento dará una mayor referencia y podría ser de utilidad para futuros proyectos de graduación

y cursos en la Universidad en esta área.

1.4 Planteamiento del problema

El flujo de diseño e implementación general de un circuito digital FPGA consiste del diagrama de bloques mostrado a continuación [8]:

3

Figura 1.1: Flujo de diseño e implementación mediante FPGAs [8]

Actualmente todas las etapas del proceso se realizan mediante el conjunto de

herramientas EDA de Xilinx conocidas como: ISE Webpack (versión gratuita con limitaciones) o ISE Foundation (versión completa). Estas herramientas están orientadas

hacia dispositivos FPGA de esta marca por lo que no son útiles para otras plataformas, esto hace que el flujo sea poco flexible. Durante el proceso se crean y se utilizan

archivos con formatos propietarios de Xilinx, lo cual impide se puedan utilizar en

otro tipo de herramientas o aplicaciones. Es decir que etapas ya realizadas se volverán

a repetir si se cambia de plataforma.

Por otro lado, la poca documentación que se encuentra acerca de la utilización

de FPGAs como método para implementar circuitos digitales, provoca que los dispositivos no se puedan utilizar en los cursos impartidos en la Universidad ya que no se

tiene la suficiente experiencia en el uso de ellos.

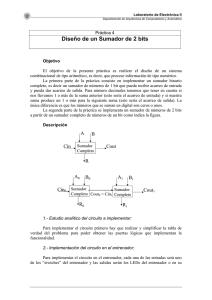

1.5 Metodología

4

Para cumplir con los objetivos planteados, se contó con las herramientas de código libre Icarus Verilog y GTK Wave. Icarus Verilog es un simulador de Verilog y

sintetizador [17] y GTK Wave se utilizó para análisis temporal [16].

La metodología constó de 7 etapas que se enuncian a continuación:

1. A partir del método de predicción lineal para codificación de la voz, se extrajo

las especificaciones arquitectónicas y elementos básicos para el diseño del codificador/decodificador de voz.

2. Con base en las fórmulas del modelo matemático se construyeron los módulos

en Verilog que describían el circuito digital. Se utilizó la metodología que se

muestra en la figura 2, donde se define el circuito completo y dentro de este se

encuentran circuitos complejos que a su vez contienen circuitos sencillos.

Figura 1.2: Metodología de diseño

3. Cada circuito simple pasó por una simulación funcional en Icarus Verilog y un

análisis temporal mediante GTKWave.

4. Obtenida una descripción funcional en Verilog de los circuitos simples, estos

se sintetizaron en el formato estándar EDIF mediante Icarus Verilog y se implementaron mediante la herramienta ISE Webpack de Xilinx.

5. Al finalizar este proceso para cada circuito simple, se continuó con los circuitos complejos que pasaron por las etapas 3 y 4. De esta forma el procedimiento se ejercitó en cada iteración.

5

6. Finalmente, el circuito completo formado por los circuitos complejos y sencillos se sometió a las etapas 3 y 4, donde se obtuvo una síntesis general del circuito.

7. Seguidamente, se hizo la programación del circuito completo en el FPGA,

donde se realizaron las pruebas en circuito. SPARTAN3E de Xilinx fue el

FPGA utilizado el cual se encontraba disponible en la bodega de la Escuela de

Ingeniería Eléctrica.

8. Finalmente, se documentó el procedimiento en forma de guía, donde se detalla

cada etapa.

CAPÍTULO 2: Desarrollo teórico

2.1 Historia y estado del arte de los FPGAs

En 1984, Ross Freeman funda Xilinx y crea el circuito del tipo FPGA, distinto de

otros dispositivos lógicos programables (PLD). Estos circuitos tuvieron un gran éxito en el

mercado y permitieron el desarrollo de la que hoy es empresa líder del sector de FPGAs [7].

Por otra parte, en esta época se fundaron otras dos empresas. Atmel se fundó en 1984,

fabricando PLDs y FPGAs [7]. Actel se fundó en 1985, desarrollando FPGAs con tecnología

basada en antifusibles y convirtiéndose en los líderes de esta tecnología desde 1994, presentando además la segunda cuota más grande del mercado de FPGAs [7]. Por su parte, Altera también introdujo circuitos del tipo FPGA, de arquitectura cuadrícula, siendo

actualmente el tercer fabricante en cuota de mercado [7].

Actualmente, los fabricantes introducen mejoras en las nuevas FPGAs como [7]:

•

Reconfiguración parcial en el sistema (“Field partial reconfiguration”), es decir, de

sólo una parte de la FPGA, en lugar de su totalidad como es habitual actualmente.

•

Incremento de la capacidad lógica, es decir, mayor número de puertas lógicas equivalentes.

•

Incremento de la capacidad de interconexión y disminución de los retardos de propagación, con el fin de alcanzar un mayor aprovechamiento de la capacidad de lógica y aumento en la velocidad del FPGA.

2.2 Antecedentes en la UCR

Los trabajos realizados en la Universidad de Costa Rica en el área de los dispositivos

lógicos programables no son muchos. Se ha sintetizado e implementado la CPUCR [2] [5], un

filtro digital

[4]

y un probador de escaneo controlado por una PC para realizar pruebas es-

tructurales a microprocesadores [1]. Para el desarrollo de todas estas aplicaciones se han utilizado PLD’s de la marca Xilinx modelo SPARTAN2E. Como herramienta principal EDA

6

7

se ha utilizado ISE Webpack del fabricante en combinación con algunas otras herramientas

propietarias como Verilogger y ModelSim.

2.3 FPGAs

Un FPGA es un dispositivo lógico programable o PLD (“Programmable Logic Device”),

cuyas características pueden ser modificadas y almacenadas mediante programación [9]. Poseen una estructura interna formada por: matriz de bloques lógicos configurables CLB

(“Configurable Logic Block”) que se comunican entre sí y con los bloques de Entrada/Salida I/OB (“Input/Output Block”) a través de canales de ruteo horizontal.

Figura 2.1: Diagrama de un FPGA [8]

Estructura de una FPGA

Dependiendo del fabricante se pueden encontrar diferentes soluciones. Las FPGAs

que existen actualmente en el mercado, dependiendo de la estructura que adoptan los bloques lógicos que tengan definidos, se pueden clasificar como pertenecientes a cuatro grandes familias [9]:

1. Matriz Simétrica (“Symmetrical Array”).

2. Basada en Filas (“Row Based”).

3. Mar de puertas (“Sea-of-Gates”).

4. PLDs Jerárquicos (Hierarchical PLD).

8

Figura 2.2: Estructuras de FPGAS [8]

CLBs: Bloques Lógicos Configurables

Cada CLB presenta una sección de lógica combinacional programable y registros de

almacenamiento:

Figura 2.3: Estructuras de CLB [8]

Los registros de almacenamiento sirven como herramientas en la creación de lógica

secuencial. La sección de lógica combinacional suele consistir en una LUT (“Look Up Table”), que permite implementar cualquier función booleana a partir de sus variables de entrada. Se presentan también multiplexores y conmutadores, como elementos adicionales de

direccionamiento de los datos del CLB, los cuales permiten variar el tipo de salidas (com-

9

binacionales o registradas), facilitan caminos de realimentación, o permiten cambiar las entradas de los biestables.

Bloques entrada/Salida (I/OBs)

La periferia del FPGA está constituida por bloques de entrada/salida configurables

por el usuario. Cada bloque puede ser configurado independientemente para funcionar como entrada, salida o bidireccional, admitiendo también la posibilidad de control triestado.

Los IOBs pueden configurarse para trabajar con diferentes niveles lógicos (TTL,

CMOS,…). Además, cada IOB incluye flip-flops que pueden utilizarse para registrar tanto

las entradas como las salidas.

Líneas de interconexión

Constituyen un conjunto de caminos que permiten conectar las entradas y salidas de

los diferentes bloques. Están constituidas por líneas metálicas de dos capas que recorren

horizontal y verticalmente las filas y columnas existentes entre los CLBs.

Dos elementos adicionales participan activamente en el proceso de conexión:

Puntos de Interconexión Programable PIP (“Programmable Interconnection Point”)

que permiten la conexión de CLBs e IOBs a líneas metálicas cercanas.

Matrices de interconexión SW (“ Switch Matrix o Magic Box”) que son dispositivos de conmutación distribuidos de forma uniforme por la FPGA.

Figura 2.4: Líneas de interconexión [9]

Los diferentes modelos comerciales se diferencian en [8]:

•

Arquitectura: Gate Array (Filas), Mar de puertas, Matriz simétrica.

•

Tipo de CLB: Puertas lógicas, multiplexores, tabla de búsqueda (LUT).

10

•

Arquitectura de las interconexiones: Canales de routing, red de interconexión.

•

Tecnología de la programación: antifusibles, memoria no volátil (EPROM,

EEPROM), memoria FLASH (RAM, FLASH).

A continuación se presentan una tabla con los principales fabricantes de FPGAs y sus

características [8]:

Figura 2.5: Fabricantes de FPGAs [8]

Ventajas y Desventajas de los FPGAs con respecto a otras tecnologías

Las ventajas que poseen los FPGAs en el área de diseño de circuito digital son las siguientes [15]:

•

Reducción del tiempo de introducción al mercado de productos.

•

Habilidad de ser reprogramados después de haber salido al mercado a fin de corregir posibles errores, y reducir los costos de investigación, diseño y pruebas de un

nuevo producto.

•

Facilidad de diseño, en la mayoría de las FPGAs se pueden encontrar funciones de

alto nivel (como sumadores y multiplicadores) embebidas en la propia matriz de interconexiones, así como bloques de memoria.

•

Mayor densidad de los elementos lógicos programables en puertas lógicas equivalentes, en el orden de cientos de miles hasta millones de ellas, que otras tecnologías.

•

Mayor flexibilidad debido a su arquitectura y la enorme libertad disponible en la interconexión.

11

Las desventajas que poseen los FPGAs en el área de diseño de circuito digital son las

siguientes [15]:

•

Son generalmente más lentos.

•

No pueden soportar diseños muy complejos.

•

Consumen más energía.

2.4 Flujo de diseño mediante FPGAs utilizando las herramientas de

Xilinx

La figura muestra el diagrama de flujo para el diseño de sistemas implementados sobre FPGAs de Xilinx. El proceso de diseño se divide en cuatro fases: descripción del modelo, síntesis, implementación y programación [8].

Figura 2.6: Flujo de diseño mediante FPGAs [8]

Al finalizar cada una de las fases es preciso comprobar la validez del diseño mediante

simulación, utilizando distintos tipos de simulación en cada una de ellas [11]:

•

Simulación funcional RTL para validar el modelo creado.

•

Simulación funcional post-síntesis a nivel de puertas para validar el modelo sintetizado.

•

Simulación temporal post-implementación para validar la implementación del modelo implementado.

12

•

Verificación en circuito.

El banco de pruebas creado para validar el modelo es único, siendo utilizado en todos

los tipos de simulación mencionados. Las dos últimas son simulaciones a nivel de puertas,

ya que el diseño esta expresado como una descripción estructural HDL en términos de las

celdas de la tecnología destino para la que se va a implementar.

Creación del modelo

El primer paso consiste en crear un modelo RTL del diseño que se pretende realizar.

Para ello se puede utilizar:

•

Un lenguaje de descripción de Hardware HDL (“Hardware Description Language”)

como: Verilog, VHDL y ABEL.

•

Un esquemático.

El diseño puede contener:

•

Código HDL genérico que describe lógica independiente de la tecnología donde se

va a implementar.

•

Componentes con instancias propias de la arquitectura del dispositivo en el que se

va a implementar.

Para el caso de utilización de componentes propios de la arquitectura del dispositivo

el sintetizador obtiene la descripción de dichos componentes de la biblioteca de celdas de la

tecnología destino. El formato de esta biblioteca dependerá de la herramienta de síntesis

utilizada.

Antes de proceder a la síntesis del diseño es preciso verificar el modelo creado mediante una simulación funcional la cual se puede construir con Test Bench Wave Form Editor (Editor de Formas de Onda de Prueba) de Xilinx. También se pueden crear archivos

con restricciones temporales o espaciales para la síntesis.

Síntesis del modelo

13

Una vez validado el modelo creado se procede a la síntesis de éste para lo cual se utiliza la herramienta de síntesis de Xilinx: XST [18]. El resultado de la síntesis es una lista de

conexiones en formato NGC propio de Xilinx (anteriormente XNF). Si en el proceso de

síntesis se fijan restricciones de diseño (topológicas o temporales) que afectan al proceso de

implementación éstas se exportan en la propia lista de conexiones.

Para comprobar los resultados de la síntesis es preciso realizar una simulación funcional (retardos unitarios) a nivel de puertas. El procedimiento a seguir es similar a la simulación funcional RTL.

Implementación del modelo

Una vez sintetizado el diseño se procede a su implementación. La implementación en

Xilinx consta de cuatro pasos [18]:

1. Traslate – Traducción: En esta fase, se enlazan los ficheros de lista de conexiones

(EDIF, NGC, XNF) creando un único fichero de salida en el que queda reflejada la

jerarquía citada. El formato de este fichero de salida se denomina: NGD (Native

Generic Design) y contiene componentes lógicos: puertas lógicas, biestables,

RAMs, etc.

2. Map – Mapeo: En esta etapa se mapean los componentes lógicos en los componentes físicos de que dispone la FPGA: tablas LUT, biestables, buffers triestado, etc. A

continuación se encapsulan estos componentes físicos en bloques configurables

(CLBs e IOBs), creando un fichero de salida en formato NCD (Native Circuit Design).

3. Place and Route – Posicionamiento y Ruteo: En esta etapa se pasa a realizar el posicionamiento e interconexión de los bloques configurables en el FPGA y se genera

un fichero de lista de conexiones en formato NCD. Una vez finalizado este proceso

se dispone de toda la información de retardos internos (elementos activos e interconexiones) y se puede realizar de nuevo un análisis estático de tiempos esta vez con

todos los datos de retardos internos. Después de realizar estas fases se obtiene la información para realizar simulaciones temporales del diseño completo y se puede

14

crear un archivo HDL estructural con base en los componentes físicos de la FPGA y

un fichero SDF con los retardos internos del FPGA. Utilizando estos ficheros se

puede realizar la verificación del diseño final mediante una simulación temporal

HDL post-síntesis.

4. Programming File Generation – Generación del archivo de programación: Finalmente en esta fase se genera el fichero BIT de configuración de la FPGA.

Programación

Una vez que se genera el archivo BIT se procede a configurar el dispositivo. Durante

la configuración se descargan los archivos de programación desde una computadora anfitriona al dispositivo FPGA de Xilinx.

2.5 Introducción a la codificación de predicción lineal (LPC) de la voz

humana

Este método de predicción lineal se utiliza para el análisis y síntesis de la voz humana. Este modelo supone que el tracto vocal se puede describir de la siguiente forma [3]:

Frecuencia del Pitch

Generador

de pulsos

periódicos

Selector de voz con

o sin sonido

Filtro IIR

todo polos

Señal

de voz

Generador

de Ruido

Blanco

Figura 2.7: Modelo del tracto vocal [3]

El filtro lineal IIR todo polos, tiene la siguiente función de transferencia:

H ( z) =

G

M

1 − ∑ ai z

i =1

(1)

−i

15

Donde i es el número de polos, G la ganancia del filtro y ai son los parámetros de los polos.

A este filtro se le conoce también como filtro LPC (Lineal Predictive Coding) [18].

Existen dos funciones de excitación mutuamente exclusivas que modelan los sonidos

con voz (periódica con periodo igual al pitch) y los sonidos sin voz (ruido blanco). Se supone que cada muestra es una combinación lineal de las muestras anteriores. Los coeficientes del filtro se calculan para minimizar el error cuadrático entre la muestra actual y su

predicción.

Se trabaja sobre bloques de 20 ms de voz, sobre lo que se conoce como modelo corto,

donde las características de la voz se suponen que no varían con el tiempo en intervalos pequeños. Esos bloques se analizan para determinar los coeficientes de predicción. Estos se

cuantifican y se envían al receptor junto con otros parámetros.

Los parámetros que se envían son: los coeficientes del filtro (coeficientes de predicción y ganancia), la intensidad de la excitación, un bit que indica si la excitación es un sonido sin voz ó un sonido con voz, y, en caso de ser este último, la frecuencia de la

excitación del formante (pitch) [3].

Figura 2.8: Esquema de codificación LPC [3]

Con esta información el decodificador puede reconstruir la señal fuente, la cual hace

pasar por el filtro, obteniéndose la voz sintetizada.

En el decodificador, los sonidos con voz se obtienen al pasar una serie de impulsos

periódicos con la misma frecuencia e intensidad de la formante por el filtro (caracterizado

por los coeficientes de predicción). Los sonidos sin voz se obtienen al pasar por el filtro

ruido aleatorio con la amplitud de la excitación [3].

16

Figura 2.9: Esquema de decodificación LPC [3]

Típicamente, el periodo del pitch requiere 6 bits y el parámetro de la ganancia se

puede representar con 5 bits. Los coeficientes de predicción requieren entre 8 y 10 bits por

coeficiente para una representación precisa. Si se utiliza un modelo de décimo orden el número de bits asignado por segmento es 82, con segmentos de 20ms se obtiene un bit rate de

4,6 kbps que es muy bajo con respecto a PCM (64Kbps), donde se observa la compresión

que se obtiene con este procesamiento [3] .

Hoy día se puede codificar la voz con LPC a velocidades entre 2.4 y 4.8 kbps con una

señal de voz reconstruida con una calidad razonable. LPC basa su funcionamiento en dos

tipos de sonidos: con voz y sin voz, sin embargo otros tipos de sonidos existentes no se

pueden reproducir con este método, resultando esto en la producción de una voz artificial y

es imposible reconocer, a partir de la voz sintetizada, a la persona que la origina [10].

CAPÍTULO 3: Planteamiento de un procedimiento basado en

herramientas de código abierto

En la sección 1.4, se presentó el flujo de diseño de los FPGA de Xilinx. Este procedimiento presenta ciertamente varias ventajas:

•

Estabilidad: las herramientas que se utilizan han sido ampliamente probadas y

se encuentran en una etapa estable donde es difícil encontrar un error de programación y el fabricante provee soporte en caso de encontrar alguna falla.

•

Optimización: las herramientas fueron diseñadas por el fabricante para obtener

el máximo provecho de las capacidades del FPGA.

Sin embargo, está claro que el procedimiento fue concebido para FPGAs de la marca

Xilinx, de donde surgen las siguientes desventajas:

•

Falta de compatibilidad y portabilidad: las herramientas se diseñaron específicamente para FPGAs de Xilinx, durante las diferentes etapas del flujo se generan archivos con formatos propietarios, esto impide que los resultados se

puedan utilizar con otras herramientas EDA de otro fabricante y que los diseños no se puedan redireccionar a otras marcas o tecnologías.

•

Falta de flexibilidad: no es posible modificar las herramientas para obtener

nuevos resultados durante el flujo de diseño. Desde el punto de vista académico no permite que la Universidad desarrolle y aporte conocimientos en esta

área. El estudiante aprende solo a desarrollar circuitos digitales para FPGAs

de Xilinx.

A partir de estas desventajas se plantea un procedimiento para diseño e implementación de circuitos digitales concebido en forma generalizada, en el cual sea posible seleccionar la tecnología en la cual se va a implementar el diseño y que los resultados obtenidos

durante el proceso sean estándares de la industria que provean de portabilidad y flexibilidad. Además este procedimiento debe permitir que el estudiante pueda realizar modificaciones y mejoras a las herramientas.

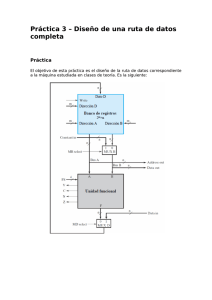

Bajo estas ideas se presenta el siguiente flujo de diseño:

17

18

Creación del Diseño

Compilación

(Icarus Verilog)

Simulación Funcional

(Icarus Verilog - GTK Wave)

Síntesis

(Icarus Verilog)

VLSI

ASIC’s

CPLD

FPGA

Xilinx

Altera, Amtel,

Actel,Lattice,

otros

Simulación Lógica

(Icarus Verilog / GTK Wave)

Implementación

(Xilinx WebPack)

Verificación Temporal

(GTK Wave)

Programación

(Xilinx WebPack)

Verificación en circuito

Figura 3.1 Flujo de diseño basado en herramientas EDA de código abierto

El flujo se inicia con una etapa de diseño, compilación y simulación funcional. Se

crea un modelo ideal independiente de la tecnología donde vaya a implementar el circuito

digital. En la etapa de síntesis se presenta la principal característica del flujo, donde es posible seleccionar la tecnología para implementar el proyecto. En esta etapa de síntesis se

decide la tecnología en la que se va a implementar el proyecto y se realiza el proceso mediante las especificaciones de la tecnología seleccionada.

Una vez que se obtenga la síntesis del diseño, se continuará con los pasos necesarios

para la implementación física que dependerá de la tecnología seleccionada.

19

Como se observa en la figura 3.1, se seleccionaron dos herramientas EDA para el desarrollo de este flujo: Icarus Verilog y GTKWave. Estas herramientas se seleccionaron ya

que satisfacían las necesidades del procedimiento planteado.

Icarus Verilog es una herramienta de simulación y síntesis de Verilog, lenguaje de

HDL estándar (IEEE-1364). Para el proceso de síntesis utiliza un formato estándar llamado

EDIF independiente de la tecnología. También permite la generación de archivos VCD, un

formato estándar especificado en IEEE-1364 para análisis de modelos de simulación de Verilog.

GTKWave es un analizador de formas de ondas. Permite visualizar las formas de ondas de simulaciones en diferentes formatos, como el formato VCD. Esta herramienta complementa a Icarus Verilog para simulaciones funcionales, lógicas y temporales.

Ambas herramientas son de código abierto y están asociadas al proyecto de herramientas EDA open source: gEDA. Está condición da la libertad a la UCR para modificar y

mejorar las herramientas con el fin de conseguir una mayor eficiencia y aportar en la automatización del desarrollo de circuitos digitales.

Ambas herramientas, se encuentran disponibles para: Windows, Linux y otras plataformas.

Sin embargo estas herramientas poseen ciertas debilidades como toda herramienta de

código abierto:

•

Estas herramientas no poseen soporte y se utilizan bajo propio riesgo.

•

No están completamente terminadas y es posible encontrar errores de programación.

Este proyecto utiliza las herramientas de forma exhaustiva para verificar que tienen la

capacidad para desarrollar circuitos digitales de cualquier tipo y tamaño. Para cumplir con

este propósito se seleccionó el desarrollo de un codificador/decodificador de voz que utiliza

el modelo de predicción lineal de la voz humana. Esta aplicación contaba con las condiciones necesarias de tamaño y complejidad para estresar las herramientas y revelar sus limitaciones.

20

Como primer paso, en este proyecto se utilizó este procedimiento y las herramientas

para la tecnología FPGA de Xilinx para comprobar que se puede llegar a resultados equivalente a los obtenidos con las herramientas propias del fabricante. En lo posterior, se presentan los resultados obtenidos en cada etapa del procedimiento y que permitieron elaborar la

guía presentada en el apéndice E. Esta guía documenta con detalle cada paso del flujo y el

uso de las herramientas Icarus Verilog y GTKWave. Además se explican las limitaciones y

las soluciones a los errores que se pueden presentar durante el proceso.

CAPÍTULO 4: Diseño del codificador/decodificador de voz

En este capítulo se presenta en alto nivel la arquitectura del codificador/decodificador

de voz que se diseñó para ejecutar el procedimiento planteado. Se revisan las características, los componentes y los flujos principales del diseño. Para mayor detalle se puede revisar el apéndice A y los archivos de Verilog adjuntados.

4.1 Descripción general

Se diseñó un codificador/decodificador de voz, que permite realizar grabaciones de

voz por ocho minutos y hacer reproducciones mediante dos tipos de codificaciones: PCM y

codificación predictiva lineal (LPC). La voz es filtrada mediante un filtro pasivo RC de un

polo para limitar el ancho de banda y muestreada de forma uniforme a una frecuencia de

muestreo de 8kHz (satisface el teorema de Nyquist). Se utilizaron 14 bits para la conversión

analógica-digital y las muestras se almacenaron en una memoria RAM dinámica.

Para realizar la codificación predictiva lineal se utilizaron tramas de voz de 20 milisegundos y diez coeficientes de predicción lineal. Todos los cálculos se realizan en punto flotante en precisión simple (32bits) bajo el estándar IEEE 754.

Para la reproducción se utilizaron 12 bits para la conversión digital-analógica y un retenedor de orden cero.

4.2 Componentes

El codificador/decodificador de voz posee los siguientes componentes:

•

Pre-amplificador programable, modelo LTC6912-1, marca Linear Technology.

•

Convertidor analógico-digital, modelo LTC1407A-1, marca Linear Technology.

•

Convertidor digital-analógico, modelo LTC2624, marca Linear Technology.

•

Memoria RAM dinámica, modelo MT46V32M16, marca Micron.

•

Oscilador de reloj, modelo SG-8002JF, marca EPSON.

•

FPGA, modelo XC3S1600E-FG320-4, marca Xilinx

21

22

Todos estos elementos se encuentran interconectados en la tarjeta de desarrollo: Spartan-3E

Starter-kit de Xilinx.

Dentro del FPGA se desarrollaron los siguientes circuitos digitales que permitieron

verificar el procedimiento planteado:

Para control de interfaces y almacenamiento

Controlador A/D

Controlador

Controlador de

Controlador de Re-

Memoria RAM está-

D/A

Memoria

producción

tica 160X32

Coeficientes R

Coeficientes LPC

Para codificación/decodificación predictiva lineal

Controlador de Codifi-

Sonido con/sin

Detección del

cación

voz

pitch

Filtro de análisis

Filtro de síntesis

Para cálculo en punto flotante en 32 bits (FPU)

Sumador/Restador

Multiplicador

Divisor

Raíz Cuadrada

Tabla 4.1 Circuitos diseñados para el codificador/decodificador de voz

A continuación se presenta un diagrama de bloques del diseño:

23

Figura 4.1 Diagrama de bloques del diseño

4.3 Diagrama de estados general

A continuación se presenta el diagrama estado general del codificador/decodificador

de voz:

24

S0: Estado Inicialización

S1: Estado Listo

S2: Estado Grabando

S3: Estado Codificacion/Decodificación Automática

S4: Estado Reproducción PCM Rotativa

S5: Estado Reproducción LPC Rotativa

Reset

S0

S1

S3

Listo

no

si

Grabar

?

si

Memoria

Llena

?

S2

no

no

Reproducir

?

no

Continuar

?

si

si

Codificar

?

si

no

S4

Continuar

?

no

S5

si

Continuar

?

si

no

Figura 4.2 Diagrama de estado general del diseño

La señal Reset inicializa el sistema y se entra al estado S0 donde se inicializan las

máquinas de estado y se configuran los dispositivos externos al FPGA. Cuando se termina

esta fase se pasa en forma incondicional al S1 donde el sistema se encuentra listo para operar y se indica con la señal Listo. En este estado se revisan las señales Grabar y Reproducir. Si la señal Grabar está en alto, se pasa al estado S2 donde se graba y almacena las

muestras de voz hasta que se llene la memoria o que se finalice la grabación bajando la señal Grabar. Inmediatamente se continúa al estado S3 donde se realiza una codificación

predictiva lineal de las muestras, seguidamente se decodifican y se almacenan listas para

reproducirse.

Si la señal Reproducir está en alto, se revisa la señal Codificar. Si la señal Codificar

esta en bajo, se pasa al estado S4 donde se reproduce la voz con la codificación PCM hasta

que la señal Reproducir baje. Si la señal Codificar está en alto, se pasa al estado S5 donde

25

se reproduce la voz con la codificación LPC hasta que la señal Reproducir baje. Se reproduce en forma repetida hasta que la señal Reproducir baje.

La señal Grabar tiene prioridad sobre la señal Reproducir si ambas están en alto al

mismo tiempo. No es posible grabar y reproducir al mismo tiempo.

4.4 Descripción de los circuitos digitales

A continuación se describen los circuitos digitales que se diseñaron:

Para control de interfaces y almacenamiento:

Controlador del convertidor analógico-digital

Consiste en una máquina de estado y una asignación de registros, que inicializa y

configura el pre-amplificador programable y el convertidor analógico-digital. Controla la

frecuencia de muestreo a 8kHz de la señal de voz entrante y posee la interfaz para introducir las muestras de voz de 14 bits del convertidor A/D al FPGA.

Controlador del convertidor digital-analógico

Consiste en una máquina de estado y una asignación de registros, que inicializa y

configura el convertidor digital-analógico. Controla la frecuencia de reproducción a 8kHz

de la voz saliente y posee la interfaz para llevar las muestras de voz de 12 bits del FPGA al

convertidor D/A.

Controlador de memoria RAM dinámica

Consiste en una máquina de estado y una asignación de registros, que inicializa y

configura la memoria RAM dinámica para el almacenamiento de muestras de voz. Realiza

el proceso de inicialización de la memoria. Controla los periodos de refrescamiento de la

memoria. Permite realizar escrituras y lecturas de datos, solo un dato a la vez.

Controlador de reproducción

Consiste en una máquina de estado y una asignación de registros, posee la interfaz

con las señales de control disponibles para el usuario. Se encarga de almacenar las muestras

que provee el controlador de convertidor A/D en el banco 1 de la memoria RAM a través

del controlador de memoria durante la grabación. Controla el controlador de codificación

26

para que se ejecute el procedimiento de predicción lineal. Durante la reproducción según la

codificación seleccionada lleva las muestras del banco 1 (PCM) o 2 (LPC) de la DRAM al

controlador de convertidor D/A.

Memoria RAM estática 160X32

Consiste en una memoria Ram estática de 160x32, que permite el almacenamiento

temporal de 160 muestras de voz en 32 bits, que corresponde a la trama de voz que es analizada. Posee una escritura sincrónica y una lectura asincrónica.

Para codificación/descodificación predictiva lineal:

Controlador de codificación.

Consiste en una máquina de estado y una asignación de registros, que convierte tramas de voz de 20 ms (160 muestras a 8kHz) almacenadas en la memoria DRAM en 14 bits,

al formato de punto flotante en 32 bits. Se encarga de mover cada trama de voz convertida

a la memoria RAM estática para aplicarle el procedimiento LPC. Controla las máquinas de

estado para realizar el procedimiento de codificación predictiva lineal, tanto la codificación

como la decodificación.

Sonido con/sin voz

Consiste en una máquina de estado y una asignación de registros, que analiza la trama

de voz en la memoria RAM estática con el procedimiento llamado “Cruce por cero” para

determinar si la muestra de voz se caracteriza como un sonido con voz o sin voz. Se utiliza

un umbral de 25 cruces para su identificación. Si el resultado es un sonido con voz, controla la máquina de estado “Detección del pitch”.

Detección del pitch

Consiste en una máquina de estado y una asignación de registros, que analiza la trama

de voz en la memoria RAM estática con el procedimiento llamado AMDF (Average Magnitude Difference Function) para determinar el periodo del pitch de la muestra de voz.

Coeficientes R: Cálculo de los coeficientes de autocorrelación

27

Consiste en una máquina de estado y una asignación de registros, que analiza la trama

de voz en la memoria RAM estática y calcula los coeficientes de autocorrelación. Se obtienen 11 coeficientes. Esta máquina controla la máquina de estado “Coeficientes LPC”.

Coeficientes LPC: Cálculo de los coeficientes de predicción lineal

Consiste en una máquina de estado y una asignación de registros, que utiliza los coeficientes R de autocorrelación y calcula los 10 coeficientes de predicción lineal mediante

el método Levinson-Durbin.

Filtro de análisis

Consiste en una máquina de estado y una asignación de registros, constituye el filtro

de análisis del método LPC. Filtra la trama de voz en la memoria RAM estática y obtiene el

error y la ganancia a partir de los coeficientes de predicción lineal.

Filtro de síntesis

Consiste en una máquina de estado y una asignación de registros, constituye el filtro

de síntesis del método LPC. Utiliza los parámetros obtenidos para decodificar la trama de

voz que fue analizada. Se construye el filtro mediante los coeficientes LPC y la ganancia.

La entrada del filtro puede consistir en ruido gaussiano que se encuentra pre-almacenado en

una ROM o una señal de pulsos con la frecuencia del pitch. La selección de la entrada se

realiza con la detección de un sonido con/sin voz. Convierte los resultados obtenidos de 32

bits a 14 bits y lo almacenada en el banco 2 de la DRAM para reproducción.

Para cálculo en punto flotante en 32 bits:

Sumador/Restador/Multiplicador/Divisor/Raíz Cuadrada

Consisten en una máquina de estado y una asignación de registros por cada operación

aritmética, que ejecuta la operación correspondiente de dos operandos en 32 bits, excepto la

raíz cuadrada que ocupa solo un operando de 32 bits. Se utiliza el estándar IEEE754 de

precisión simple para realizar el cálculo de los resultados. El resultado es truncado y se da

en el mismo formato que los operandos. Se puede ejecutar una operación a la vez. Las operaciones que generan overflows o los underflows se resuelven dando como resultado el numero más grande y el numero más pequeño respectivamente que permite el estándar. En el

28

caso de la división por cero se resuelve dando como resultado el número más grande posible.

4.5 Arquitectura de las máquinas de estado y de la asignación de registros

Para el diseño de las máquinas de estado se utilizaron dos tipos de arquitectura: un

flip-flop por estado (“One-hot”) y microprogramación. La arquitectura micro-programada

se utilizó para los circuitos cuya frecuencia de reloj no era importante como el controlador

A/D y D/A ya que la frecuencia de muestreo es muy baja. Para los demás circuitos se utilizó la arquitectura one-hot para obtener una frecuencia de reloj alta para el procedimiento de

predicción lineal a cambio de más flip-flops por máquina y mayor consumo de potencia.

Entrada n

Estado n

Entrada 1

Estado 1

Entrada 0

Estado 0

Para la asignación de registros (datapath), se usó la siguiente arquitectura:

Figura 4.3 Arquitectura de la asignación de registros

4.5.1 Protocolo de comunicación entre circuitos

Para la comunicación entre circuitos digitales se utilizó un Full Handshake completamente sincrónico con el reloj de referencia como se muestra a continuación:

29

Figura 4.4 Protocolo de comunicación entre los circuitos

Las máquinas se pueden utilizar si la señal listo está en alto. Se inician con la señal

inicio. La máquina iniciada indica su estado ocupado bajando la señal listo y la máquina

que la controla puede bajar la señal inicio. Cuando la máquina termina lo indica subiendo

listo, todos los cambios se realizan en los flancos negativos del reloj de referencia.

4.5.2 Protocolo de cambio de estado y asignación de estado

Se definió la siguiente convención: Todas las máquinas de estado cambian de estado

en los flancos positivos del reloj de referencia y las asignaciones de los registros se realizan

en los flancos negativos de reloj. A continuación se muestra la convención definida:

Figura 4.5 Protocolo de cambio de estado y asignación de estado

CAPÍTULO 5: Compilación y Simulación Funcional

En este capítulo se explica la forma en que se realizó la compilación y simulación

funcional de los circuitos digitales descritos en Verilog por separado y después en conjunto.

5.1 Descripción en Verilog

El diseño del codificador/decodificador de voz se describió en Verilog. La descripción se realizó en forma conductual y de forma jerárquica. Cada circuito se describió, en

general, utilizando dos módulos de la siguiente forma:

Figura 5.1 Estructura de la descripción en Verilog para los circuitos diseñados

El primer módulo consiste en la máquina de estados con la arquitectura correspondiente y el segundo con la asignación de registros. A continuación se presenta los nombres

de módulos en Verilog:

Nombre del Circuito

Módulos en Verilog

Controlador A/D

AD_controlador.v

AD_registros.v

Controlador D/A

DA_controlador.v

DA_registros.v

Controlador de Memoria

mem_controlador.v

mem_registros.v

Controlador de Reproducción

repro_controladorv2.v

repro_registros.v

Controlador de Codificación

CODE_controlador.v

CODE_registros.v

Sonido con/sin Voz

Cruce_controlador.v

Cruce_registros.v

Detección del Pitch

Pitch_controlador.v

Pitch_registros.v

Coeficientes R

R_controlador.v

R_registros.v

Coeficientes LPC

C_controlador.v

C_registros.v

Filtro de Análisis

FG_controlador.v

FG_registros.v

Filtro de Síntesis

FPR_controlador.v

FPR_registros.v

Sumador/Restador

microcontrolador.v

asignacion_registros.v

Multiplicador

multiplicador_controlador.v

multiplicador_registros.v

Divisor

divisor_controlador.v

divisor_registros.v

30

31

Raíz Cuadrada

raiz_controlador.v

ROM de Ruido

ruido.v

Memoria RAM Estática 160x32

ram.v

raiz_registros.v

Tabla 5.1 Nombre de los módulos en Verilog para cada circuito

La estructura jerárquica que se estableció fue la siguiente:

Controlador A/D

Controlador D/A

Controlador de

Memoria

Controlador de

Memoria

Controlador de

Reproducción

Controlador de

Codificación

Filtro de análisis

Módulo principal

Módulo

Coeficientes R

y LPC

Módulo FPU

Sumador/

Restador

Multiplicador

Divisor

Raíz Cuadrada

Coeficientes R

Coeficientes

LPC

Módulo Sonido

y Pitch

Sonido con/sin

Voz

Detección del

Pitch

Filtro de síntesis

ROM Ruido

Figura 5.2 Estructura jerárquica establecida para el proyecto

En un principio la descripción en Verilog se realizó con las reglas básicas que se deben respetar para cualquier proceso de síntesis en Verilog. A continuación se mencionan [6]:

•

No modificar una variable en dos procesos diferentes.

•

En una asignación procedural, todas las variables de las que dependa la asignación

deben aparecer en la lista de sensibilidad, para evitar inferencia equivocada de latches.

•

No realizar asignaciones al mismo tiempo donde una depende de la otra.

•

No se admiten procesos initial.

•

No se admiten algunos operadores como la división.

En esta etapa se utilizaron estas reglas con el fin de asegurar una síntesis exitosa. Pos-

teriormente se encontraron problemas con el sintetizador de Icarus Verilog donde se tuvo

que modificar la descripción en Verilog y el diseño para resolverlos. La estructura jerárquica establecida permitió aislar fácilmente los problemas.

32

En el capítulo 6, se hace una caracterización del sintetizador en Icarus Verilog y se

discute las limitaciones y problemas que se encontraron en la herramienta.

5.2 Etapa de Compilación y Simulación Funcional

En esta etapa se comprobó en forma individual y grupal que los módulos en Verilog

no tuvieran ningún error de sintaxis y alguna directiva no soportada por Icarus Verilog. Para este proyecto se utilizó la versión 8.6 para Windows. Todos los comandos se ejecutaron

en la consola, como por ejemplo para la compilación del circuito completo:

%iverilog –o REP.vvp –c REP.prj

Donde iverilog invoca a la herramienta Icarus Verilog, REP.prj es el nombre del archivo

con las direcciones a los archivos fuente .v y la opción -o define el nombre del archivo que

va a contener el ejecutable de simulación que este caso se va a llamar REP.vvp.

5.2.1

Simulación funcional

La simulación funcional verifica que la descripción en Verilog del circuito digital sea

la correcta y que su comportamiento funcional satisface las especificaciones. Para realizar

las simulaciones funcionales se utilizó el siguiente esquema:

Figura 5.3 Esquema jerárquico para simulación funcional

Se creó un módulo llamado banco de pruebas para cada circuito diseñado. De esta

forma todas las sentencias que tenían que ver con la simulación quedaron definidas dentro

de este módulo y posteriormente se utilizó solo el módulo con el diseño para el proceso de

síntesis.

Cada banco de pruebas posee un conjunto de estímulos que simula el entorno alrededor del circuito. Se ejercitó cada circuito por separado para comprobar su funcionalidad de

33

forma ideal ya que no emplearon retardos temporales, esto para que las simulaciones durante la implementación coincidieran.

Para los circuitos de control de interfaces y almacenamiento, los bancos de pruebas

se desarrollaron de forma tal que simularan el comportamiento del dispositivo externo. En

el caso de la memoria DRAM se utilizaron las descripciones en Verilog que provee el fabricante, Micron, que facilitó y aseguró la simulación funcional del controlador de memoria.

Para cada circuito se obtuvo un archivo VCD y se utilizó para comprobar que los

cambios de estados y las asignaciones a registros fueran correctos en la simulación.

Figura 5.4 Simulación funcional del controlador de memoria DRAM en GTKWave

Para los circuitos de cálculo en punto flotante en 32 bits (FPU) se emplearon pruebas

para ejecutar operaciones con casos esquinas básicas y conjuntos de operaciones aleatorias.

No se hizo una validación exhaustiva puesto que se salía de los objetivos del proyecto.

Para las pruebas con operaciones aleatorias se utilizó Matlab para generar los archivos

binarios en precisión simple y se consideró como el resultado ideal. Sin embargo los resultados de Matlab eran redondeados a diferencia de los circuitos diseñados cuyo resultado es

truncado. Por lo que en los resultados de las simulaciones se aceptaron errores por redondeo con respecto al resultado ideal (Matlab). A continuación se muestra los resultados de

las simulaciones para el divisor:

34

Figura 5.5 Simulación funcional del divisor de 32bits

Similarmente, para los circuitos de codificación/decodificación predictiva lineal se desarrollaron bancos de pruebas que utilizaban tramas de 20ms de señales senoidales.

Además de las simulaciones individuales, se desarrollaron dos simulaciones intermedias:

•

Los circuitos de predicción predictiva lineal en conjunto para comprobar el algoritmo LPC.

•

Los circuitos de interfaz y almacenamiento en conjunto para comprobar la grabación, almacenamiento y reproducción.

Finalmente se realizó una simulación del circuito completo para comprobar el funcionamiento global del sistema. Para este tipo de simulaciones se tuvo que limitar los niveles

en las jerarquías de los módulos que se iban a acceder para la creación del archivo VCD, ya

que el archivo se volvía muy grande debido a la duración de la simulación y la cantidad de

señales por jerarquía. También, para disminuir el tiempo y tamaño de la simulación se utilizaron tramas de voz pequeñas, se aumentó la frecuencia de muestreo y solo se simuló una

trama a la vez por simulación. Según el tamaño del archivo VCD (entre 0.5 y 1 GB), así duraba la aplicación GTKWave en abrirlo y se veía limitado por la memoria de la computadora donde se corría la aplicación (para el proyecto se utilizó una computadora portátil con 1

GB de memoria RAM, un procesador Pentium M de 1.8 GHz).

35

Figura 5.6 Simulación funcional del codificador/decodificador de voz en GTKWave

Estas etapas de descripción, compilación y simulación funcional se realizaron reiteradamente debido a los cambios ocasionados por el proceso de síntesis.

CAPÍTULO 6: Síntesis en Icarus Verilog

En este capítulo se describe el proceso de síntesis con Icarus Verilog y específicamente para la arquitectura Virtex de Xilinx para la cual se realizó este proyecto. Se presentan las características del sintetizador y

las limitaciones que se encontraron en la

herramienta. Se hace referencia la implementación sobre el FPGA SPARTAN-3E y la tarjeta de desarrollo SPARTAN-3E Starter-Kit Board.

6.1 Descripción del proceso de síntesis con Icarus Verilog

La síntesis es el proceso de mapear y optimizar una descripción en HDL de alto nivel

a una tecnología de compuertas (compuertas lógicas, latches, flip-flops, etc.). A continuación se presenta este proceso en general de síntesis para la herramienta Icarus Verilog que

se definió como resultado de este proyecto:

Figura 6.1 Proceso de Síntesis con Icarus Verilog

Descripción en HDL: consiste en la descripción del diseño en Verilog. Se debe utilizar un subconjunto de instrucciones soportadas por el sintetizador de Icarus Verilog.

Librería de tecnología: el sintetizador de Icarus Verilog posee información acerca de

la descripción funcional de celdas para la arquitectura Virtex (Xilinx), Virtex2 (Xilinx) y

LPM (estándar genérico). El fabricante de la arquitectura provee documentación de la librería y de las celdas disponibles. En este caso, el sintetizador es limitado y conoce un subcon36

37

junto de las celdas de la arquitectura por lo que el resultado no siempre está optimizado.

También no posee información temporal de la arquitectura por lo que no se obtienen resultados de análisis temporal.

Restricciones y Parámetros: Es información adicional acerca de las características físicas del diseño, como asignación de pines, estándar de voltaje de salida y entrada, periodo

de reloj, ubicación de celdas, entre otros. Esta información es provista por el fabricante de

la arquitectura. Icarus Verilog permite indicar ciertos parámetros y restricciones en forma

limitada directamente en el archivo de Verilog.

Netlist: es un archivo de texto que describe los componentes y la conexión física entre

ellos para la implementación del diseño y es el resultado final del proceso. Icarus Verilog

utiliza el formato estándar EDIF, versión 2. Debido a las limitaciones de Icarus Verilog y a

las características propias del circuito digital, es posible que el archivo EDIF resultante sea

incompleto y que sea necesario editarlo para completar la síntesis. Esta edición principalmente se hace para agregar parámetros y restricciones no soportados.

6.2 Descripción del proceso de síntesis para la arquitectura Virtex

6.2.1

Características del sintetizador de Icarus Verilog

La herramienta Icarus Verilog posee un compilador para sintetizar un código en Veri-

log y transformarlo a formato EDIF.

El compilador trabaja a nivel de sentencias always, asignaciones continuas y compuertas lógicas en Verilog. Por esta razón, estructuras como for, task, while, wait, repeat,

initial no son sintetizables. Aún con estas limitaciones, se puede sintetizar diseños jerárquicos con circuitos combinacionales y secuenciales. Esto debido a que la sentencia always

modela casi todo tipo de lógica digital. Por defecto se intenta sintetizar todas las instrucciones, sin embargo mediante directivas se identifica las estructuras que se desean sintetizar y

cuales no.

Desde el punto de vista formal de lenguaje, se probó con la descripción en Verilog del

diseño que Icarus Verilog sintetiza para la arquitectura Virtex:

38

•

Procesos always.

1. Operadores binarios aritméticos: suma (+) y resta (-).

2. Operadores relacionales: >=, <=, !=, ==.

3. Operadores lógicos: !, &&, ||.

4. Operadores lógicos de bit ~, &, |, ^.

5. Concatenaciones {,}.

6. Desplazamiento hacia la izquierda o derecha, con adición de ceros.

7. Estructuras de control: if-else y case (con anidaciones).

8. Asignaciones procedurales no bloqueantes.

9. Eventos de nivel y de flanco positivo.

•

Asignaciones continuas:

1. Operadores binarios aritméticos: suma (+) y resta (-).

2. Operadores relacionales: >=, <=, !=, ==.

3. Operadores lógicos: !, &&, ||.

4. Operadores lógicos de bit: ~, &, |, ^.

5. Concatenaciones: {,}.

6. Desplazamiento hacia la izquierda o derecha, con adición de ceros.

7. Condicional: ?: .

•

Compuertas lógicas: and, or, xor, nor, xnor, buf, not.

•

Utilización de parámetros.

•

Utilización de variables tipo: reg, wire, input, output, inout.