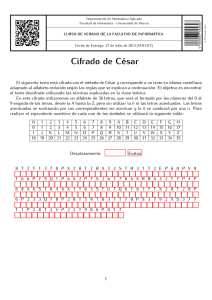

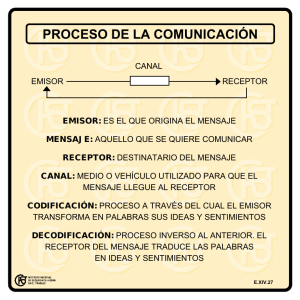

Sistema de comunicación vocal con cifrado analógico y digital

Anuncio