Formulación Sistemas Secuenciales

Anuncio

UNIVERSIDAD TECNICA FEDERICO SANTA MARIA

DEPARTAMENTO DE ELECTRONICA

ELO211 Sistemas Digitales

9.5. Tipos de máquinas secuenciales

Si bien existen innumerables formas que pueden tomar los diagramas de estados, pueden describirse

algunos tipos que se presentan más a menudo en electrónica.

a) Máquinas que analizan secuencias de largo fijo con un recorrido fijo. Por ejemplo: tomar 5 valores de

la secuencia y tomar una acción, de acuerdo a los valores.

b) Máquinas que analizan secuencias de largo fijo con un recorrido fijo con reintento en caso de falla. Si

una subsecuencia no es correcta, vuelven al estado inicial; o a un estado previo.

c) Reconocedores continuos. Se genera una salida cada vez que se detecta una secuencia dada. En estas

máquinas, cada estado recuerda una secuencia previa de la entrada. En este caso, se habla de estado

inicial sólo cuando la máquina comienza a funcionar.

9.6

Síntesis de Diagramas de Estado. Modelado

Se desea obtener el diagrama de estados a partir de una descripción en lenguaje natural.

Nuestro lenguaje común suele ser impreciso y a veces redundante. Por esta razón es conveniente emplear

las construcciones estructuradas de los lenguajes de programación.

En general, el paso de una descripción en lenguaje natural a la tabla de estados, se efectúa por pasos

tentativos, hasta asegurar que el modelo formal obtenido cumple las especificaciones dadas.

Veremos algunos ejemplos.

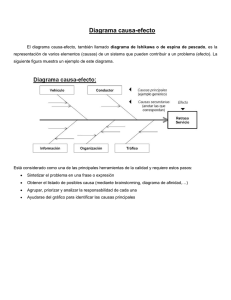

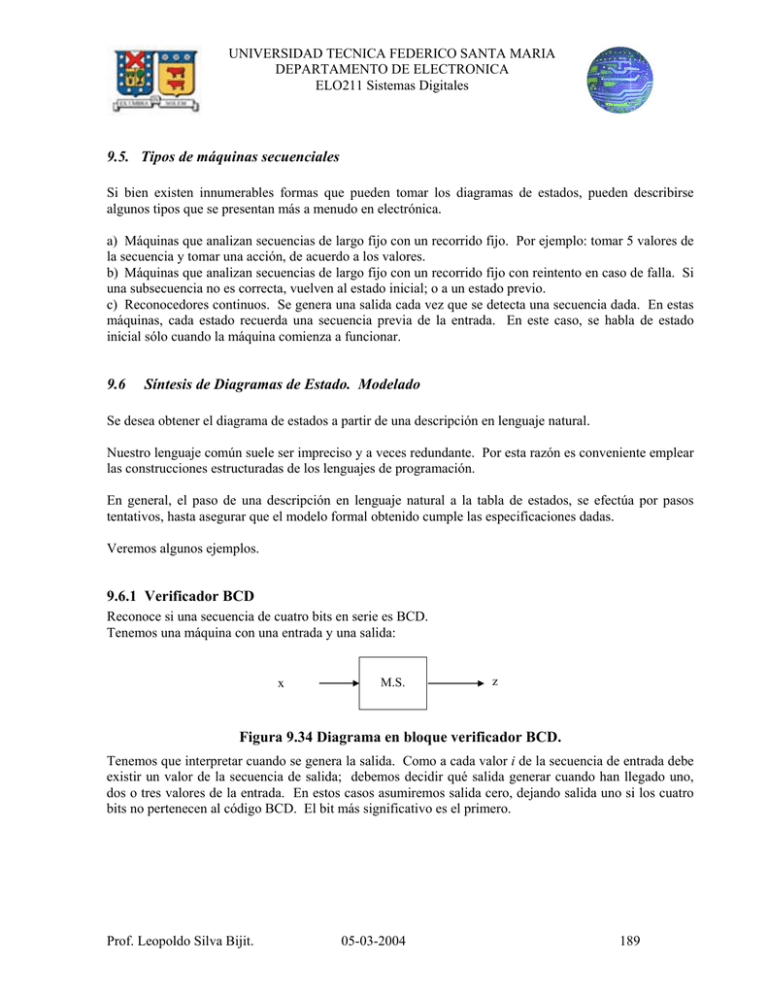

9.6.1 Verificador BCD

Reconoce si una secuencia de cuatro bits en serie es BCD.

Tenemos una máquina con una entrada y una salida:

x

M.S.

z

Figura 9.34 Diagrama en bloque verificador BCD.

Tenemos que interpretar cuando se genera la salida. Como a cada valor i de la secuencia de entrada debe

existir un valor de la secuencia de salida; debemos decidir qué salida generar cuando han llegado uno,

dos o tres valores de la entrada. En estos casos asumiremos salida cero, dejando salida uno si los cuatro

bits no pertenecen al código BCD. El bit más significativo es el primero.

Prof. Leopoldo Silva Bijit.

05-03-2004

189

UNIVERSIDAD TECNICA FEDERICO SANTA MARIA

DEPARTAMENTO DE ELECTRONICA

ELO211 Sistemas Digitales

Verificador BCD:

estado_inicial();

while(1)

{ lea primer valor de xi ; z=0;

lea segundo valor de xi ; z=0;

lea tercer valor de xi ; z=0;

lea cuarto valor de xi ;

if ( los últimos cuatro bits de xi es cifra BCD)

then z=0; else z:=1;

}.

La descripción en pseudo lenguaje es bastante útil para especificar con rigurosidad los requerimientos del

diseño.

El pseudo lenguaje es similar a un lenguaje de programación estructurado, en el cual las acciones

describen los eventos asociados a las máquinas digitales.

Estado Inicial

a

1/0

0/0

0/0

b

0/0

1/0

d

0/0

e

h

0/0

0/0

1/0

1/0 0/0

1/0

0/0

1/0

g

f

0/0

1/0

j

i

c

l

k

1/0 0/0

1/0 0/0

0/0

1/0

n

m

1/0 0/1

1/0

1/1 0/1

o

1/1 0/1

1/1

Figura 9.35 Diagrama de estados verificador BCD.

Cada estado representa una subsecuencia previa de la entrada. Por ejemplo, en l se ha recibido la

secuencia 100. En d se ha recibido 00.

Este primer diseño es muy sistemático; se forma un árbol de decisión. De cada estado, se pasa a dos

próximos con entrada cero y uno respectivamente.

Estos problemas no tienen una solución única. Puede encontrarse un diagrama de estados más simple.

Por ejemplo:

Prof. Leopoldo Silva Bijit.

05-03-2004

190

UNIVERSIDAD TECNICA FEDERICO SANTA MARIA

DEPARTAMENTO DE ELECTRONICA

ELO211 Sistemas Digitales

a

1/0

0/0

b

e

1/0

0/0

φ/0

c

f

/0

φφφ/0

/0

1/0

g

φ/0

0/0

h

d

φ/0

φ/1

Figura 9.36 Diagrama de estados reducido del verificador BCD.

Se emplea φ para indicar que con entrada cero o uno, se pasa al próximo estado. Este segundo diagrama

requiere tres flip-flops para representar los estados. El anterior requiere 4 flip-flops para identificar 15

estados.

Existen procemientos sistemáticos para encontrar estados equivalentes y removerlos de los diagramas.

9.6.2. Reconocedor continuo

Se desea obtener el diagrama de estados de una máquina secuencial que produzca una salida alta cada vez

que se detecta la secuencia 0101 en la entrada; la salida debe ser cero en el resto de los casos.

Solución:

Si por ejemplo la entrada es: 0, 1, 0, 1, 0, 1, ...

la salida debe ser:

0, 0, 0, 1, 0, 1, ...

Tenemos:

reconocedor 0101:

estado_inicial(); i=0;

while( i<3) { lea(xi); zi=0; i ++;}

for(; ;i++)

{ lea(xi);

if ( (xi-3==0) && (xi-2==1) && (xi-1==0) && (xi==1) ) then zi=1; else zi=0 ;

}

Prof. Leopoldo Silva Bijit.

05-03-2004

191

UNIVERSIDAD TECNICA FEDERICO SANTA MARIA

DEPARTAMENTO DE ELECTRONICA

ELO211 Sistemas Digitales

A partir de un estado inicial A, se plantea la secuencia a reconocer:

A

B

C

0/0

D

1/0

0/0

1/1

Figura 9.37 Reconocedor de secuencia 0101.

Luego, lo que resta es completar las transiciones que faltan. Desde cada estado deben salir dos

transiciones; en este caso, sólo hay una entrada, y ésta puede tomar valores 0 y 1.

Ayuda conceptualizar el significado de los estados, del siguiente modo:

A:

inicial, se espera un cero.

B: después de haber aceptado un cero.

C: después de haber aceptado la secuencia 01.

D: después de haber aceptado la secuencia 010.

Observaciones:

Estando en D, si llega un cero, debe ir al estado B, pues ya tendría el primer cero de la secuencia.

Estando en B, debe permanecer en B mientras lleguen ceros.

Permanece en A, mientras lleguen unos.

Estando en C, si llega un uno, debe ir al estado inicial.

Estando en D, si llega un uno, se reconoce secuencia correcta; y debe ir a C. Ya que tiene los dos

primeros bits reconocidos.

Resulta el siguiente diagrama de estados:

1/0

0/0

1/0

A

0/0

B

B

1/0

C

0/0

D

1/1

0/0

Figura 9.38 Diagrama de estados completo del reconocedor continuo.

Prof. Leopoldo Silva Bijit.

05-03-2004

192

UNIVERSIDAD TECNICA FEDERICO SANTA MARIA

DEPARTAMENTO DE ELECTRONICA

ELO211 Sistemas Digitales

9.6.3.Reconocedor continuo con reintento en caso de falla

Diseñar máquina secuencial que reconozca con salida uno, cada vez que se presente en la entrada, la

secuencia de exactamente dos ceros, seguida de 10. En caso contrario debe generar salida cero.

Solución:

La siguiente secuencia de entrada:

debe generar la siguiente salida:

001001000010010...

000100100000001...

Un esquema de la “columna vertebral” del diagrama es:

1/0

A

0/0

B

0/0

1/0

C

D

0/1

Figura 9.39 Diagrama de estados inicial.

A, es el estado inicial: en él se espera por un cero.

Si en B o D falla la secuencia se retorna al estado inicial.

Estando en C, si llega un cero debe pasarse a un estado E; en el cual deben descartarse todos los ceros que

lleguen.

El diagrama completo:

0/0

1/0

E

1/0

1/0

A

0/0

B

0/0

1/0

0/0

C

1/0

D

0/1

Figura 9.40 Diagrama de estados completo.

9.6.4.Reconocedor continuo de códigos BCD válidos.

En este ejemplo se ilustra la importancia de darle un nombre simbólico adecuado a cada estado.

Si la entrada presente y las tres anteriores forman un código válido BCD, entonces la salida permanece en

0; en caso contrario la salida debe ser uno.

Solución:

El nombre del estado recuerda la secuencia previa de 3 bits de la entrada. Para construir el diagrama basta

obtener los estados próximos a cualquier estado.

Por ejemplo, a partir del 001, se llega a los estados 011 y 010, con entradas uno y cero respectivamente.

Prof. Leopoldo Silva Bijit.

05-03-2004

193

UNIVERSIDAD TECNICA FEDERICO SANTA MARIA

DEPARTAMENTO DE ELECTRONICA

ELO211 Sistemas Digitales

Esto se ilustra en el siguiente diagrama:

001

0

1

010

011

Figura 9.41 Estados siguientes al estado 001.

Los dos últimos bits de 001, forman los dos primeros de 011 y 010.

De esta forma es sencillo plantear, el diagrama completo:

0

000

1

0

1

001

100

0

0

010

1

0

1

1

011

0

101

1

110

0

1

0

111

1

Figura 9.42 Diagrama de estados completo, sin salida.

Para completar el diagrama deben indicarse las salidas asociadas a las transiciones.

Las secuencias: 1010, 1011, 1100, 1101, 1110, 1111 son las que tienen asociada una salida uno.

Prof. Leopoldo Silva Bijit.

05-03-2004

194

UNIVERSIDAD TECNICA FEDERICO SANTA MARIA

DEPARTAMENTO DE ELECTRONICA

ELO211 Sistemas Digitales

La función de salida puede describirse por la siguiente tabla de verdad, y con ésta completar el diagrama.

Estado

000

001

010

011

100

101

110

111

x

0

0

0

0

0

0

1

1

1

1

0

0

0

0

0

1

1

1

z

Figura 9.43 Tabla de verdad de la función de salida.

9.6.5. Del diagrama a la especificación.

Dado el siguiente diagrama de estados, describir qué efectúa la máquina.

Asumir 1 como estado inicial.

0/0

1/0

1

2

0/0

1/0

1/0

3

1/0

4

5

0/0

0/0

0/1,

1/1

Figura 9.44 Diagrama de estados ejemplo 9.6.5.

Solución:

Observando que en 1 se espera un cero; y que 2 simboliza que ha llegado un cero.

Se tiene que es un reconocedor continuo de las secuencias 01110 y 01111 con salida uno.

La salida es cero en el resto de los casos.

Cuando reconoce una de las secuencias anteriores vuelve a comenzar de nuevo.

Prof. Leopoldo Silva Bijit.

05-03-2004

195

UNIVERSIDAD TECNICA FEDERICO SANTA MARIA

DEPARTAMENTO DE ELECTRONICA

ELO211 Sistemas Digitales

9.6.6.Inferir conducta de la máquina secuencial

A

0/0

1/0

1/0

0/0

B

1/1

C

1/0

φ/0

φ/0

0/0

D

E

1/0

F

φ/0

0/0

G

Figura 9.45 Diagrama de estados ejemplo 9.6.6.

Solución:

Asumiendo que el estado inicial es el A: analiza secuencias de largo cuatro. Si la secuencia es 1111

genera salida 1; en el resto de las secuencias la salida es cero.

Prof. Leopoldo Silva Bijit.

05-03-2004

196

UNIVERSIDAD TECNICA FEDERICO SANTA MARIA

DEPARTAMENTO DE ELECTRONICA

ELO211 Sistemas Digitales

9.6.7. Máquina vendedora de bebidas.

Especificaciones: Liberar una bebida después de que se hayan ingresado 150 pesos. Pueden ingresarse

monedas de 50 y 100 pesos(por dos ranuras diferentes, en las cuales no pueden introducirse monedas

simultáneamente). La máquina no entrega vuelto.

Reset

M50

Abrir

Expendedor

a

Sensor Monedas

M100

Mecanismo

para entregar envase

Clock

Figura 9.46 Diagrama en bloques de máquina vendedora.

El diagrama anterior ilustra las entradas y salidas, así como las señales de control.

Las siguientes secuencias satisfacen las especificaciones: 3 monedas de 50; 1 de 100 seguida de una de

50; una de 50 seguida de una de 100; dos de 100(el usuario pierde 50). Las posibles soluciones se

ilustran en el siguiente diagrama:

Las salidas de los estados: E0, E1, E2 y E3 deben desactivar la señal abrir. Luego de los estados: E4, E5,

E6 y E7 debe retornarse al estado inicial E0. Si asignamos la lógica: cuando se ingresa una moneda de 50

la señal M50 es 1; y mientras no se ingrese M50 es cero; y el mismo tipo de lógica para las monedas de

100. Habría que agregar lazos para mantenerse en los estados a la espera de ingreso de monedas.

Reset

E0

M100

M50

E1

M50

E3

E2

M100

M50

E4/

abrir

E5/

abrir

M100

E6/

abrir

M50

E7/

abrir

Figura 9.47 Diagrama de estados de máquina vendedora.

Prof. Leopoldo Silva Bijit.

05-03-2004

197

UNIVERSIDAD TECNICA FEDERICO SANTA MARIA

DEPARTAMENTO DE ELECTRONICA

ELO211 Sistemas Digitales

Si se asignan nombres lógicos a los estados(en lugar de denominarlos Ei), que recuerden la condición del

estado(0, 50, 100,150). Y si para la inserción de una modeda de 50 se emplea L(en romano) = 1 y C= 1(

para inserción de monedas de a 100), las transiciones se rotulan con las ecuaciones lógicas que implican

el cambio de estado. Entonces puede simplificarse el diagrama, según:

L’ C’ + Reset

Reset

L

C

L

0

0

L’C’ +Reset

50

0

L’ C’

100

0

C

L’ C’

Entradas CL Reset=0

E.Actual

00

01

10

11

0

0

50

100

50

50

100

150

100

100

150

150

150

150

Próximo estado

E.Actual

L+C

150

1

Reset’

0

50

100

150

Entradas

00

0

0

CL

01

-

Reset=1

10

11

-

Abrir

0

0

0

1

Abrir

0

0

0

1

Figura 9.48 Diagrama de estados simplificado.

Nótese que el control Reset sólo está permitido para ingresar al estado 0, o para salir del estado 150. Las

casillas marcadas con un guión se pueden emplear como condiciones superfluas. Si se agrega una señal

para devolver monedas, podría aplicarse la señal reset en estados intermedios, o cuando la cantidad

ingresada exceda los $ 150(en este caso no se puede comprar con dos monedas de a 100) o que exceda

los $200.

El problema queda completamente especificado, si están presentes todas las transiciones posibles, o si

quedan bien definidas todas las casillas de la matriz de transiciones.

9.6.8. Cerebro de Hormiga. (Ant Brain. Propuesto en el MIT).

Se desea diseñar una máquina secuencial cuyo objetivo es permitir a la hormiga encontrar la salida del

laberinto.

La hormiga dispone de dos sensores en las antenas izquierda y derecha(I y D), que están en 1 si la antena

respectiva entra en contacto con las paredes del laberinto; y se colocan en cero si dejan de estar en

contacto. Son las entradas a la máquna de estados finitos.

La hormiga también dispone de tres señales de actuación, que son las salidas de la máquina, una señal

para avanzar hacia delante A; otra para doblar levemente hacia la izquierda DI; y otra para doblar

levemente hacia la derecha DD.

Prof. Leopoldo Silva Bijit.

05-03-2004

198

UNIVERSIDAD TECNICA FEDERICO SANTA MARIA

DEPARTAMENTO DE ELECTRONICA

ELO211 Sistemas Digitales

La estrategia para diseñar el cerebro de la hormiga es mantener la pared a la derecha de la hormiga.

Figura 9.49 Laberinto.

Para desarrollar el diagrama de estados, se elige emplear el modelo de Moore. Es decir, las salidas estarán

asociadas al estado.

Se definen los estados posibles, y en cada uno de éstos debe observarse los valores de las entradas que

llevan a otros estados. Debe notarse que se tienen cuatro combinaciones posibles para los valores

permitidos a las entradas, esto implica dibujar 4 transiciones a estados próximos. Sin embargo es posible

simplificar el diagrama rotulando las transiciones como una expresión lógica de las entradas.

Ejemplos:

Si debe pasarse a cierto estado cuando cualesquiera de las antenas tocan una pared, la transición puede

rotularse ( I + D).

Si debe pasarse a cierto estado cuando ambas antenas no tocan a alguna pared, la transición puede

rotularse ( I ' D'). Es decir, que ambas no toquen.

Si la transición es cuando la izquierda no toque y la derecha entre en contacto con la pared, la transición

se anota: (I' D).

Para encontrar los estados debe analizarse las diversas situaciones en que se puede encontrar la hormiga

en su recorrido del laberinto. Observando las entradas, y las acciones que ésta puede realizar, a

continuación se plantean algunas de las situaciones:

Prof. Leopoldo Silva Bijit.

05-03-2004

199

UNIVERSIDAD TECNICA FEDERICO SANTA MARIA

DEPARTAMENTO DE ELECTRONICA

ELO211 Sistemas Digitales

A: Siguiendo la muralla y tocándola:

Avanzar, doblando levemente a la

izquierda, hasta llegar a B:

B: Siguiendo la muralla y no tocándola:

Avanzar, doblando levemente a la

derecha. O se vuelve a A, o se pasa

a C.

C: Se acaba la pared:

Avanzar, doblando levemente a la

derecha, hasta llegar a D:

D: Vuelve a tocar la muralla, con la

Antena derecha:

Es la situación A.

E: Pared al frente: Mientras

toque con alguna antena:

Doblar levemente a la

izquierda hasta pasar a F:

F: Igual situación que en el estado B.

G: Tocando la pared con la izquierda.

Doblar a la izquierda hasta no tocar

la pared. Es la situación B.

H: Perdido:

Avanzar hasta tocar algo.

Figura 9.50 Esquema de situaciones. Definición de estados.

No se encuentran otras situaciones que no se hayan planteado, entonces se procede a conectar los

diferentes estados, mediante el siguiente un diagrama:

Prof. Leopoldo Silva Bijit.

05-03-2004

200

UNIVERSIDAD TECNICA FEDERICO SANTA MARIA

DEPARTAMENTO DE ELECTRONICA

ELO211 Sistemas Digitales

I+D

LOST

(A)

I’ D

E/G

(DI)

I+D

D

I’ D’

I’ D’

A

(DI, A)

I

D

I’ D’

B

C

(DD, A)

(DD, A)

D’

D’

Figura 9.51 Diagrama de estados para el cerebro de la hormiga.

Nótese que los estados E y G se tratan como si fuera un solo estado. En ambos se toca con la antena

izquierda, y el objetivo(local, para cumplir la estrategia) es dejar de tocar la pared.

El diagrama muestra que los estados B y C podrían tratarse como uno solo(son equivalentes). Ya que

tienen iguales salidas; y para iguales entradas, se pasa a igual estado próximo(más adelante se verán

algoritmos para determinar estados equivalentes).

Si se funden los estados B y C se llega al siguiente diagrama, que representa el cerebro de la hormiga:

I+D

LOST

(A)

I’ D

E/G

(DI)

I+D

D

L’ R’

I’ D’

A

(DI, A)

I

I’ D’

D’

B/C

(DD,

A)

Figura 9.52 Reducción de estados equivalentes.

Prof. Leopoldo Silva Bijit.

05-03-2004

201

UNIVERSIDAD TECNICA FEDERICO SANTA MARIA

DEPARTAMENTO DE ELECTRONICA

ELO211 Sistemas Digitales

9.6.9. Contador sincrónico con control de modo M.

Si M = 0 el contador es binario ascendente; si M = 1 el contador avanza según código Gray. A

continuación se indican las secuencias:

binario: 000, 001, 010, 011, 100, 101, 110, 111

Gray:

000, 001, 011, 010, 110, 111, 101, 100

El diagrama de estados se construye para la secuencia binaria, con transiciones con entrada de control

igual a cero. Luego, se marcan las transiciones para contar en Gray:

0

reset

S0

[000]

S1

0

[001]

S2

[010]

0

S3

[011]

0

S4

[100]

0

S5

[101]

0

S6

[110]

0

S7

[111]

0

Figura 9.53 Contador binario ascendente.

0

reset

S0

[000]

S1

[001]

0

1

S2

[010]

0

0

1

S3

[011]

0

S4

[100]

1

0

S5

[101]

0

S6

[110]

1

S7

[111]

1

1

1

0

1

Figura 9.54 Contador Gray descendente.

9.6.10 Reconocedor de un patrón finito.

Sean: entrada x y salida z. La salida se activa cada vez que se presenta la secuencia 010, y mientras que la

secuencia 100 no se haya presentado, en cuyo caso la salida se desactiva permanentemente.

Ejemplos de secuencias, y columna vertebral del diagrama de estados:

X: 0 0 1 0 1 0 1 0 0 1 0 …

Z: 0 0 0 1 0 1 0 1 0 0 0 …

X: 1 1 0 1 1 0 1 0 0 1 0 …

Z: 0 0 0 0 0 0 0 1 0 0 0 …

Prof. Leopoldo Silva Bijit.

05-03-2004

202

UNIVERSIDAD TECNICA FEDERICO SANTA MARIA

DEPARTAMENTO DE ELECTRONICA

ELO211 Sistemas Digitales

E0

reset

[0]

0

1

E1

E4

[0]

[0]

1

0

E2

E5

[0]

[0]

0

0

E3

E6

[1]

[0]

0/1

Figura 9.55 Diagrama de estados inicial.

Luego deben completarse las transiciones que faltan.

Si en E5 llega un cero, debe ir al estado permanente E6, ya que habría reconocido la secuencia 100. Si

estando en E3(los últimos 3 bits de la secuencia son 010) llega un 1, los últimos dos serán ahora 01, esto

implica pasar al estado E2.

En E1 debe permanecer si llegan secuencias de ceros. En E4 debe permanecer si llegan secuencias de

unos.

Si estando en E2 llega un uno, se tendrán dos unos seguidos, entonces debe pasarse al estado E4.

Si estando en E5 llega un uno, se tendrá hasta ese momento, que los dos últimos de la secuencia son 01,

entonces debe pasarse al estado E2.

El diagrama final se muestra a continuación:

Prof. Leopoldo Silva Bijit.

05-03-2004

203

UNIVERSIDAD TECNICA FEDERICO SANTA MARIA

DEPARTAMENTO DE ELECTRONICA

ELO211 Sistemas Digitales

E0

reset

[0]

0

1

E1

0

[0]

E4

...0

1

...01

...010

1

E5

[0]

[0]

1

0

1

0

1

E2

[0]

...1

0

E3

E6

[1]

[0]

...100

0/1

Figura 9.56 Diagrama de estados final.

Si denominamos X a la entrada, el diagrama puede describirse, según:

While (1)

{if ( reset) estado = E0;

else

switch (estado)

{ case E0: if (X) estado = E4 else estado = E1;

case E1: if (X) estado = E2 else estado = E1;

case E2: if (X) estado = E4 else estado = E3;

case E3: if (X) estado = E2 else estado = E6;

case E4: if (X) estado = E4 else estado = E5;

case E5: if (X) estado = E2 else estado = E6;

case E6: estado = E6;

}

}

Prof. Leopoldo Silva Bijit.

05-03-2004

204

UNIVERSIDAD TECNICA FEDERICO SANTA MARIA

DEPARTAMENTO DE ELECTRONICA

ELO211 Sistemas Digitales

9.6.11. Diseñar el control de una máquina de lavar ropa.

El funcionamiento de la lavadora es el siguiente:

• Cuando se oprime el botón “Partida”, después de colocar las prendas, la máquina determina el tamaño

de la carga( Mediano / Grande) y de acuerdo al tamaño dispensa la cantidad de agua y detergente.

• Luego de esto, la máquina lava la ropa por 10 minutos.

• Después del ciclo anterior, la máquina enjuaga las ropas por 10 minutos. Detecta si el líquido de

salida está sucio, al final del enjuague; en caso de estarlo, repite el ciclo (lavado + enjuague), pero no

más de 3 repeticiones.

• Luego centrifuga las ropas hasta que no detecta descarga de agua, pero por no más de 20 minutos.

Las duraciones de los ciclos se logran con temporizadores. Los cuales pueden modelarse con una entrada

que inicia la cuenta del tiempo, y una salida que indica que ya transcurrió el tiempo programado.

Entradas

Descripción

Botón de Partida

Sensor carga mediana

Sensor carga grande

Sensor salida sucia

Sensor descarga salida

Timeout 60 min

Timeout 10 min

Variable

SP

SM

SG

SS

SD

O60

O10

Salidas

Descripción

Dispensador mediano

Dispensador Grande

Actuador lavado

Actuador enjuague

Actuador centrífuga

Inicio timer 60 min

Inicio timer 10 min

Variable

AM

AG

AL

AE

AC

I60

I10

Figura 9.57 Especificaciones de variables.

reset

SP’

SD’ # O10

Inicio

SD’

(SP&SM) / AM, AL, I10, I60

#

(SP&SG) / AG, AL, I10, I60

2

Lavado

O10’ / AL

O10 / I10

O10’ / AE

Centrifuga

O10’&SD / AC

O10&SD / I10

O10&SS&O60’&SM / AM, AL, I10

#

O10&SS&O60’&SG / AG, AL, I10

Centrifuga

Enjuage

O10&SS’ # O60 / I10

1

O10’&SD / AC

Figura 9.58 Diagrama de estados control lavadora.

Prof. Leopoldo Silva Bijit.

05-03-2004

205

UNIVERSIDAD TECNICA FEDERICO SANTA MARIA

DEPARTAMENTO DE ELECTRONICA

ELO211 Sistemas Digitales

9.7. Diseño de Máquinas Secuenciales empleando lenguaje Abel.

9.7.1 Detector secuencia 0101.

A continuación se tiene el diagrama de estados de una máquina secuencial(Modelo de Mealy) que

produce una salida alta cada vez que se detecta la secuencia 0101 en la entrada; y salida cero en el resto

de los casos.

1/0

0/0

1/0

A

0/0

B

B

1/0

C

0/0

D

1/1

0/0

Figura 9.59 Diagrama de estados detector secuencia 0101.

La siguiente secuencia de entrada produce las siguientes secuencias de salida y de transiciones de estados.

Entrada

0

1

0

1

1

0

0

1

1

....

Salida

0

0

0

1

0

0

0

0

0

....

Estado

B

C

D

C

A

B

B

C

A

….

Figura 9.60 Secuencias de entrada, salida y de estados.

El siguiente módulo describe el diagrama de estados.

En las declaraciones se emplea el tipo reg, para declarar una salida registrada; es decir, una salida de un

flip-flop D. En el diseño se tienen dos salidas: z es una salida combinacional, que como veremos es

asincrónica; mientras que la salida zs es de tipo sincrónica.

Luego se declara el registro de estado(sreg), en función de las salidas de los flip-flops.

También se efectúa un mapeo de nombres lógicos a físicos. Esto también se denomina asignación de

estados. El estado inicial, será el estado A; cuyo nombre binario será [0, 0].

En las ecuaciones se indican las señales de entrada que ingresan al reloj(clock), a la habilitación de la

salida(enab, no se usa enable ya que es palabra reservada) y al reseteo asincrónico de la

macrocelda(reset).

Luego se describe el diagrama de estados de sreg, mediante la especificación de cada estado. En la cual

se indica las transiciones de acuerdo a los valores de las entradas(esto se indica con la sentencia if then

else); y los valores que deben tomar las salidas(esto se realiza con la sentencia with). Debe notarse que las

salidas registradas se asignan con :=, y que a las salidas combinacionales se les asigna un valor con el

signo igual. Pueden agruparse acciones, mediante el uso de paréntesis cursivos{ }.

Finalmente se especifican vectores de prueba. Se emplea la constante .c. para modelar un pulso de reloj,

equivale a generar tres vectores, uno con clock en cero, luego un valor de clock uno; y finalmente un

valor de clock cero. Como el resto de las entradas no cambian, se cumplen automáticamente las

especificaciones de tiempos de set-up y hold para la variable de entrada x.

Prof. Leopoldo Silva Bijit.

05-03-2004

206

UNIVERSIDAD TECNICA FEDERICO SANTA MARIA

DEPARTAMENTO DE ELECTRONICA

ELO211 Sistemas Digitales

La constante .C. es adecuada para flip-flops que operan con cantos de subida; la constante .K. genera la

secuencia 101 en el reloj, que es adecuada para flip-flops que operan con cantos de bajada. Además se

tienen los estímulos .D. que genera un canto de bajada , con la secuencia 10; la constante .U. genera un

canto de subida, con la secuencia 01.

Se generan los vectores asociados a la tabla anterior con las secuencias de la entrada, salida y estados.

MODULE estado1

TITLE 'Diagrama de Estados. Modelo de Mealy'

"Declaraciones

q1, q0, zs pin istype 'reg';"Estado y Salida Registrada

clock, enab, reset, x pin ;"Entradas

z pin istype 'com';"Salida Combinacional.

sreg = [q1,q0];

"Valores de los estados

A= 0; B= 1; C= 2; D= 3;

equations

[q1,q0,zs].clk= clock;

[q1,q0,zs].oe = !enab;

[q1,q0,zs].ar = reset; "Con reset va a [0, 0](el estado A).

state_diagram sreg;

State A:

zs := 0; if (!x) then B with z = 0; else A with z = 0;

State B:

if (!x) then B with z = 0; else C with z = 0;

State C:

if (!x) then D with z = 0; else A with z = 0;

State D:

if (!x) then B with z = 0; else C with {z = 1; zs := 1;}

test_vectors ( [clock,enab,reset, x]->[sreg,zs])

[.c. , 0 , 1 , 0 ]->[A ,0];

[.c. , 0 , 0 , 1 ]->[A ,0];

[.c. , 0 , 0 , 0 ]->[B ,0];

[.c. , 0 , 0 , 1 ]->[C ,0];

[.c. , 0 , 0 , 0 ]->[D ,0];

[.c. , 0 , 0 , 1 ]->[C ,1];

[.c. , 0 , 0 , 1 ]->[A ,0];

[.c. , 0 , 0 , 0 ]->[B ,0];

[.c. , 0 , 0 , 0 ]->[B ,0];

[.c. , 0 , 0 , 1 ]->[C ,0];

[.c. , 0 , 0 , 1 ]->[A ,0];

END

Prof. Leopoldo Silva Bijit.

05-03-2004

207

UNIVERSIDAD TECNICA FEDERICO SANTA MARIA

DEPARTAMENTO DE ELECTRONICA

ELO211 Sistemas Digitales

Después de la compilación, las ecuaciones reducidas resultan:

q1.OE = (!enab);

q1 := (q1.FB & !q0.FB & !x) # (q0.FB & x);

q1.AR = (reset);

q1.C = (clock);

q0.OE = (!enab);

q0 := (!x);

q0.AR = (reset);

q0.C = (clock);

zs.OE = (!enab);

zs := (q1.FB & q0.FB & x);

zs.AR = (reset);

zs.C = (clock);

z = (q1.FB & q0.FB & x);

El en siguiente diagrama se ilustra la notación empleada para las variables asociadas a cada salida

registrada. Nótese que cuando q1 aparece al lado izquierdo de la asignación, está representando a la

entrada D del flip-flop, es el próximo estado que tomará dicha variable; es decir q1(k+1), con la notación

empleada en clases.

Cuando aparece en el lado derecho el término q1.FB(por feed-back) se lo interpreta como la salida del

flip-flop.

clock

enable

reset

Q.AR

Q.OE

AR

D

Q.C

x

Q

clk

Q.FB

in

Q.PIN

Figura 9.61 Variables internas. Visión del programador.

Prof. Leopoldo Silva Bijit.

05-03-2004

208

UNIVERSIDAD TECNICA FEDERICO SANTA MARIA

DEPARTAMENTO DE ELECTRONICA

ELO211 Sistemas Digitales

Nótese que la expresión booleana para la salida asincrónica z es idéntica a la de zs, que es salida de flipflop.

La salida del reporte de simulación muestra los estímulos y respuestas debidos a los vectores elegidos.

c r

l e e

on s

ca e

q qz

kb t x 1 0s

V0001 C 0 1 0 Z Z Z

C010 LLL

C010 LLL

C010 LLL

V0002 C 0 0 1 L L L

C001 LLL

C001 LLL

V0003 C 0 0 0 L L L

Clock = 0

C000 LHL

Clock = 1

C000 LHL

Clock = 0

V0004 C 0 0 1 L H L

C001 HLL

C001 HLL

V0005 C 0 0 0 H L L

C000 HHL

C000 HHL

V0006 C 0 0 1 H H L

C001 HLH

C001 HLH

C001 HLH

V0007 C 0 0 1 H L H

C001 LLL

C001 LLL

V0008 C 0 0 0 L L L

C000 LHL

C000 LHL

V0009 C 0 0 0 L H L

C000 LHL

C000 LHL

V0010 C 0 0 1 L H L

C001 HLL

C001 HLL

V0011 C 0 0 1 H L L

C001 LLL

C001 LLL

11 out of 11 vectors passed.

Debe notarse que cada vector genera tres estímulos(esto debido al pulso definido con .c.).

Los vectores generan las siguientes formas de ondas:

Prof. Leopoldo Silva Bijit.

05-03-2004

209

UNIVERSIDAD TECNICA FEDERICO SANTA MARIA

DEPARTAMENTO DE ELECTRONICA

ELO211 Sistemas Digitales

V003

asincrónica

V006

Figura 9.62 Simulación funcional. Formas de ondas generadas por estímulos.

La señal z cambia entre dos cantos de subida del reloj, por esto se dice que es asincrónica respecto de

éste. Mientras que la señal zs, que se obtiene como salida de un flip-flop será sincrónica con éste.

La salida z cambia en la transición, apenas se produce la condición que la genera. La señal zs ocurre

generalmente un poco después, ya que se activa cuando ocurre el siguiente canto de subida del reloj.

La señal z, es una salida de una máquina de Mealy, y depende de las entradas; lo cual puede verse ya que

interviene la entrada x en la ecuación: z = (q1.FB & q0.FB & x);

Si esta salida está conectada como entrada a otra máquina secuencial, que ocupe el mismo reloj, podría no

cumplir las condiciones para operación sincrónica. Por lo tanto es recomendable emplear la salida

sincronizada zs.

Con dispositivos programables conviene emplear el modelo de Moore. En este caso las salidas están

sincronizadas con el reloj.

9.7.2. Reconocedor de un patrón finito. Modelo de Moore

Sean: entrada x y salida z. La salida se activa cada vez que se presenta la secuencia 010, y mientras que la

secuencia 100 no se haya presentado, en cuyo caso la salida se desactiva permanentemente.

Ejemplos de secuencias de entrada y salida:

X: 0 0 1 0 1 0 1 0 0 1 0 …

Z: 0 0 0 1 0 1 0 1 0 0 0 …

X: 1 1 0 1 1 0 1 0 0 1 0 …

Z: 0 0 0 0 0 0 0 1 0 0 0 …

Ver ejemplo 9.6.10.

El siguiente programa Abel, implementa el diseño:

MODULE fsm010

TITLE 'fsm010'

"Activa Z cada vez que llega 010 y mientras no llegue 100.

"si llega 100 se activa Y, y permanece en ese estado.

Prof. Leopoldo Silva Bijit.

05-03-2004

210

UNIVERSIDAD TECNICA FEDERICO SANTA MARIA

DEPARTAMENTO DE ELECTRONICA

ELO211 Sistemas Digitales

"Declaraciones

"Pines de entrada

clk, Xin, RESET pin;

"Pines de Salida

Q0, Q1, Q2 pin istype 'reg';

Z, Y pin istype 'com';

"Registro de Estado

SREG = [Q0, Q1, Q2];

"Definicion de Estados

S0 = [0,0,0]; " Estado Inicial. (Reset state)

S1 = [0,0,1]; " secuencias tipo ...0

S2 = [0,1,0]; " secuencias tipo ...01

S3 = [0,1,1]; " secuencias tipo ...010

S4 = [1,0,0]; " secuencias tipo ...1

S5 = [1,0,1]; " secuencias tipo ...10

S6 = [1,1,0]; " secuencias tipo ...100

equations

[Q0,Q1,Q2].clk= clk;

[Q0.ar, Q1.ar, Q2.ar] = RESET;"Con Reset va a S0

"Z=!Q0&Q1&Q2; Y=Q0&Q1&!Q2;

"Modelo de Moore

state_diagram SREG

state S0: Z=0; Y=0;

state S1:

state S2:

state S3: Z=1;

state S4:

state S5:

state S6: Y=1;

if Xin then S4 else S1;

if Xin then S2 else S1;

if Xin then S4 else S3;

if Xin then S2 else S6;

if Xin then S4 else S5;

if Xin then S2 else S6;

goto S6;

test_vectors ([clk, RESET, Xin] -> [Z,Y])

[.C.,1,.X.] ->[0,0];"reset

[.C.,0, 0] -> [0,0];"secuencia 00101010010

[.C.,0, 0] -> [0,0];

[.C.,0, 1] -> [0,0];

[.C.,0, 0] -> [1,0];

[.C.,0, 1] -> [0,0];

[.C.,0, 0] -> [1,0];

[.C.,0, 1] -> [0,0];

[.C.,0, 0] -> [1,0];

[.C.,0, 0] -> [0,1];

[.C.,0, 1] -> [0,1];

[.C.,0, 0] -> [0,1];

Prof. Leopoldo Silva Bijit.

05-03-2004

211

UNIVERSIDAD TECNICA FEDERICO SANTA MARIA

DEPARTAMENTO DE ELECTRONICA

ELO211 Sistemas Digitales

END fsm010;

Nótese la definición de las salidas asociadas al estado. Y el salto incondicional, mediante el goto.

Las salidas también podrían haberse definido en el segmento de las ecuaciones, esto se insinúa como

comentario.

Después de la compilación, resultan las ecuaciones reducidas:

Q0 := (!Q0.FB & Q1.FB & Q2.FB & !Xin) # (Q0.FB & !Q1.FB & !Xin) # (Q0.FB & !Q2.FB)

# ( !Q2.FB & Xin);

Q0.AR = (RESET);

Q0.C = (clk);

Q1 := (!Q0.FB & Q1.FB & !Xin) # ( !Q0.FB & Q2.FB & Xin) # (Q0.FB & Q1.FB & !Q2.FB)

# (Q0.FB & !Q1.FB & Q2.FB);

Q1.AR = (RESET);

Q1.C = (clk);

Q2 := (!Q1.FB & !Q2.FB & !Xin) # (!Q0.FB & !Q2.FB & !Xin) # (!Q0.FB & !Q1.FB & !Xin);

Q2.AR = (RESET);

Q2.C = (clk);

Z = (!Q0.FB & Q1.FB & Q2.FB);

Y = (Q0.FB & Q1.FB & !Q2.FB);

Con estas ecuaciones, podría haberse efectuado el diseño sin emplear diagrama de estados.

Después de la compilación de los vectores, se obtiene:

R

E

cS X

l E i

kT n ZY

V0001 C 1 X

C1X

C1X

V0002 C 0 0

C00

C00

V0003 C 0 0

C00

C00

V0004 C 0 1

C01

C01

V0005 C 0 0

C00

C00

C00

LL

LL

LL

LL

LL

LL

LL

LL

LL

LL

LL

LL

LL

LL

HL

HL

Prof. Leopoldo Silva Bijit.

05-03-2004

212

UNIVERSIDAD TECNICA FEDERICO SANTA MARIA

DEPARTAMENTO DE ELECTRONICA

ELO211 Sistemas Digitales

V0006 C 0 1 H L

C01 HL

C01 LL

C01 LL

V0007 C 0 0 L L

C00 LL

C00 HL

C00 HL

V0008 C 0 1 H L

C01 HL

C01 LL

C01 LL

V0009 C 0 0 L L

C00 LL

C00 HL

C00 HL

V0010 C 0 0 H L

C00 HL

C00 LH

C00 LH

V0011 C 0 1 L H

C01 LH

C01 LH

V0012 C 0 0 L H

C00 LH

C00 LH

12 out of 12 vectors passed.

Generando las siguientes formas de ondas:

Figura 9.63 Formas de ondas ejemplo 9.7.2.

9.7.3. Contador sincrónico con control de modo M.

Si M = 0 el contador es binario ascendente; si M = 1 el contador avanza según código Gray. A

continuación se indican las secuencias de cuentas:

Prof. Leopoldo Silva Bijit.

05-03-2004

213

UNIVERSIDAD TECNICA FEDERICO SANTA MARIA

DEPARTAMENTO DE ELECTRONICA

ELO211 Sistemas Digitales

binario: 000, 001, 010, 011, 100, 101, 110, 111

Gray:

000, 001, 011, 010, 110, 111, 101, 100

El diagrama de estados se construye para la secuencia binaria, con transiciones con entrada de control

igual a cero. Luego, se marcan las transiciones para contar en Gray.

En este diseño las salidas corresponden al estado directamente. Como es usual en contadores.

Ver ejemplo 9.6.9.

MODULE cntgray

TITLE 'Contador en Gray'

"Pines de Entrada

clk, M, RESET pin 1, 2, 3;

"Pines de Salida

Z0, Z1, Z2

pin istype 'pos, reg';

"Registro de Estado

SREG = [Z0, Z1, Z2];

S0 = [0,0,0];

S1 = [0,0,1];

S2 = [0,1,0];

S3 = [0,1,1];

S4 = [1,0,0];

S5 = [1,0,1];

S6 = [1,1,0];

S7 = [1,1,1];

equations

[Z0,Z1,Z2].clk= clk;

[Z0.ar, Z1.ar, Z2.ar] = RESET; "Reset asincrónico lleva al estado S0

state_diagram SREG

state S0: goto S1;

state S1: if M then S3 else S2;

state S2: if M then S6 else S3;

state S3: if M then S2 else S4;

state S4: if M then S0 else S5;

state S5: if M then S4 else S6;

state S6: goto S7;

state S7: if M then S5 else S0;

test_vectors ([clk, RESET, M] -> [Z0, Z1, Z2])

[0,1,.X.] -> [0,0,0];

[.C.,0,0] -> [0,0,1];

[.C.,0,0] -> [0,1,0];

[.C.,0,1] -> [1,1,0];

[.C.,0,1] -> [1,1,1];

[.C.,0,1] -> [1,0,1];

[.C.,0,0] -> [1,1,0];

[.C.,0,0] -> [1,1,1];

end cntgray

Prof. Leopoldo Silva Bijit.

05-03-2004

214

UNIVERSIDAD TECNICA FEDERICO SANTA MARIA

DEPARTAMENTO DE ELECTRONICA

ELO211 Sistemas Digitales

Las ecuaciones resultan, después de la compilación:

Equations:

Z0 := (Z0.FB & !Z1.FB & !M) # (Z0.FB & !Z2.FB & !M) # (Z0.FB & Z2.FB & M)

# (!Z0.FB & Z1.FB & Z2.FB & !M) # (Z1.FB & !Z2.FB & M);

Z0.AR = (RESET);

Z0.C = (clk);

Z1 := (!Z0.FB & Z2.FB & M) # (!Z1.FB & Z2.FB & !M) # (Z1.FB & !Z2.FB);

Z1.AR = (RESET);

Z1.C = (clk);

Z2 := (!Z0.FB & !Z1.FB & M) # (Z0.FB & Z1.FB & M) # (!Z2.FB & !M);

Z2.AR = (RESET);

Z2.C = (clk);

Los estímulos generan las siguientes formas de ondas:

Figura 9.64 Formas de ondas contador Gray.

Prof. Leopoldo Silva Bijit.

05-03-2004

215

UNIVERSIDAD TECNICA FEDERICO SANTA MARIA

DEPARTAMENTO DE ELECTRONICA

ELO211 Sistemas Digitales

Índice de Figuras.

Figura 9.34 Diagrama en bloque verificador BCD. ................................................................................189

Figura 9.35 Diagrama de estados verificador BCD. ...............................................................................190

Figura 9.36 Diagrama de estados reducido del verificador BCD............................................................191

Figura 9.37 Reconocedor de secuencia 0101. .........................................................................................192

Figura 9.38 Diagrama de estados completo del reconocedor continuo...................................................192

Figura 9.39 Diagrama de estados inicial. ................................................................................................193

Figura 9.40 Diagrama de estados completo. ...........................................................................................193

Figura 9.41 Estados siguientes al estado 001..........................................................................................194

Figura 9.42 Diagrama de estados completo, sin salida. ..........................................................................194

Figura 9.43 Tabla de verdad de la función de salida...............................................................................195

Figura 9.44 Diagrama de estados ejemplo 9.6.5. ....................................................................................195

Figura 9.45 Diagrama de estados ejemplo 9.6.6. ....................................................................................196

Figura 9.46 Diagrama en bloques de máquina vendedora. .....................................................................197

Figura 9.47 Diagrama de estados de máquina vendedora. ......................................................................197

Figura 9.48 Diagrama de estados simplificado. ......................................................................................198

Figura 9.49 Laberinto..............................................................................................................................199

Figura 9.50 Esquema de situaciones. Definición de estados...................................................................200

Figura 9.51 Diagrama de estados para el cerebro de la hormiga.............................................................201

Figura 9.52 Reducción de estados equivalentes......................................................................................201

Figura 9.53 Contador binario ascendente................................................................................................202

Figura 9.54 Contador Gray descendente. ................................................................................................202

Figura 9.55 Diagrama de estados inicial. ................................................................................................203

Figura 9.56 Diagrama de estados final....................................................................................................204

Figura 9.57 Especificaciones de variables. .............................................................................................205

Figura 9.58 Diagrama de estados control lavadora. ................................................................................205

Figura 9.59 Diagrama de estados detector secuencia 0101.....................................................................206

Figura 9.60 Secuencias de entrada, salida y de estados. .........................................................................206

Figura 9.61 Variables internas. Visión del programador. .......................................................................208

Figura 9.62 Simulación funcional. Formas de ondas generadas por estímulos.......................................210

Figura 9.63 Formas de ondas ejemplo 9.7.2. ..........................................................................................213

Figura 9.64 Formas de ondas contador Gray. .........................................................................................215

Prof. Leopoldo Silva Bijit.

05-03-2004

216