tema 2: lenguaje vhdl introduccion

Anuncio

INTRODUCCION

TEMA 2:

LENGUAJE VHDL

❏

Breve historia

❏

Características de VHDL

❏

Introducción

❏

Codificación orientada al hardware

❏

Conceptos básicos

❏

Objetivos del tema

❏

Organización del diseño

❏

Descripción de la arquitectura

❏

Modelo de tiempos

❏

Descripción de circuitos digitales

❏

Simulación

Universidad de Zaragoza, IEC.

Luis A. Barragán y José I. Artigas

Lenguaje VHDL - 1

Breve historia

Características de VHDL (1)

❏

¿Qué significa VHDL?

– VHDL = VHSIC Hardware

Description Language

– VHSIC = Very High Speed Integrated

Circuits

❏

Inicialmente, documentación de diseños y

creación de modelos de simulación de

hardware para el DoD (1981).

❏

❏

Estándar IEEE ⇒ Portabilidad

– 1987, se aprobó el lenguaje estándar

IEEE 1076-1987

– 1992, cada 5 años se revisa el proceso

de estandarización, IEEE 1076-1992

Permite descripción de hardware digital:

– Puertas lógicas

– Sistemas complejos (SPARC)

Universidad de Zaragoza, IEC.

❏

Permite diseños modulares y jerárquicos.

Soporta distintas metodologías de diseño:

– Arriba-abajo

– Abajo-arriba

– Mixto

❏

Soporta varias técnicas de modelado digital:

– Descripción algorítmica

– Ecuaciones booleanas

– Máquinas de Estados Finitos (MEFs)

❏

Soporta temporización:

– Síncrona

– Asíncrona

❏

Es un lenguaje concurrente, aunque permite

definir dominios en los que las acciones se

suceden en orden secuencial

Luis A. Barragán y José I. Artigas

Lenguaje VHDL - 2

Codificación orientada al

hardware

Características de VHDL (2)

❏

Soporta tipos abstractos de datos.

❏

Codificar pensando en puertas y FFs, no en

variables y funciones!!

❏

Permite simular el diseño y generar formas

de onda

– Entornos de test (test benchs).

❏

Diseñar circuitos síncronos

– Un único reloj y flanco (si es posible).

❏

Codificar en HDL no nos preserva de

problemas hardware: glitches, violación de

restricciones temporales tsu, th.

❏

Evitar:

– Bucles combinacionales.

– Buffers triestado.

– Latches (usar sólo FFs).

– Set, Reset asíncronos.

– Relojes condicionales (Gated-clock).

❏

❏

Soporta distintos niveles de descripción:

– Comportamental

– RTL

– Lógico

A partir de un modelo en HDL se puede

sintetizar hardware a nivel de puertas con

herramientas especiales de síntesis

– Independencia de la tecnología.

❏

Universidad de Zaragoza, IEC.

Luis A. Barragán y José I. Artigas

Comentar el código fuente ⇒ Reutilización↑

Lenguaje VHDL - 3

Objetivos del tema

CONCEPTOS BASICOS

Enmarcar los lenguajes de descripción de

hardware dentro del proceso de síntesis

lógica

❏

Objetos

❏

Tipos

❏

Presentar una introducción a VHDL

❏

Operadores

❏

Reforzar la sintaxis y semántica de VHDL

con la presentación de ejemplos

❏

• Conocer la sintaxis de VHDL, no implica

necesariamente saber diseñar hardware

con él

❏

Introducir mediante ejemplos la influencia

del estilo de codificación en el hardware

sintetizado

Universidad de Zaragoza, IEC.

Luis A. Barragán y José I. Artigas

Lenguaje VHDL - 4

Objetos

❏

Los objetos en VHDL contienen valores.

❏

Clases de objetos:

– Constant. Se les asigna un valor

inicial que no puede ser modificado.

– Variable. Contiene un valor que

puede ser modificado.

– Signal. Contiene una lista de valores

que incluye el valor actual y un

conjunto de posibles valores futuros.

– File. Modelan ficheros en el entorno

del host. Se utilizan en test-benchs.

❏

Estos objetos se crean mediante su

declaración:

Tipos

❏

Todos los objetos en VHDL son de algún

tipo. Es ilegal conectar señales que no son

del mismo tipo

❏

Un tipo de datos se caracteriza por un

conjunto de valores que puede tener y un

conjunto de operaciones.

– El tipo de cada objeto es estático

❏

Los tipos predefinidos en el lenguaje están

declarados en el package STANDARD:

boolean, bit, bit_vector,

character, string, integer,

real, time, positive, natural.

❏

El lenguaje permite crear nuevos tipos y

definir operaciones con esos tipos a través

de funciones

❏

Tipos de datos predefinidos:

- Scalar

- Composite

- Access

- File

– variable R: natural := 0;

❏

Declaraciones implícitas:

– Puertos de una entidad

– Indices de bucles

Universidad de Zaragoza, IEC.

Luis A. Barragán y José I. Artigas

Lenguaje VHDL - 5

Tipos escalares

❏

Composite

❏

Existe una relación de orden entre los

valores de los objetos de este tipo

INTEGER

constant MUX_ADDRESS: integer := 5;

-- Rango desde -(2**31) hasta (2**31-1)

-- Se puede especificar un rango menor

type INDEX is integer range 0 to 15;

constant MUX_ADDRESS: INDEX := 5;

type natural is integer range 0 to integer'high;

FLOATING POINT

variable F0 : real := 62.3E-2;

-- Se puede especificar un rango

type ANALOG_IN is real range 0.0 to 5.0;

0

Tipo matriz:

– Una o más dimensiones

– Elementos del mismo tipo

– Acceso indexado

1

0

1

2

3

❏

ENUMERATION

-- Conjunto de valores definidos por el usuario

-- Hace más legible el código, se utiliza en la

-- definición de máquinas de estado

type MICRO_OP is (LOAD, STORE, ADD, SUB);

Universidad de Zaragoza, IEC.

Campo2

Campo3

Campo4

Luis A. Barragán y José I. Artigas

3

type ADR_WORD is array (0 to 63) of BIT;

type DATA_WORD is array (7 downto 0) of BIT;

type ROM is array (0 to 125) of DATA_WORD;

-- ∃ arrays predefinidos: BIT_VECTOR

variable OP_CODE: BIT_VECTOR(1 to 5);

OP_CODE := "01001";

OP_CODE := ('0','1','0','0','1');

OP_CODE := (2=>'1', 5=>'1', others=>'0');

Tipo Registro:

– Uno o más campos

– Campos de diferente tipo

– Acceso por nombre

Campo1

FISICOS

-- Representan medidas de magnitudes físicas

-- Existe un tipo TIME cuya unidad es fs

constant TH : time := 10 ns;

2

type OPCODE is (LD, ST, ADD, SUB);

type ADR is array (0 to 63) of BIT;

type INSTRUCTION is record

OPCODE_FIELD: OPCODE;

OPERAND1 : ADR;

OPERAND2 : ADR;

end record;

Lenguaje VHDL - 6

Tipos de datos

❏

Operadores

Un SUBTIPO es un tipo con una restricción.

– Se especifica el tipo base y el rango de

restricciones

– Se comprueba cada asignación para

garantizar que el valor entra dentro del

rango del subtipo

❏

type MATRIZ is

array(integer range<>, integer range <>) of integer;

subtype IMAGEN is MATRIZ (0 to 255, 0 to 255);

subtype POSITIVE is INTEGER range 1 to INTEGER´HIGH

❏

ALIAS. Define nombres alternativos para

partes de un objeto ya existente

signal SCON : bit_vector (7 downto 0);

alias RI : bit is SCON (0)

variable DATA_WORD : BIT_VECTOR (15 downto 0);

alias DATA_BUS : BIT_VECTOR (7 downto 0) is

DATA_WORD (15 downto 8);

Se definen sobre los tipos de datos

predefinidos, aunque se pueden sobrecargar.

package std_logic_arith

package std_logic_unsigned

package std_logic_signed

ARITMÉTICOS

+

*

/

mod

rem

**

abs

RELACIÓN

SIGN O

+

DESPL.

sll

srl

sla

sra

rol

ror

=

/=

Luis A. Barragán y José I. Artigas

>

<=

>=

-

CONCATENACIÓN

Universidad de Zaragoza, IEC.

<

LOGICOS

AND

OR

NAND

NOR

XOR

NOT

&

Lenguaje VHDL - 7

ORGANIZACIÓN DEL

DISEÑO

❏

Entidad:

– Declaración de la entidad.

– Descripción de la arquitectura.

– Declaración de la configuración.

❏

Empaquetamientos y librerías.

❏

Entorno de trabajo con Synopsys.

Entidad

❏

Entidad = Abstracción Hardware de un

Sistema Digital

❏

Las entidades pueden ser jerárquicas.

– Una entidad E1 puede, a su vez, estar

constituida por otras entidades

– Una entidad E2 se puede utilizar como

componente de otra entidad E1

❏

Una entidad consta de:

– Declaración de la Entidad

– Descripción de la Arquitectura

– Declaración de la Configuración

E2

E1

Universidad de Zaragoza, IEC.

Luis A. Barragán y José I. Artigas

Lenguaje VHDL - 8

Declaración de la entidad

Modo de un puerto

❏

Especifica el nombre de la entidad y el

interfaz con su entorno (los puertos)

– Los puertos son señales; su

declaración es implícita.

❏

No especifica la estructura de la entidad.

Visión de “caja negra” (Encapsulado).

❏

Design Entity

A

M

B

N

C

P

D

Q

Entity Declaration

Architecture Body

IN

Config. Declaration

-- Declara el nombre de la entidad,

-- los puertos de entrada y salida, los

-- modos y los tipos de dichos puertos

ENTITY E1 IS

PORT (A, B, C, D : in BIT;

M, N, P, Q : out BIT );

END E1;

Nombres

Universidad de Zaragoza, IEC.

El Modo define la dirección del flujo de

datos visto desde la entidad. Pueden ser:

– IN, sólo pueden ser leídos

– OUT, sólo se les puede asignar valor

– INOUT, BUFFER. se les puede leer y

asignar un valor desde dentro de la

entidad.

Modos

OUT

INOUT

❏

Lectura de un INOUT, lee el

valor del flujo de datos

entrante

❏

Lectura de un BUFFER,

como solo tiene una fuente,

lee el valor asignado

BUFFER

R/W

Tipos

Luis A. Barragán y José I. Artigas

Lenguaje VHDL - 9

Descripción de la arquitectura

❏

Declaración de configuración

Contiene la descripción interna de la entidad.

Estilos de modelado:

– Estructural: Conexión de componentes.

– Comportamental:

• Algoritmo secuencial (Alto Nivel

Abstracción)

• Ecuaciones booleanas (Bajo Nivel

Abstracción)

❏

❏

Realiza la correspondencia entre:

– Entidad/Arquitectura

– Entidad/Componente

❏

Una vez que la configuración se ha

compilado, VHDL puede simular el

modelo global

Entity E1

Una entidad puede tener varias arquitecturas,

que representan diferentes implementaciones

de la misma.

component E2

...

end component

ARCHITECTURE mi_arq OF E1 IS

-- Declaración de items que serán

-- utilizados dentro del cuerpo de

-- la arquitectura

-- Los nombres de los puertos y

-- genéricos no requieren ser

-- declarados

Design Entity

Entity Declaration

...

I_1: E2

E1_A1

E1_A2

Entity E2

BEGIN

Architecture Body

Config. Declaration

-- Instrucciones Concurrentes

-- El orden textual no importa

-- ya que se ejecutan en paralelo

END mi_arq;

Universidad de Zaragoza, IEC.

-- Descripción de entidad E1 en

-- fichero E1.vhd

configuration CFG_E1 of E1 is

for E1_A2

for I_1: E2

use configuration WORK.CFG_E2_A1;

end for;

end for;

end CFG_E1;

E2_A1

Luis A. Barragán y José I. Artigas

E2_A2

-- Descripción de E2 entity en

-- fichero E2.vhd

configuration CFG_E2_A1 of E2 is

for E2_A1

end for;

end CFG_E2_A1

Lenguaje VHDL - 10

Entidad de diseño vs.

placa de circuito impreso

❏

Declaración de Entidad

– Definir zócalos

❏

Arquitectura

– Soldar zócalos en la

placa y Rutear pistas

– En un mismo zócalo se

pueden insertar distintos

C.I. compatibles

funcionalmente y pin a

pin según: velocidad,

precio, consumo,...

❏

Configuración

– Insertar en cada zócalo

un integrado

Universidad de Zaragoza, IEC.

Empaquetamientos y librerías (1)

❏

Empaquetamientos:

– Pueden contener declaraciones y

definiciones de objetos a usar en

diferentes diseños.

– Constan de:

• Declaración: Componentes, constantes,

tipos, funciones y procedimientos.

• Cuerpo: Cuerpos de las funciones y

procedimientos declarados.

package EX_PACK is

z

z --Declarations

z

end;

❏

Luis A. Barragán y José I. Artigas

package body EX_PACK is

z

z --Body Declarations

z

end;

Librerías:

– Los diseños, una vez compilados, se

almacenan en Librerías.

– Una librería es un directorio. Los

diseños compilados son ficheros.

Lenguaje VHDL - 11

Empaquetamientos y librerías (2)

❏

Entorno de trabajo con

Synopsys

odf.sym

Existen librerías predefinidas:

– STD: Contiene los empaquetamientos

CLK

RST

• STANDARD, define los tipos, subtipos y

funciones básicas del lenguaje.

• TEXTIO contiene declaraciones de tipos,

subtipos y programas para operaciones

ASCII.

Símbolo

ppp.sch

– WORK: librería de trabajo

• Aquí se almacenan las entidades de diseño

del usuario

Esquemático

– IEEE: Contiene empaquetamientos:

odf

I_1

I_2

I_3

odf.vhd

Estas declaraciones pueden ser importadas

y utilizadas por otros diseños utilizando la

clausula USE.

library IEEE;

use IEEE.std_logic_1164.all

Entity Declaration

• Ejemplo: Suponiendo que EX_PACK se

ha compilado en la librería DESIGN_LIB:

library DESIGN_LIB;

use DESIGN_LIB.EX_PACK.ALL;

Universidad de Zaragoza, IEC.

odf

ctl

• STD_LOGIC_1164

• STD_LOGIC_ARITH

❏

OUT_DATA(15:0)

IN_DATA(15:0)

DATA_RDY

VHDL

Architecture Body

Config. Declaration

Luis A. Barragán y José I. Artigas

Lenguaje VHDL - 12

DESCRIPCION DE LA

ARQUITECTURA

Arbol de directorios

/

❏

Introducción

❏

Estilos de modelado

❏

Sentencia PROCESS

❏

Sentencias secuenciales

– Sentencias de asignación

– Sentencia IF

– Sentencia CASE

– Sentencia LOOP

❏

Sentencia COMPONENT

❏

Ejemplo

VLSI1

home

synopsys

sd4

packages

usuario

IEEE

WORK

src

lib

std_logic_1164.vhd

std_logic_arith.vhd

...

Universidad de Zaragoza, IEC.

xxx.vhd

xxx.sym

xxx.sch

xxx.syn

xxx.sim

xxx.mra

Luis A. Barragán y José I. Artigas

Lenguaje VHDL - 13

Introducción

❏

Estilos de modelado (1)

La descripción de una arquitectura se

compone de un conjunto de sentencias

concurrentes que se ejecutan de forma

asíncrona entre sí y se comunican mediante

señales

❏

El orden textual de las mismas no importa

❏

La sentencia fundamental es el proceso que

define los límites de un dominio secuencial

❏

El resto de sentencias concurrentes son

formas particulares de procesos

Architecture

Statement A

Statement B

Signal Assignment

Process

Component

Block

Universidad de Zaragoza, IEC.

Statement C

Código vs. estilo de modelado

❏

ARCHITECTURE name OF entity IS

-- Declaración de items que serán utilizados

-- dentro del cuerpo de la arquitectura

BEGIN

Sentencias Concurrentes

PROCESS

Comportamental

Secuencial

Conjunto de procesos ejecutandose

asíncronamente

Concurrente

COMPONENT instantation

Estructural

END name;

❏

En la descripción de una arquitectura dada

se pueden mezclar los dos estilos de

modelado

❏

VHDL tiene un dominio secuencial en el

que opera un funcionamiento puramente

algorítmico y un dominio concurrente en el

que evolucionan los procesos a ritmo de

eventos discretos

Procedure

Generate

Assert

Luis A. Barragán y José I. Artigas

Lenguaje VHDL - 14

Estilos de modelado (2)

Nombre y pines de la entidad

RS_Latch

Q

RESET

❏

Ecuaciones Booleanas

Dominio Concurrente.

Q

N_RESET

0

0 1

1

1

1 0

Q

Descripción comportamental

Algoritmo secuencial.

—

SET RESET

0

0

1

1

Descripción comportamental

–

–

entity RS_Latch is

Port (N_SET : In BIT;

N_RESET: In BIT;

Q : Out BIT;

N_Q : Out BIT);

end RS_Latch;

Q

SET

❏

N_SET

❏

Estilos de modelado (3)

0

1

0

1

Q

Q

1

1

0

Q

1

0

1

Q

Universidad de Zaragoza, IEC.

architecture SEQUENTIAL of RS_Latch is

begin

process (N_SET, N_RESET)

begin

if (N_SET='1' and N_RESET='0') then

Q <= '0' after 2 ns;

N_Q <= '1' after 2 ns;

elsif (N_SET='0' and N_RESET='1') then

Q <= '1' after 2 ns;

N_Q <= '0' after 2 ns;

elsif (N_SET='0' and N_RESET='0') then

Q <= '1' after 2 ns;

N_Q <= '1' after 2 ns;

end if;

end process;

end SEQUENTIAL;

❏

Luis A. Barragán y José I. Artigas

architecture DATAFLOW of RS_Latch is

signal Qtmp, N_Qtmp: BIT;

begin

-- Q y N_Q son de modo OUT, no pueden ser leídos

-- no pueden aparecer en el lado derecho

-- de una sentencia de asignación

-- Solución definir señales temporales

Q <= Qtmp;

N_Q <=N_Qtmp;

Qtmp <= (not(N_SET)) or

(Qtmp and N_RESET) after 2 ns;

N_Qtmp <= (not(N_RESET)) or

(N_Qtmp and N_SET) after 2 ns;

end DATAFLOW;

Descripción estructural

SET

RESET

U1

Q

U2

Q

architecture STRUCTURE of RS_Latch is

component NAND2

port ( A, B : in BIT;

C

: out BIT);

end component;

begin

U1: NAND2

PORT MAP(N_SET, N_Q, Q);

U2: NAND2

PORT MAP(N_RESET, Q, N_Q);

end STRUCTURE;

Lenguaje VHDL - 15

Sentencia PROCESS (1)

Sentencia PROCESS (2)

❏

Un proceso es una sentencia concurrente

❏

❏

En el interior de un proceso las sentencias

se ejecutan en el orden secuencial marcado

por las sentencias de control de flujo de

programa típicas de un lenguaje

imperativo. La ejecución se hace en tiempo

cero.

Dominio Concurrente

Mecanismos para suspender un proceso:

– Lista de sensibilidades

– Sentencias WAIT

❏

Es un error:

– No utilizar ninguno de los dos

mecanismos en un proceso. El proceso

permanece en un bucle infinito

– Utilizar lista de sensibilidades y

sentencias wait en el mismo proceso

❏

Ejecución temporal de un proceso con lista

de sensibilidades

process (sensitivity list);

Dominio secuencial

end process;

process (sensitivity list);

-- Declarations (var.)

begin

-- Sequential stmts

end process;

❏

Un proceso puede

estar activo o en

suspenso. El proceso

se ejecuta hasta que

se suspende.

Universidad de Zaragoza, IEC.

process (A, B);

begin

Stmt_1;

z

Stmt_N;

end process;

Proceso

Activo

Activo

Eventos en

AoB

Suspenso

Suspenso

Luis A. Barragán y José I. Artigas

Lenguaje VHDL - 16

Sentencia PROCESS (3)

❏

Sentencia PROCESS (4)

La sentencia WAIT, suspende el proceso:

– Hasta que se cumple una condición,

Ej: wait until A=B;

– Hasta que se produce un evento en

señales, Ej: wait on A, B;

– Durante un intervalo de tiempo,

Ej: wait for 10 ns;

❏

Presencia de lista de sensibilidades en un

proceso ≡ wait on lista de sensibilidades

❏

Ejecución temporal de un proceso con

sentencia WAIT:

process

begin

Stmt_1;

z

wait on A, B;

Stmt_I;

z

Stmt_N;

end process;

Universidad de Zaragoza, IEC.

❏

Generación de una señal de reloj

-- Mal Comportamental

-- Si no hay ni lista de sensibilidades ni sentencias wait

-- El proceso siempre está activo y permanece en un bucle

infinito

CLOCK: process

begin

if CLK = '1' then CLK <= '0' after 10 ns;

else CLK <= '1' after 15 ns;

end if;

end process;

-- Comportamental1: Lista de sensibilidades

-- El proceso se suspende al ejecutar la última instrucción

-- Se reactiva cuando hay un evento en la señal CLK y

-- comienza la ejecución a partir de la primera sentencia

CLOCK: process (CLK)

begin

if CLK = '1' then CLK <= '0' after 10 ns;

else CLK <= '1' after 15 ns;

end if;

end process;

Suspenso

-- Comportamental2: Sentencia wait

CLOCK: process begin

if CLK = '1' then

CLK <= '0' after 10 ns;

else CLK <= '1' after 15 ns;

end if;

wait on CLK;

end process;

Eventos en

AoB

Activo

Luis A. Barragán y José I. Artigas

Lenguaje VHDL - 17

Sentencias secuenciales

❏

Sentencias de asignación

Para consultas sobre la sintaxis:

– Utilizar ayuda on-line iview &

❏

Asignación de señal:

– Nombre_sig <= expresion;

– Las señales a ambos lados del

operador de asignación deben ser del

mismo tipo

– Si hay varias asignaciones a la misma

señal dentro de un mismo proceso:

prevalece el valor de la última

– Pueden aparecer en sentencias

secuenciales y concurrentes

❏

Asignación de variable:

– Nombre_var := expresion;

– Los objetos a ambos lados del

operador de asignación deben ser del

mismo tipo

– Mantienen su valor a lo largo del ciclo

de simulación

– Sólo puede aparecer en el interior de

un proceso (dominio secuencial)

Sentencias de Flujo Control

IF

CASE

RETURN

LOOP

NEXT

EXIT

Sincronización

entre procesos

WAIT

Tipos de Sentencias Secuenciales

Subprogramas

PROCEDURE

FUNCTION

Universidad de Zaragoza, IEC.

Asignación de Señales

Asignación de Variables

Assertion

Luis A. Barragán y José I. Artigas

Lenguaje VHDL - 18

Sentencia IF

❏

Sentencia CASE

Sentencia IF:

– Cada una de las condiciones debe ser

booleana

– Si una condición es evaluada como

verdadera, el resto de las expresiones

no son evaluadas

❏

• when others

PROCESS

BEGIN

if S1='0' and S0='0' then

Z <= IN0 after 5 ns;

elsif S1='0' and S0='1' then

Z <= IN1 after 5 ns;

elsif S1='1' and S0='0' then

Z <= IN2 after 5 ns;

else Z <= IN3 after 5 ns;

end if;

wait on IN0,IN1,IN2,IN3, S1,S0;

END PROCESS

PROCESS (IN0, IN1,IN2,IN3,S1,S0)

subtype two_bits is BIT_VECTOR(1 downto 0);

BEGIN

case two_bits'(S1&S0) is

when "00" =>

IN0

Z <= IN0 after 5ns;

when "01" =>

IN1

Z <= IN1 after 5ns;

Z

MUX

when "10" =>

IN2

Z <= IN2 after 5ns;

IN3

when others =>

Z <= IN3 after 5ns;

S0 S1

end case;

END PROCESS;

IN0

IN1

MUX

Sentencia CASE

– Se escoge una y sólo una de las

alternativas

– Cuando no se cubren todas las

alternativas es necesario la inclusión

como última alternativa de :

Z

IN2

IN3

S0 S1

Universidad de Zaragoza, IEC.

Luis A. Barragán y José I. Artigas

Lenguaje VHDL - 19

Sentencia LOOP (1)

❏

❏

Sentencia LOOP (2)

Sentencia LOOP:

– La forma con while primero evalua la

condición y si ésta es verdadera se

ejecuta el contenido del bucle.

– La forma con for especifica un

número de iteraciones. La declaración

de la variable de iteración es implícita.

No se le puede asignar valores dentro

del bucle y no existe fuera de él.

Dentro de un bucle se pueden utilizar las

sentencias: NEXT y EXIT.

L1:

L2:

while A < 10 loop

for I in 0 to 10;

-- Sentencias

next L2 when I = A;

-- exit L2 when I = A;

-- Sentencias

end loop L2;

-- Sentencias

end L1;

Universidad de Zaragoza, IEC.

---------- COMPARADOR DE 4 BITS ---------entity COMP4 is

PORT(A, B: in BIT_VECTOR(3 downto 0);

AEQB, AGTB, ALTB: out BIT);

end COMP4;

architecture LOOP_BEH of COMP4 is

begin

process(A,B)

variable var_EQ : bit := '0';

variable var_LT : bit := '0';

variable var_GT : bit := '0';

begin

L1: for I in 3 downto 0 loop

if(A(I)=B(I)) then

var_EQ := '1';

else

var_EQ := '0';

if (A(I) = '1') then var_GT := '1';

else var_LT := '1';

end if;

exit L1;

end if;

end loop L1;

AEQB <= var_EQ;

AGTB <= var_GT;

ALTB <= var_LT;

end process;

end LOOP_BEH;

Luis A. Barragán y José I. Artigas

Lenguaje VHDL - 20

Sentencia COMPONENT

❏

Ejemplo (1)

Se utiliza para modelar una entidad como

un conjunto de componentes conectados

por señales

clock

CLK

I_1

Sentencia concurrente: el orden textual no

importa

– Un componente se puede instanciar un

número arbitrario de veces. Cada instancia

debe tener una etiqueta única

–

COUNT

RST

reset

RST

I_2

architecture STRUCT_A of GATING is

-- Declaración de componentes

component AND2

port (X, Y: in BIT; Z : out BIT);

end component;

component NAND2

port(A, B:in BIT;

MR

C:out BIT);

RDY

Q

end component;

S1

D

A

component DFF

QN S2

port(D, CLK:in BIT;

CLK

Q, NQ:out BIT);

CTL

CK

end component;

DIN

signal S1, S2 : BIT;

begin

-- Instanciación de componentes. Asocia

-- Asocia las señales de la entidad con los

-- puertos de los componentes

I_1: DFF port map (A, CK, S1, S2);

I_2: AND2 port map(S2, DIN, CTL);

I_3: NAND2 port map (C=>RDY, A=>S1, B=>MR);

end STRUCT_A;

Universidad de Zaragoza, IEC.

3bit_counter

CLK

Luis A. Barragán y José I. Artigas

I_3

entity reset is

PORT(RST: out bit);

end reset;

reset

RST

architecture rst_beh of reset is

begin

-- Forma de onda NO repetitiva

RST <= '0', '1' after 100 ns;

end rst_beh;

entity clock is

PORT(CLK: out bit);

end clock;

clock

CLK

architecture clk_beh of clock is

constant TCLK: time := 20 ns;

begin -- Forma de onda repetitiva

process begin

CLK <= '0', '1' after TCLK/2;

wait for TCLK;

end process;

end clk_beh;

Lenguaje VHDL - 21

Ejemplo (2)

MODELO DE TIEMPOS

entity 3bit_counter is

PORT(CLK,RST: in bit;

COUNT: out integer range 0 to 7);

end 3bit_counter;

architecture behavioral of 3bit_counter is

signal NEXT_COUNT: integer range 0 to 7;

signal COUNT_tmp : integer range 0 to 7;

begin

❏

Ciclo de simulación

❏

Tiempo de simulación es 2_D

❏

Señales vs. variables

❏

Asignación concurrente de señales

❏

Driver

❏

Múltiples drivers

COUNT <= COUNT_tmp;

process begin

wait until CLK='1';

COUNT_tmp <= NEXT_COUNT;

end process;

3bit_counter

CLK

process(COUNT_tmp, RST)

RST

begin

if (COUNT_tmp = 7) then

NEXT_COUNT <= 0;

else

NEXT_COUNT <= COUNT_tmp + 1;

end if;

if(RST = 0) then

NEXT_COUNT <= 0;

end if;

end process;

end behavioral;

Universidad de Zaragoza, IEC.

COUNT

Luis A. Barragán y José I. Artigas

Lenguaje VHDL - 22

Ciclo de simulación

❏

Tiempo de simulación es 2_D

La simulación

– Comienza con las asignaciones de señal

y todos los procesos suspendidos

– Los procesos reaccionan ante eventos en

ciertas señales

– Finaliza cuando no hay procesos activos

ni asignaciones de señal que hacer en

dicho tiempo T

Current

T

Simulation Time

❏

❏

∆

2nd Half

AWAKE

PROCESS

Existe al menos un retraso delta ∆ desde

que se asigna un nuevo valor a una señal

hasta que ésta adquiere dicho valor

*

E

2∆

*D

1∆

*C

Durante el ciclo de simulación el tiempo

físico no avanza

Universidad de Zaragoza, IEC.

-- Sea un conjunto de asignaciones

-- concurrentes de señales cuyos

-- valores iniciales son '0'

Next

Simulation Time

3∆

1st Half

UPDATE

SIGNALS

Retraso delta

– No se corresponde con ningún retraso

real. El tiempo físico de simulación no

avanza.

– Permite ordenar eventos que ocurren

en el mismo tiempo de simulación ⇒

La ordenación es causal

*

B

*

20 ns

B <= '1' after 20ns;

D <= C;

C <= B;

E <= D;

F <= E after 20ns;

F

*

40 ns

-- Una asignación concurrente se

-- ejecuta siempre que ocurre un

-- evento en una señal que aparece

-- en su lado derecho

* X, señal X es actualizada

Luis A. Barragán y José I. Artigas

Lenguaje VHDL - 23

Señales vs. variables (1)

❏

❏

Aunque ambas sintetizan en los mismos

elementos: cables o FFs, su semántica es

totalmente distinta.

La asignación de un nuevo valor a una

variable es instantanea.

– Visibilidad local. La declaración y

asignación de variables sólo puede

aparecer en el interior de un proceso

(dominio secuencial)

• No se recomienda el uso de variables

globales (VHDL'93)

❏

Señales vs. Variables (2)

La asignación de un nuevo valor a una

señal no es instantánea, existe al menos un

retraso ∆ .

– Z <= A0 and A1 [after 6ns];

– Son globales. No se pueden declarar

en el interior de un proceso

– Pueden aparecer en sentencias

secuenciales y concurrentes

Universidad de Zaragoza, IEC.

CONDICIONES INICIALES

A=0, B=1, C=2, X=3

PROCESS

-- A, B, C, X son variables

-- Declaración y asignación

-- dentro del proceso

BEGIN

-- wait until the trailing

-- edge of the clock

wait until Clock = '1';

-- variable assignments

A:= B+C; -- 1+2

X:= A+C; -- 3+2

A:= X+C; -- 5+2

END PROCESS;

A=7, X=5

Luis A. Barragán y José I. Artigas

PROCESS

-- A, B, C, X son señales

-- Las señales se han de-- clarado fuera del proceso

BEGIN

-- wait until the trailing

-- edge of the clock

wait until Clock = '1';

-- signal assignments

A<= B+C; -- 1+2

X<= A+C; -- 0+2

A<= X+C; -- 3+2

END PROCESS;

A=5, X=2

Lenguaje VHDL - 24

Asignación concurrente de

señales (1)

❏

Asignación concurrente de

señales (2)

Las sentencias de asignación de señales se

ejecutan en respuesta a eventos en alguna

de las señales que aparecen en el miembro

derecho de la asignación

– La señal no adquiere su nuevo valor

de forma instantanea, existe al menos

un retraso ∆ .

architecture A1 of INV is

signal B, C : bit;

begin

-- El orden textual

A

-- no importa

Z <= NOT C;

B <= NOT A;

C <= NOT B;

end A1;

B

C

❏

Una asignación concurrente se ejecuta

siempre que ocurre un evento en una señal

que aparece en su lado derecho

❏

Existe una sentencia PROCESS equivalente

Out <= In2 - In1 after 8 ns;

Z

❏

Asignaciones secuenciales vs. concurrentes

process(B)

begin -- Secuencial

A<= B;

Z <= A;

end process;

-- En T= 20 ns, ocurre evento en A

*

Z

2∆

*

C

1∆

*

B

3∆

*

* ns

20

Universidad de Zaragoza, IEC.

process (In1, In2)

begin

Ou t <= In2 - In1 after 8ns;

end process;

-- Concurrente

A<= B;

Z <= A;

B

A

B

B

A

C

A

Z

Z

Z

20ns

20ns + 3 ⋅ ∆

Luis A. Barragán y José I. Artigas

Lenguaje VHDL - 25

Multiples drivers

Driver

❏

Driver: lista de pares (valor, tiempo)

ordenados temporalmente (T, ∆) asociados

a una señal

❏

El driver de una señal representa la

evolución temporal futura de la misma

❏

La sentencia de asignación de señal crea en

el driver de la señal asignada un nuevo par

(valor, tiempo)

– El valor es el resultado de evaluar la

expresión de la sentencia

– El tiempo es igual a la suma del

tiempo actual de simulación (en el que

se ejecuta la sentencia) más el retardo

declarado a la derecha de la palabra

reservada AFTER.

Z

❏

Cada sentencia de asignación concurrente

asocia un driver a la señal modificada

❏

Una señal con más de un driver debe de

tener una función de resolución, en caso

contrario es un error.

('0', 5ns) ('1' ,10ns + 3∆)

'U'

'0'

5

Universidad de Zaragoza, IEC.

A

1

B

0

C

0

?

1

DR1:

DR2:

❏

Z

0

('0' , 10ns)

('1' , 5ns)

architecture A1 of TWO_DR is

begin

Z <= A and B after 10 ns;

Z <= not C after 5 ns;

end;

Función

de

Resolución

Z

Analogía entre función de resolución en

VHDL y los C.I. con salidas en colector

abierto: si existe un driver t.q. su valor =

'0', entonces la salida es '0'.

'1'

10

ns

Luis A. Barragán y José I. Artigas

Lenguaje VHDL - 26

DESCRIPCION DE

CIRCUITOS DIGITALES

❏

Introducción

❏

Circuitos combinacionales

❏

Circuitos secuenciales:

– Latches

– Flip-Flops

❏

Máquinas de Estados Finitos (MEFs)

Universidad de Zaragoza, IEC.

Introducción

❏

En este apartado se dan plantillas o

patrones que modelan distintos tipos de

circuitos digitales.

❏

Se indican algunos de los posibles

problemas que nos pueden aparecer:

– Diferencias Simulación vs. Síntesis.

❏

VHDL es muy flexible, y no todas sus

construcciones sirven para describir

circuitos.

– Nos centraremos en el subconjunto de

VHDL sintetizable para Synopsys.

Luis A. Barragán y José I. Artigas

Lenguaje VHDL - 27

Circuitos combinacionales

❏

Procesos => Cir. combinacionales

Sentencias de Asignación concurrentes =>

Lógica Combinacional

❏

library IEEE;

use IEEE.std_logic_1164.all;

entity COMBI is

port( A, B, C: in std_logic;

D: out std_logic);

end COMBI;

architecture BEHAVIORAL of COMBI is

begin

D <= (A and B) or C;

end BEHAVIORAL;

configuration CFG_COMBI of COMBI is

for BEHAVIORAL

A

end for;

end CFG_COMBI;

B

C

❏

D

Si una señal es leída en el interior de un

proceso y no aparece en la lista de

sensibilidad se producen diferencias entre

síntesis y simulación

process (A, B)

begin

D <= (A and B) or C;

end process;

process (A, B, C)

begin

D <= (A and B) or C;

end process;

Modelo VHDL original

Código interpretado

por la herramienta de

síntesis

No sintetiza asignaciones a señales con la

claúsula AFTER

C <= A and B after 10 ns;

❏

Procesos => Lógica Combinacional

process (A, B, C)

begin

D <= (A and B) or C;

end process;

Universidad de Zaragoza, IEC.

Luis A. Barragán y José I. Artigas

Lenguaje VHDL - 28

Sentencia IF => Circuitos

combinacionales (1)

❏

❏

Sentencia IF => Circuitos

combinacionales (2)

Tipo booleano

– Cierto => ‘1’

– Falso => ‘0’

❏

Las señales y variables (locales) mantienen

su valor hasta que se les asigna uno nuevo.

❏

Para asegurar que se sintetiza un circuito

combinacional, se debe asignar un valor a

la señal D_OUT independientemente de si la

condición de la sentencia IF es cierta o

falsa

La señal COND es leída dentro del proceso

y debe aparecer en la lista de sensibilidad

process(A, B, COND)

begin

-- Asignar valor a D_OUT

-- en todas las condiciones

if (COND) then

D_OUT <= B;

else

D_OUT <= A;

end if;

end process;

process(A, B, COND)

begin

-- Asignar valor a D_OUT

-- en todas las condiciones

if (COND) then

D_OUT <= B;

else

D_OUT <= A;

end if;

process(A, B, COND)

end process;

begin

-- Dar a D_OUT

-- un valor por defecto

D_OUT <= A;

if (COND) then

D_OUT <= B;

end if;

end process;

B

COND

D_OUT

A

Universidad de Zaragoza, IEC.

Luis A. Barragán y José I. Artigas

Lenguaje VHDL - 29

Sentencia CASE => Circuitos

combinacionales

❏

Las sentencias CASE no siempre se

sintetizan en multiplexores

❏

Para asegurar que se sintetiza un circuito

combinacional, se debe asignar un valor a

la señal Z para todo valor de SEL.

Latch

❏

process (Enable,Data)

begin

if (Enable='1') then

Value <= Data;

end if;

end process;

PROCESS (A,B,C,D,SEL)

BEGIN

case SEL is

when "00" => Z <= A;

when "01" => Z <= B;

when "10" => Z <= C;

when others => Z <= D;

end case;

END PROCESS;

process (Enable, Data)

begin

Value <= '0';

if (Enable='1') then

Value <= Data;

end if;

end process;

❏

A

B

MUX

Sentencia IF ⇒ Latch

Z

C

D

Data

Value

Enable

Data

Enable

Value

Si se desea evitar que la herramienta de

síntesis infiera latches, se debe asignar

valores a las señales y variables para todas

las condiciones de una sentencia IF o

CASE

SEL

Universidad de Zaragoza, IEC.

Luis A. Barragán y José I. Artigas

Lenguaje VHDL - 30

Circuitos secuenciales

❏

Flip-Flop

Se sintetiza un circuito secuencial:

❏

Instanciación de Flip Flops (o componentes con

FFs) en una descripción estructural

– Procesos activados por flanco de reloj en una

descripción comportamental

–

❏

process (CLK)

begin

if (CLK'EVENT and CLK='1') then

if (Reset = '1') then

Q <= '0';

else Q <= Data;

end if;

end if;

end process;

Patrones básicos (descrip. comportamental)

process begin

-- Flanco Ascendente

wait until CLK='1';

...

end process;

process (CLK)

begin

if CLK'EVENT and CLK='1' then

...

end if;

end process;

❏

process (CLK, RST)

begin

if RST= '1' then

...

elsif CLK'EVENT and CLK='1' then

...

end if;

end process;

Universidad de Zaragoza, IEC.

Flip Flop con RESET síncrono

Luis A. Barragán y José I. Artigas

Flip Flop con RESET y PRESET asíncronos

process (CLK, RST, PRT)

begin

if (Reset = '1') then

Q <= '0';

elsif (PRT = '1') then

Q <= '1';

elsif (CLK'EVENT and CLK='1') then

Q <= Data;

end if;

end process;

Lenguaje VHDL - 31

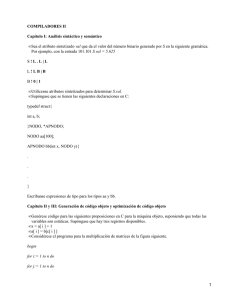

Máquinas de Estados síncronas

❏

Una MEF es una sex-tupla:

– Vector de estados S={Sj}

– Vector de entrada I={Ij}

– Vector de salida O={Oj}

– Función de transición I × S → S

– Función de salida I × S→ O

– Estado inicial o de reset R

MEFs

Tipos:

– MOORE, correspondencia entre

estado y vector de salida biunívoca

Función de salida S→ O

❏

I

Función de

Transición

Next

state

Registros

S

Función

de Salida

O

Current state

❏

❏

❏

Se utilizan para describir y simular

subsistemas de control

– MEALY, el vector de salida depende

del estado y del vector de entrada

Función de salida: I × S→ O

Niveles de descripción:

– Algorítmico ✓

– Tablas de Transición de estados

– Ecuaciones booleanas y registros

I

Descripción algorítmica. Requisitos:

– Claridad

– Sintetizable

Universidad de Zaragoza, IEC.

Función de

Transición

Next

state

Registros

S

Función

de Salida

O

Current state

Luis A. Barragán y José I. Artigas

Lenguaje VHDL - 32

Descripción en 2 procesos de

MEF síncronas

❏

Descripción en 2 procesos de

MEF síncronas

❏

Descripción en 2 procesos:

– Proceso secuencial, actualiza el estado

– Proceso combinacional, deriva el

siguiente estado y actualiza las salidas

– Para evitar "glitches", registrar salidas

ENTITY fsm

ARCHITECTURE Beh2 OF fsm

INPUTS

CASE

Para cada estado:

Transición de estados;

Generación de salidas;

OUTPUTS

Combinacional:

PROCESS( Current_state, All_inputs)

Secuencial:

PROCESS BEGIN

-- Un unico CLK

wait until CLK ='1';

Next_state

Current_state

END PROCESS;

Current_state <= Next_state;

Seq: PROCESS BEGIN

-- All FFs driven by the same clock

wait until CLK='1';

current_state <= next_state;

END PROCESS seq;

END beh2;

END PROCESS;

Universidad de Zaragoza, IEC.

Estructura General:

ARCHITECTURE beh2 OF fsm IS

type STATE_TYPE is (S0,S1,S2);

signal current_state, next_state: STATE_TYPE;

BEGIN

combi: PROCESS(current_state, all_inputs, RST)

BEGIN

signals <= default assignments;

CASE current_state is

WHEN S0 =>

0/0

IF input = '0' THEN

output <= '0';

S0

next_state <= S0;

ELSE

output <= '1';

1/1

next_state <= S2;

END IF;

unconditional signal generation;

S2

WHEN S1 =>

.................

WHEN OTHERS =>

-- Fail safe behavior

-- illegal state recovery

END CASE;

-- Power on reset initialization

IF reset_conditions THEN

transition to reset state R

and reset signals;

END IF;

END PROCESS combi;

Luis A. Barragán y José I. Artigas

Lenguaje VHDL - 33

SIMULACION

❏

Entornos de test

❏

Generación de estímulos

– Vectores de test

– Ficheros

Entornos de test

❏

Un entorno de test (test bench) es otra

entidad de diseño que se utiliza para verificar

la corrección funcional de nuestro diseño.

– Se pueden utilizar construcciones VHDL

no sintetizables.

❏

Partes de un entorno de test:

– Entidad a testear (EUT). Se instancia

como un componente

– Generador de Estímulos. Estos se aplican a los puertos de entrada de la EUT.

– Monitor de los resultados: Fichero de

datos o Waveform Viewer.

• Comparar resultados obtenidos con valores

esperados.

TEST BENCH

Generador

de Estímulos

Monitor de

Resultados

Universidad de Zaragoza, IEC.

Luis A. Barragán y José I. Artigas

CLK

RST,

IN_DATA

OUT_DATA

EUT:

Engloba todo

el hardware

que va a ser

sintetizado

Lenguaje VHDL - 34

Vectores de test almacenados

en tabla (1)

Generación de estímulos

❏

Los estímulos pueden:

– ser generados mediante código VHDL

no sintetizable

– ser vectores de datos almacenados en:

❏

Utilización:

– Los estímulos pueden ser vectores de

entrada almacenados en una tabla

– Los resultados esperados se pueden

almacenar junto con el correspondiente

vector de entrada para su comparación

con el resultado obtenido

❏

Ejemplo:

– Declaración

• vector o tabla

• fichero ASCII

❏

Generación de estímulos:

– Patrones NO Repetitivos

– Patrones Repetitivos

--No repetitivo

RST <= '1', '0' after 20 ns;

--Repetitivo

process begin

CLK <= '0';

wait for 10 ns;

CLK <= '1';

wait for 10 ns;

end process;

--Repetitivo

process begin

CLK <= '1', '0' after 20 ns;

wait for 50 ns;

end process;

Universidad de Zaragoza, IEC.

type test_vector is record

input1, input2, output: std_logic;

end record;

type test_vector_table is

array(natural range <>) of test_vector;

constant input_vectors: test_vector_table := (

(input1 => '0', input2 => '0', output => '0'),

...

(input1 => '1', input2 => '1', output => '1')

);

Luis A. Barragán y José I. Artigas

Lenguaje VHDL - 35

Vectores de test almacenados

en tabla (2)

Ficheros (1)

– Aplicación de estímulos a las entradas

de EUT y comprobación de las salidas

❏

Utilización:

– Los estímulos pueden ser vectores de

entrada almacenados en un fichero

ASCII

– Los resultados se pueden escribir en un

fichero para posterior comprobación

❏

Construcciones:

-- Instanciación de EUT

U1:eut port map(CLK=>actual_clk,I1=>actual_input1,

I2=>actual_input2, O=>actual_output);

-- Aplicación de los estímulos

process begin

for i in input_vectors'range loop

-- Aplicar vector de test

-- en el flanco de bajada del reloj

actual_clk <= '0';

actual_input1 <= input_vectors(i).input1;

actual_input2 <= input_vectors(i).input2;

wait for 10 ns;

actual_clk <= '1';

wait for 10 ns;

-- Comprobar resultados de simulación

assert(actual_output=input_vectors(i).output)

report "Resultado incorrecto";

end loop;

assert FALSE -- Parar la simulación

report "Fin";

end process;

Universidad de Zaragoza, IEC.

Package TEXTIO

-- Definiciones de tipos

type STRING is array (POSITIVE range <>) of CHARACTER

type LINE is access STRING;-- Pointer to a STRING value

type TEXT is file of STRING;

type SIDE is (RIGHT, LEFT);-- Justify output data

type WIDTH is NATURAL;-- Specify widths of output fields

-- Funciones y Procedimientos predefinidos

function ENDFILE (F: TEXT) return BOOLEAN;

procedure READLINE(F: in TEXT, L: out LINE);

procedure READ(L:inout LINE; VALUE:out <tipo>;

GOOD: out BOOLEAN);

procedure WRITELINE(F: out TEXT; L: in LINE);

procedure WRITE(L:inout LINE; VALUE:out <tipo>;

JUSTIFIED: in SIDE; FIELD: in WIDTH);

<tipo> cualquiera de los definidos en el package STANDARD

Luis A. Barragán y José I. Artigas

Lenguaje VHDL - 36

Ficheros (2)

❏

Ejemplo:

-- Instanciación de EUT

U1:eut port map(CLK=>actual_clk,I1=>actual_input1,

I2=>actual_input2, O=>actual_output);

-- Aplicación de los estímulos

READ FILE: process

file INPUT_FILE:

text is in "./eut_test.vec";

variable MY_LINE: line;

variable IN1, IN2, OUT: std_logic;

BEGIN

WHILE (NOT (endfile (INPUT_FILE))) LOOP

readline(INPUT_FILE, MY_LINE);

read (MY_LINE, IN1);

read (MY_LINE, IN2);

read (MY_LINE, OUT);

-- Aplicar valores leidos

actual_clk <= '0';

actual_input1 <= IN1;

actual_input2 <= IN2;

wait for 10 ns;

actual_clk <= '1';

wait for 10 ns;

assert (actual_output = OUT)

report "Resultado incorrecto";

END LOOP;

assert FALSE -- Parar la simulación

report "Fin";

END PROCESS;

Universidad de Zaragoza, IEC.

Luis A. Barragán y José I. Artigas

Lenguaje VHDL - 37