Arquitecturas de Máquinas Computadoras II

Anuncio

UNIVERSIDAD NACIONAL DE INGENIERIA

FACULTAD DE ELECTROTECNIA Y COMPUTACION

DEPARTAMENTO DE ARQUITECTURA Y SISTEMAS

Arquitecturas de Máquinas Computadoras II

José L. Díaz Chow

Curso 2016

Managua, Julio de 2016

Arquitectura de Máquinas Computadoras II

Guía de estudio para el estudiante

Elaborado por

Profesor José Díaz Chow

Última Revisión: Julio 2016

Universidad Nacional de Ingeniería, UNI.

Managua, Nicaragua.

INDICE DE CONTENIDO

1 INTRODUCCION A LA ARQUITECTURA DE COMPUTADORAS

1

1.1 INTRODUCCION A LA ASIGNATURA

1

1.2 EVOLUCION DE LAS COMPUTADORAS.

1

1.3 MÁQUINA SECUENCIAL DE PROGRAMA ALMACENADO.

6

1.4 ORGANIZACION DE LA COMPUTADORA.

7

1.4.1 ENFOQUE FUNCIONAL

8

1.4.2 ENFOQUE ESTRUCTURAL

9

2 ORGANIZACION DEL PROCESADOR

11

2.1 EL PROCESADOR

11

2.2 INSTRUCCIÓN Y CICLO DE INSTRUCCIÓN

11

2.3 ELEMENTOS PARA ESTRUCTURAR EL PROCESADOR

12

2.4 ESTRUCTURA BÁSICA DEL PROCESADOR

13

2.5 ARQUITECTURAS DE ACUMULADOR, PILA Y REGISTROS.

15

2.5.1 MÁQUINA DE ACUMULADOR

15

2.5.2 MÁQUINA DE PILA

17

2.5.3 MÁQUINA DE REGISTROS.

18

3 DISEÑO DEL CONJUNTO DE INSTRUCCIONES

21

3.1 INSTRUCCIÓN Y CONJUNTO DE INSTRUCCIONES

21

3.1.1 CONJUNTO DE INSTRUCCIONES

21

3.1.2 INSTRUCCIÓN

21

3.1.3 CLASIFICACIÓN DE LAS INSTRUCCIONES

22

3.1.4 FILOSOFÍAS DE DISEÑO DEL CONJUNTO DE INSTRUCCIONES

23

3.2 FORMATO DE INSTRUCCIONES

23

3.3 CODIGO DE OPERACIÓN

24

3.3.1 CODIFICACIÓN DE BLOQUE FIJO

24

3.3.2 CODIFICACIÓN DE BLOQUE EXPANDIDO

25

3.3.3 CODIFICACIÓN HUFFMAN

26

3.4 CAMPOS DE DIRECCIONAMIENTO

29

3.5 MODOS DE DIRECCIONAMIENTO

30

3.5.1 MODO INMEDIATO

30

3.5.2 MODO DIRECTO O DE REGISTRO

31

3.5.3 MODO ABSOLUTO O DIRECTO DE MEMORIA

31

3.5.4 MODO INDIRECTO DE REGISTRO

32

3.5.5 MODO INDIRECTO DE MEMORIA

32

3.5.6 MODO DE AUTOINCREMENTO

33

3.5.7 MODO DE AUTODECREMENTO

33

3.5.8 MODOS DESPLAZADOS

34

3.5.9 MODO INDIZADO O DE ÍNDICE

34

3.5.10 MODO BASE-DESPLAZAMIENTO

35

3.5.11 MODO BASE-DESPLAZAMIENTO CON ESCALACIÓN

36

3.5.12 MODO DE DESPLAZAMIENTO RELATIVO

36

3.6 CODIFICACIÓN DEL MD

37

4 UNIDAD DE EJECUCION

38

4.1 LA FUNCION DE PROCESAMIENTO

38

4.2 REPRESENTACION DE DATOS

38

4.2.1 REPRESENTACIÓN DE ENTEROS CON SIGNO.

39

4.2.2 NÚMEROS EN PUNTO FLOTANTE

40

4.2.3 OTROS TIPOS DE DATOS:

41

4.3 LA UNIDAD ARITMETICA

42

4.4 LA UNIDAD LOGICA

45

4.5 DISEÑO DE LA ALU

46

4.6 EXTENSIONES DE LA ALU

47

4.7 REGISTROS DE PROPOSITO GENERAL

47

4.7.1 DISEÑO DE LOS REGISTROS DE PROPÓSITO GENERAL O GPR

47

4.8 ARITMETICA EN PUNTO FLOTANTE

50

5. LA UNIDAD DE CONTROL

51

5.1 LA FUNCION DE CONTROL

51

5.2 OPERACIONES BASICAS DE CONTROL

52

5.3 PASOS DE CONTROL PARA LA EJECUCION DE UNA INSTRUCCION

54

5.4 UNIDAD DE CONTROL FIJO

59

5.5 UNIDAD DE CONTROL MICROPROGRAMADA

62

5.6 MICROPROGRAMA Y MICRORRAMIFICACIONES

68

5.7 APLICACIONES DE LA MICROPROGRAMACION

71

5 EL SISTEMA DE MEMORIA

72

5.1 LA FUNCIÓN DE ALMACENAMIENTO

72

5.2 CARACTERIZACIÓN DE LA MEMORIA.

73

5.3 ORGANIZACIÓN DE LA MEMORIA PRINCIPAL.

75

5.4 JERARQUÍA DE MEMORIA.

77

5.4.1 BASES DE LA JERARQUÍA DE MEMORIA

77

5.4.2 CARACTERÍSTICAS DE LA JERARQUÍA DE MEMORIA

78

5.5 SISTEMA DE MEMORIA CON CACHÉ

78

5.5.1 INTERCONEXIÓN CACHÉ - MEMORIA PRINCIPAL

79

5.5.2 ELEMENTOS DE DISEÑO DE LA CACHÉ

79

5.5.3 TÉCNICAS DE MAPEO

80

5.5.4 ALGORITMOS DE SUSTITUCIÓN DE BLOQUE

83

5.5.5 POLÍTICA DE ESCRITURA

84

6 EL SISTEMA DE ENTRADA-SALIDA

85

6.1 LA FUNCIÓN DE TRANSFERENCIA EXTERNA

85

6.2 ESTRUCTURA DE INTERCONEXIÓN DE LA COMPUTADORA

85

6.2.1 INTERCONEXIÓN CON BUSES

85

6.2.2 DISEÑO DEL BUS

87

6.2.3 BUSES ESTÁNDARES

88

6.3 COMUNICACIÓN CON DISPOSITIVOS EXTERNOS

90

6.3.1 DIRECCIONAMIENTO DE DISPOSITIVOS EXTERNOS

90

6.3.2 MODOS DE TRANSFERENCIA Y SINCRONIZACIÓN

91

6.4 ESTRUCTURA DEL MÓDULO DE E/S

92

6.5 INTERRUPCIONES

93

6.5.1 TIPOS DE INTERRUPCIONES

93

6.5.2 DISEÑO SIMPLE DEL SISTEMA DE INTERRUPCIONES

93

6.5.3 MÚLTIPLES DISPOSITIVOS

94

6.5.4 CONCURRENCIA DE MÚLTIPLES INTERRUPCIONES:

95

6.5.5 HABILITACIÓN E INHABILITACIÓN DE INTERRUPCIONES

96

6.5.6 ENMASCARADO SELECTIVO DE INTERRUPCIONES:

97

6.5.7 INTERRUPCIONES NO ENMASCARABLES:

97

6.5.8 EJEMPLO DE ÁRBITRO DE INTERRUPCIONES

97

6.6 ACCESO DIRECTO A MEMORIA

99

6.6.1 TRANSFERENCIA DE DATOS DE ACCESO DIRECTO A MEMORIA

100

6.6.2 MODOS DE TRANSFERENCIA DE DATOS DMA

100

6.6.3 CONFIGURACIONES DE DMA

101

6.6.4 ACCESO AL BUS DE MÚLTIPLES CONTROLADORES DE DMA

102

6.7 PROCESADORES Y CANALES DE E/S

103

6.7.1 CANAL SELECTOR

103

6.7.2 CANAL MULTIPLEXADO

104

6.7.3 CANAL MULTIPLEXADO POR BLOQUES:

104

6.8 INTERFACES ESTÁNDARES

105

6.8.1 INTERFACES SERIE

105

6.8.2 INTERFACES PARALELAS

109

A R Q U I T E C T U R A

D E

M Á Q U I N A S

C O M P U T A D O R A S

I I

1 INTRODUCCION A LA ARQUITECTURA DE COMPUTADORAS

1.1 INTRODUCCION A LA ASIGNATURA

El curso de Arquitectura de Máquinas Computadoras II incorpora tanto aspectos de Arquitectura

como de Organización de Computadoras. En éste, estaremos estudiando elementos del diseño e

implementación de las computadoras desde una perspectiva básica, orientada a conocer y comprender los

principios de diseño y el funcionamiento de las computadoras, con énfasis en el procesador o unidad central

de proceso (CPU).

Dado que los conceptos de Arquitectura y Organización están íntimamente relacionados, es importante

diferenciarlos. Para ello podemos partir de que:

Arquitectura son los atributos de un sistema que son visibles para un programador. Es decir, aquellas

características que determinan la ejecución lógica de un programa.

Conjunto de instrucciones, número de bits usados para representar datos, modos de

direccionamiento de los mismos, forma de codificación de las instrucciones, denominación de los

registros, puertos y mecanismos de E/S, técnicas para mapeo y direccionamiento de memoria.

Ejemplo: ¿Hay una instrucción de multiplicar?

Organización se refiere a cómo se implementan las características estructuralmente.

Estructura y funcionamiento de la ALU, Señales de control, buses e interfaces, tecnología de

memoria.

Ejemplo: ¿Hay una unidad de multiplicar o se hace por sumas repetidas?

Podemos relacionar la Arquitectura con la Organización si tomamos en cuenta que la organización es la forma

de implementar la Arquitectura. Por ejemplo, una Arquitectura puede tener diferentes implementaciones

generando familias de máquinas que tienen la misma arquitectura pero diferente organización. Esto permite

compatibilidad hacia atrás del software. Ejemplos claros de estas familias de máquinas son la IBM System/370

y la 80x86 de Intel.

1.2 EVOLUCION DE LAS COMPUTADORAS.

Históricamente podemos definir dos grandes eras en la evolución de las computadoras. La primera

denominada mecánica que comprende más o menos desde el año 1600 hasta 1943. En ésta se han registrado

una serie de artefactos de cálculo mecánico como la Pascalina, el cilindro de pasos de Leibniz, culminando

con una serie computadoras más o menos programables que empleaban relés electromecánicos.

La mayoría de estas máquinas no son de mucho interés, dada su tecnología y la asignatura que nos atañe, sin

embargo es importante anotar algunos hechos relevantes que fundaron los conceptos de la arquitectura de

computadoras como la conocemos hoy día. Anotaremos algunos de estos hitos:

Blaise Pascal (1642): Matemático.

Pascalina: suma y resta.

Docente: Ing. José Díaz Chow

Página 1

A R Q U I T E C T U R A

D E

M Á Q U I N A S

C O M P U T A D O R A S

I I .

Gottfried Leibniz (1673): Matemático e inventor.

Mejora Pascalina: Sumar, restar, multiplicar y dividir.

Antonius Braun (1727): Matemático

Primera calculadora mecánica completa.

Charles Babbage (1822): Matemático, “Padre del computador moderno”.

Máquina diferencial: Cálculo automático de tablas matemáticas.

Máquina analítica: Realiza cualquier operación matemática. (No se completó)

George Boole (1847): Análisis matemático lógico.

Investigación de las leyes del pensamiento, Algebra de Boole.

Herman Hollerith (1889): Máquina de tarjetas perforada moderna.

Constituyó la Tabulating Machine Company (IBM actual).

Redujo tabulación del censo de EUA de 7.5 años a dos meses.

Konrad Zuse (1938): Construyó el primer computador mecánico, el Z1.

Máquina binaria. Sin apoyo del gobierno. No quedan vestigios.

Howard Aiken (1943): Diseño el Harvard Mark 1.

Computador electromecánico inspirado en la máquina de Babbage.

En resumen, en la era mecánica se diseñaron computadores basados en dispositivos mecánicos para reducir

el tiempo de cálculo y aumentar la precisión de los resultados. Esto tuvo dos grandes desventajas: la velocidad

limitada debido a la inercia de los componentes móviles (engranajes y poleas) y un producto pesado, poco

fiable y costoso.

Destaca con especial connotación, la conceptualización de una máquina de propósito general, la máquina

analítica de Babbage que ya presenta un diseño basado en unidades especializadas (Mill, control, entrada y

salida) y el empleo de instrucciones para definir la operación a realizarse. Esta misma conceptualización fue

la base del éxito del Mark I (aunque lo venció la tecnología) e ingrediente de la arquitectura de computadoras

posterior.

La segunda era, en la cual aún vivimos, se denomina electrónica y se inicia en 1946 con el lanzamiento oficial

de la primera computadora electrónica de propósito general, el ENIAC.

El ENIAC (Electronic Numerical Integrator And Calculator) fue completado hasta en 1946, bastante tarde para

su propósito, pues el proyecto fue una respuesta a necesidades militares de los Estados Unidos en tiempos

de la segunda guerra mundial. El laboratorio de Investigación de Balística (BRL) del Ejército, una agencia

responsable del desarrollo de tablas de tiro y de trayectorias para nuevas armas, tenía dificultades para

elaborar tales tablas con exactitud y dentro de un plazo de tiempo razonable. Sin estas tablas de tiro, las

nuevas armas y piezas de artillería eran inútiles para los artilleros. El BRL empleó a más de 200 personas, la

mayoría mujeres; las cuales, utilizando calculadoras de mesa resolvían las ecuaciones balísticas necesarias.

La preparación de las tablas para una sola arma le habría llevado a una persona muchas horas, incluso días.

John Mauchly, un físico catedrático de Ingeniería Eléctrica de la Universidad de Pensilvania, y Presper Eckert

unos de sus alumnos de ingeniería eléctrica, propusieron construir un computador de uso general usando

Página 2

Docente: Ing. José Díaz Chow

A R Q U I T E C T U R A

D E

M Á Q U I N A S

C O M P U T A D O R A S

I I

tubos de vacío, para utilizarlo en las aplicaciones de la BRL. En 1943 esta proposición fue aceptada por el

ejército y se comenzó a trabajar en el ENIAC. La máquina era enorme: pesaba 30 toneladas, ocupaba 1,5000

(unos 9 x 15 metros) pies cuadrados. Contenía más de 1,8000 tubos de vacío, unas 70,000 resistencias, 10,000

condensadores, 6, 000 conmutadores y consumía 140 kilovatios de potencia. Su ventaja era su velocidad,

unas 1,000 veces más rápida que cualquier predecesor electromecánico, ya que era capaz de efectuar 5,000

sumas por segundo. Con el surgimiento del ENIAC se da la primera generación de Computadoras. Para hacer

justicia a la historia, debe mencionarse que aparentemente antes del ENIAC, Konrad Suze en Alemania diseñó

y construyó un computador electrónico completo y funcional, sin embargo éste fue destruido en la segunda

guerra mundial y no existe evidencia que respalde el dato histórico.

El ENIAC era una máquina decimal y no binaria. Es decir, los números estaban representados en forma

decimal y la aritmética se hacía también en forma decimal. Su memoria consistía en 20 acumuladores cada

uno capaz de mantener un número de 10 dígitos. Cada dígito estaba representado por una serie de diez

tubos de vacío. En un momento dado sólo un tubo estaba en ON representando un dígito. Uno de los mayores

inconvenientes del ENIAC era que tenía que ser programado mediante conmutadores e interconectando

cables.

Como hemos visto, la tarea de programar una máquina como el ENIAC era muy tediosa. Se llegó a la

conclusión que la programación de la misma sería más fácil y práctica si se pudiera especificar el programa

de alguna manera formal y sencilla que la máquina pudiera interpretar de la misma manera en que se

interpretan los datos. Es más, si estas “instrucciones” se guardaran en alguna parte de la memoria, el

procesador podría cargar y ejecutarlas secuencialmente desde allí. Esta idea conocida como Concepto de

Programa Almacenado, se atribuye a John Von Neumann, Matemático Húngaro asesor del proyecto ENIAC.

Paralelamente Turing, había propuesto la misma idea de una forma diferente basada en un autómata finito

que lee la definición de su comportamiento desde una cinta perforada. La arquitectura de Von Neumann,

especificada como modelo para la construcción de un computador de programa almacenado denominado

IAS, fue Implementada en 1952.

Los años 50 contemplaron el nacimiento de la industria de los computadores comerciales. Dos compañías

dominaron el mercado: Sperry e IBM. En 1947 Eckert y Mauchly se asociaron y crearon la primera

computadora con fines comerciales UNIVAC I que podía realizar tanto operaciones científicas como

comerciales. A la UNIVAC I siguió una serie de computadores comercializados por la Sperry-Rand, con un

predominante enfoque al campo científico.

Un hecho importante es la invención de la memoria de ferrita en 1952 por Jay Forrester en el MIT.

IBM por su parte sacó al mercado su primera máquina de programa almacenado en 1953: el 701, diseñado

sobre todo para aplicaciones de gestión. La serie que sucedió al 701 de IBM en los 50 la puso a la cabeza del

mercado de Computadores para negocios.

También en 1953 Fujitsu lanza la primera computadora japonesa: Facom100.

La segunda generación: Los transistores. El primer cambio importante en los computadores vino con

la sustitución de tubos de vacío por transistores. El transistor es más pequeño, más barato, disipa menos

calor, se puede conectar en placas discretas evitando las grandes masas de conductores y puede ser usado

de la misma manera que los tubos en la construcción de computadores. Este fue inventado en 1947 en los

laboratorios Bell y en los 50 provocó una gran revolución electrónica. Sin embargo las computadoras

totalmente transistorizadas emergieron hasta finales de la década. Con la nueva tecnología, aparecieron

nuevos nombres en el mercado cono NCR, RCA y la DEC, creadora de las populares PDP. IBM pronto consiguió

Docente: Ing. José Díaz Chow

Página 3

A R Q U I T E C T U R A

D E

M Á Q U I N A S

C O M P U T A D O R A S

I I .

cerrar la brecha y se puso a la cabeza en ventas con la serie 7000 donde destacó la 7094, que introdujo un

prefetch rudimentario y el multiplexor para organizar los accesos a memoria desde el CPU o los canales de

datos.

Emergen las supercomputadoras a principios de los sesentas.

Tercera Generación: Circuitos integrados. Con la introducción de la microelectrónica a mediado de

los 60 se pudo autocontener una cantidad de componentes discretos en un solo encapsulado, logrando

mejoras en la velocidad de transferencia entre los dispositivos internos. A esta época corresponden

máquinas con tecnología de pequeña y mediana escala de integración. La memoria, antes de núcleos de

ferrita, es semiconductora ahora. Surge la línea 360 de IBM y las PDP-5 / PDP-8.

La Cuarta Generación básicamente la pauta INTEL con la invención del chip microprocesador (P).

Un procesador completo autocontenido en un integrado, gracias a las ventajas de la tecnología MOS. Debido

al gran éxito de los microprocesadores Intel, pronto aparecen otros fabricantes en el terreno, como la

National Semiconductor, Zilog y Motorola.

El 4004. El primer P del mundo era de 4 bits y podía acceder a 4,096 palabras de 4 bits. Su repertorio consistía

de 45 instrucciones que limitaban bastante su campo de aplicación. En 1971, Intel lanzó el 8008, un P de 8

bits, con 3 instrucciones nuevas y memoria direccionable de 16K x 8. Todavía muy limitado para aplicaciones

grandes, el 8008 tuvo que ser reemplazado en 1973 por el 8080, el primer P moderno. El 8080 corría 10

veces más rápido que el 8008, podía direccionar más memoria y era TTL compatible lo que hizo al P viable

para muchas otras aplicaciones. Tenía 7 registros de 8 bits, un puntero de pila de 16 bits y un PC de 16 bits

también. Pronto las otras compañías empezaron la producción masiva de Ps de 8 bits. La explosión había

comenzado.

En 1977, Intel introdujo el 8085, que era sólo un poco más rápido que el 8080 e integraba el reloj y el

controlador del sistema al chip. Zilog introdujo el Z80 de 8 bits, con 80 instrucciones más que el 8008, bus de

direcciones de 16 bits (512K en RAM) y permitía interrupciones vectorizadas. El Z80 ha sido un procesador

muy popular en la industria de controladores de hardware para mando de procesos productivos. Por este

tiempo, también Motorola lanzó su procesador 6800 de 8 bits, 16 bits de direcciones, 2 registros de datos,

1 de índice y un SP, todos de 8 bits. Pronto lo siguieron el 6801, 6803 y el 6809 que duplicaba los índices y el

SP y podía multiplicar.

En 1978 se lanza el 8086 y un año después el 8088. Ambos eran dispositivos de 16 bits, con un tiempo de

ejecución de unos 400 ns/instrucción. Además podían direccionar hasta 1MB de RAM o 512K palabras de 16

bits. Esto permitió al P poder ejecutar las aplicaciones que se corrían en minicomputadoras pequeñas. Se

agregó hardware para multiplicar y dividir. La diferencia del 8088 con el 8086 era la búsqueda de

compatibilidad hacia atrás. El 8086 tenía una ruta de datos de 16 bits en tanto el 8088 la tenía de 8, además

su capacidad de prefetch variaba pues la cola del 8086 era de 6 y la del 8088 sólo de 4 bytes.

Por ese tiempo, National Semiconductor presenta el PACE de 16 bits y Texas Instruments saca al mercado su

TMS9900 que tenía todos sus registros en memoria (que para la época era más rápida que los registros).

Un hecho de necesaria mención es el surgimiento de la PC o microcomputadora personal de IBM en 1981,

que vino a revolucionar el mercado y las tendencias de la computación en los últimos años.

Página 4

Docente: Ing. José Díaz Chow

A R Q U I T E C T U R A

D E

M Á Q U I N A S

C O M P U T A D O R A S

I I

Pronto la revolución de los 16 bits cobra auge con la aparición de grandes mejoras en los diseños. Aquí vale

la pena mencionar el MC68000 de Motorola y el Zilog Z8000, el NS16032 de National, el i80286 y el MC68010.

El Z8000 tenía 16 registros de 16 bits utilizables como registros de 8, 16, 32 y 64 bits. Incluía multiplicación y

división de 32 bits. El 68000 era un procesador de 32 bits en realidad con empaquetado externo de 16. Su

bus de direcciones era de 24 bits y no usaba registros de segmentos. Estos procesadores permitían el uso de

dos modos de operación: usuario y supervisor o sistema operativo (protegido).

Los 80 trajeron la producción de chips de 32 bits y los procesadores RISC. El 80386 de Intel apareció en el 85.

Intel entró algo tarde a los productos de 32 bits. Sabemos que Motorola tenía procesadores de 32 bits

internos que mantenía como de 16 para estar en la competencia. Los laboratorios Bell y Hewlett Packard

habían lanzado ya procesadores de 32 bits al mercado al igual que la NS con el NS32032. Una serie de mejoras

a los procesadores de 32 bits se incluyen a finales de los 80 con la aparición del 80486 que ya incluye

características de paralelismo prestadas de RISC. Toman auge como competencia de Intel en la producción

de P, las compañías Cyrix, IBM y AMD. El campo de mayor producción y venta es el mercado de las

microcomputadoras del tipo IBM Compatibles, basadas en la familia 80x86 de Intel y sus competidores, con

lo cual se lucha por darle al microprocesador toda la potencia de las maxicomputadoras.

En el mundo del microprocesador, tan vasto, la ruta de los procesadores para IBM PC compatibles es más

fácil de seguir y afín a nuestro entorno, por tanto en el resto de esta breve reseña histórica, nos centraremos

en la evolución de estos procesadores.

En 1993, al 80486 le sucede el Pentium, un procesador de 32 bits con ruta de datos de 64. El Pentium

introduce mejoras grandes en su arquitectura, que se irán refinando con el tiempo. Los competidores lanzan

el respectivo “Pentium relative” 5x86 de Cyrix y luego el 6x86. AMD por su cuenta presenta el K5.

Al

Pentium le siguió el Pentium-Pro de Intel, diseñado para sistemas de alto rendimiento. Integra muchas

técnicas de paralelismo y una gran caché en el mismo chip.

El uso de gran volumen de información gráfica y sonido en los últimos años hizo que los fabricantes pusieran

especial interés en el paralelismo y los multimedios, con lo cual aparecen en escena el MMX y posteriormente

el Pentium II de Intel. Por su lado Cyrix presenta el Media GX y 6x86MMX para competir con Intel. AMD

presenta el K6 y el K6-2 con un nuevo repertorio gráfico “3D Now”. Con la introducción del Pentium II, Intel

clasificó sus procesadores en tres categorías, según su capacidad y mercado destino: Celeron (inicialmente

sin caché y luego con solo 128 KB a velocidad plena del CPU para una PC básica), Pentium II propiamente (de

512K de caché iniciales y orientado a estaciones de trabajo) y el Xeon que está especialmente diseñado para

servidores y que contaba con cachés de hasta 2Mb y velocidades de hasta 450 MHz.

Para evitar perder el liderazgo en el mercado, con la introducción del conjunto de instrucciones especializados

para multimedios y juegos de AMD, Intel reposta con la introducción de su propio conjunto extendido SSE

que integra en el Pentium III. La frecuencia del núcleo del procesador también es objeto de competencia y se

logran procesadores Pentium III de hasta 1,13GHz de frecuencia del núcleo y 133MHz en el bus del sistema

con la línea Coppermine. AMD introduce el Athlon, inicialmente de 1GHz y posteriormente Duron, de menor

precio, para competir con el Celeron.

Al Pentium III siguió el Pentium 4. Esta es una nueva y revolucionaria arquitectura que optimiza el paralelismo

obtenido en procesadores de 32 bits. Su frecuencia de núcleo básica es de 1.4 GHz, Nuevos Athlon y Duron

(este último, competencia del Celeron) de AMD han salido al mercado, Nuevas caras como Transmeta, han

emergido en la competencia de las pc móviles (notebooks, palms, etc). El Pentium 4 ha mantenido las tres

líneas de procesadores: Celeron con destino al mercado SOHO (Small Office and HOme) con frecuencias de

más de 2 GHz y 256kB de caché L2, el Pentium 4 para estaciones de trabajo y el Xeon para servidores. Estos

Docente: Ing. José Díaz Chow

Página 5

A R Q U I T E C T U R A

D E

M Á Q U I N A S

C O M P U T A D O R A S

I I .

últimos con frecuencias de hasta poco más de 4 GHz, nuevas técnicas paralelas como hiperthreading y cachés

L2 de 256 y 512 en el primero y hasta 1MB en el segundo.

Paralelamente al P4, Intel diseño y lanzó al mercado en el año 2001 una totalmente nueva arquitectura de

64 bits en un procesador denominado Itanium, orientado a estaciones de trabajo y servidores, que guarda

compatibilidad con la arquitectura de 32 bits. Ante la dificultad de aceptación del Itanium en el mercado, y la

introducción de procesadores de AMD de 64 bits, Intel lleva su arquitectura ix86 a un nuevo nivel

expandiéndola a 64 bits con compatibilidad binaria a su arquitectura de 32 bits original. Así hoy día tenemos

en la misma línea del procesador Pentium, sucesores del P4, dos opciones de arquitectura en el mismo CPU:

la x86 tradicional y la nueva x64 que tiene un nuevo repertorio de instrucciones con espacio de

direccionamiento de 264 bytes que remueve las barreras de 4GB de la arquitectura x86.

Es ahora como nunca antes que el microprocesador ha competido con las grandes máquinas. Hoy día es

posible encontrar una máquina de escritorio de menos de mil dólares con la misma capacidad de

procesamiento, memoria y almacenamiento que una mainframe de antaño de varios millones de dólares.

Actualmente la barrera de la frecuencia de núcleo se está ganando con paralelismo, por lo cual ya la oferta

de microprocesadores actuales en el mercado está dominada por procesadores multinúcleo que contienen

varios CPUs en un mismo chip.

Podemos finalizar diciendo que la computadora ha evolucionado a pasos agigantados desde sus orígenes a la

fecha, convirtiéndose probablemente, en la herramienta más versátil que haya inventado el hombre jamás.

La computadora ha generado toda una revolución social, tan importante como la agrícola y la industrial. Las

repercusiones de esta revolución se maximizan con las redes de computadoras, los dispositivos móviles y las

telecomunicaciones digitales. Esto ha definido una nueva era en la historia de civilización humana, la era de

la información o era del conocimiento. Era en que tenemos el privilegio de vivir.

1.3 MÁQUINA SECUENCIAL DE PROGRAMA ALMACENADO.

En uno de los reportes del proyecto ENIAC, John Von Neumann, que fungía como asesor matemático,

propone una nueva forma de diseñar y construir computadoras. Algunos de estos conceptos recogen ideas

anteriores, pero lo revolucionario de la propuesta de Von Neumann era el concepto de máquina secuencial

de programa almacenado. Este concepto establece que los principios de diseño de las computadoras deben

contemplar tres aspectos básicos:

a) Programa almacenado: Definición de instrucciones simples con las que se pueda programar

cualquier tarea de cálculo de la máquina en forma de una secuencia de instrucciones y la

posibilidad de cargar estos programas en la misma memoria que se cargan los datos.

b) Máquina secuencial: Una vez cargados el programa y los datos en la memoria, para realizar la tarea

de cómputo, basta lograr que la máquina realice el programa ejecutando instrucción tras

instrucción desde la memoria gracias a un secuenciador o dispositivo de control.

c) La implementación de tal máquina requiere cinco unidades funcionales (actualización del concepto

de Babbage): Un órgano de cálculo que ejecute las instrucciones, la memoria, el control, y

finalmente unidades de entrada y salida que permitan a la computadora obtener los datos y

programas del mundo exterior y entregar los resultados de los cálculos.

Página 6

Docente: Ing. José Díaz Chow

A R Q U I T E C T U R A

D E

M Á Q U I N A S

C O M P U T A D O R A S

I I

A tal especificación de diseño de máquinas computadoras se denominó Arquitectura Von Neumann o de

programa almacenado y constituyen hoy día la base de la arquitectura de computadoras modernas. Algunas

ventajas y características de la arquitectura de Von Neumann sobre las implementaciones de su época son:

Las secuencias de instrucciones o programas se podían guardar en la memoria y por tanto,

alimentar la máquina con nuevos programas para nuevas operaciones, modificar el programa en

tiempo de ejecución y tener un computador de verdadero propósito general.

La máquina secuencialmente ejecuta un ciclo de instrucción, leyendo instrucciones y

ejecutándolas una tras otra. El dispositivo de control recoge una instrucción desde la memoria,

interpreta su significado, trae los datos necesarios desde la memoria al órgano de cálculo, instruye

al mismo realizar la operación y luego almacena el resultado. Todas estas acciones implican traslado

de datos e instrucciones entre las unidades funcionales. Para ello existe una estructura de

interconexión. Los principales enlaces de ésta se muestran en la figura 1.1.

Entrada

Memoria

Control

Cálculo

Salida

Camino o Flujo de los Datos

Señales de Control desde la UC

.

Solicitudes o señales hacia la UC .

Figura 1.1. Unidades Funcionales de la Arquitectura Von Neumann

1.4 ORGANIZACION DE LA COMPUTADORA.

La arquitectura Von Neumann, ha sido el punto de partida de la mayoría de las máquinas computadoras

modernas. La organización de las unidades ha cambiado un poco hoy día con los avances en tecnología, sin

embargo la esencia aún se mantiene. Se han introducido nuevos enfoques respecto a cómo se describe una

organización y los términos aplicados. Adicionalmente, en la búsqueda de mejores prestaciones se han

definido nuevas técnicas de diseño basadas en paralelismo y ejecución no secuencial, que no se ajustan a la

arquitectura Von Neumann en algunas de sus características, pero éstas máquinas serán tratadas hasta en

Arquitectura de Máquinas Computadoras III.

La organización de una computadora puede definirse tanto de forma funcional como estructural. De manera

funcional se expresa en términos de las operaciones que se realizan y el flujo de los datos entre los

componentes funcionales. Estructuralmente, la organización se define en términos de los componentes

físicos que conforman el todo y sus relaciones. En nuestro caso, decimos que un ordenador es un sistema que

se compone de subsistemas, los cuales a su vez, se conforman de unidades o componentes. Los subsistemas

se interconectan y comunican mediante una estructura de interconexión.

Docente: Ing. José Díaz Chow

Página 7

A R Q U I T E C T U R A

D E

M Á Q U I N A S

C O M P U T A D O R A S

I I .

1.4.1 Enfoque Funcional

Las operaciones que una computadora es capaz de hacer son:

Procesamiento de datos

Almacenamiento de Datos

Traslado de datos

Operaciones de control

Por tanto se requieren cuatro elementos que ejecuten estas funciones. La figura 1.2 muestra la definición

funcional de una computadora con estos elementos.

Facilidad de

Almacenamiento

de Datos

Aparato de

Traslado de

datos

Mecanismo

de Control

Facilidad de

Procesamiento

de Datos

Figura 1.2. Vista funcional de la computadora

Las flechas muestran la interacción entre los elementos funcionales y el camino que seguirían los datos para

recibir servicio de las diferentes operaciones de la computadora. Por ejemplo, la operación de movimiento

de datos que se efectúa desde el teclado a la pantalla, seguirá el camino mostrado en la figura 1.3. El

camino de los datos se muestra con la flecha en color rojo.

Facilidad de

Almacenamiento

de Datos

Aparato de

Traslado de

datos

Mecanismo

de Control

Facilidad de

Procesamiento

de Datos

Figura 1.3. – Operación de traslado de datos

Página 8

Docente: Ing. José Díaz Chow

A R Q U I T E C T U R A

D E

M Á Q U I N A S

C O M P U T A D O R A S

I I

1.4.2 Enfoque Estructural

Estructuralmente, podemos considerar que la computadora se compone de tres componentes: El

sistema de procesamiento o procesador, el sistema de almacenamiento o memoria y el sistema de entrada /

salida que permite la comunicación con dispositivos periféricos u otras computadoras. Interconectando los

tres sistemas tenemos a la estructura de interconexión, que en las máquinas actuales se implementa

mediante buses. Una visión general de esta propuesta se puede observar en las figura 1.4.

Computadora

Periféricos

Memoria

Procesador

Computadora

Estructura de

Interconexión

E/S

Líneas de Comunicación

Figura 1.4. Estructura General de una Computadora

Las cinco unidades funcionales de la especificación original de Von Neumann, todavía son válidas, solo que

algunas de ellas se han unido para crear un subsistema. El órgano de cálculo junto al controlador constituye

el procesador o Unidad Central de Proceso (CPU). Por otro lado, la unidad de entrada y la de salida, son un

mismo subsistema al cual se denomina sistema de entrada / salida o E/S. La figura 1.5 muestra estas

relaciones.

CPU

Organo de Cálculo

Mecanismo de

Control

Estructura de Interconexión

Unidad de Entrada

Unidad de Salida

Sistema de Memoria

Sistema de E/S

Figura 1.5. Organización de la computadora orientada a partes o bloques constructivos.

Docente: Ing. José Díaz Chow

Página 9

A R Q U I T E C T U R A

1.4.2.1

D E

M Á Q U I N A S

C O M P U T A D O R A S

I I .

PROCESADOR O CPU

Desde una perspectiva más estructural, requerimos definir cómo la máquina ejecutará las

instrucciones. Estas instrucciones regularmente se traen de la memoria al CPU, donde se ejecutan. En este

proceso, el CPU requiere algún almacenamiento temporal interno. Para suplir esta necesidad se emplean

registros. Éstos no se muestran en la organización básica a bloques, ni tampoco el camino que los datos siguen

dentro del CPU. Una organización más detallada, muestra estos detalles arquitecturales y por lo general

define nuevas clasificaciones de unidades dentro del CPU.

Hoy día el órgano de cálculo de Von Neumann se denomina Unidad de ejecución o unidad aritmética y lógica

(ALU por sus siglas en inglés) y el mecanismo de control se denomina Unidad de Control. En el CPU, además

de los elementos de cálculo (ALU y opcionalmente otros dispositivos de cálculo especializado), se encuentran

los registros de almacenamiento temporal para manipulación de datos e instrucciones, las estructuras de

interconexión internas del CPU y los elementos de acceso a la estructura de interconexión general del

sistema.

1.4.2.2

SISTEMA DE MEMORIA

El sistema de memoria permite el almacenamiento de los datos y programas con los cuales interactúa

el ordenador. Podemos diferenciar, a groso modo, tres tipos de Almacenamiento: El Principal, el Secundario

y el Intermedio. El primero, llamado memoria principal, consiste en un arreglo de celdas de almacenamiento

de lectura /escritura donde deben residir los programas para que el procesador los pueda acceder.

Generalmente esta memoria es volátil, es decir, que una vez que se completa la ejecución del programa o se

apaga el ordenador los datos que no se almacenen en un medio permanente, se pierden.

El almacenamiento secundario también llamado masivo, es por lo general, permanente y permite almacenar

los datos y programas durante largo tiempo en forma de archivos. Está organizado de diferente manera que

la memoria principal, en función de la tecnología de implementación. Actualmente se emplean tecnologías

magnéticas y ópticas para implementar este tipo de almacenamiento en forma de discos y cintas.

El almacenamiento intermedio, también llamado cachés, permite acelerar el acceso a programas y datos

durante la ejecución.

1.4.2.3

SISTEMA DE ENTRADA / SALIDA

Esta es la interfaz al exterior de la computadora. Le permite obtener los datos y programas desde el

exterior y poder entregar los resultados del procesamiento o una copia de parte del almacenamiento

secundario al exterior. Generalmente se denominan periféricos a todos los dispositivos que pueden

conectarse al sistema de E/S y funcionar como dispositivos de entrada o salida de la computadora. Por

ejemplo, el teclado es la unidad de entrada estándar o predeterminada de la computadora y la pantalla del

monitor, la de salida.

Página 10

Docente: Ing. José Díaz Chow

A R Q U I T E C T U R A

D E

M Á Q U I N A S

C O M P U T A D O R A S

I I

2 ORGANIZACION DEL PROCESADOR

2.1 El Procesador

Los procesadores tienen como misión ejecutar operaciones de cómputo que le indica el programador.

Sabemos del modelo de Von Neumann que estas operaciones se definen como instrucciones. El procesador,

desde que recibe energía hasta que se apaga ejecuta constantemente instrucciones. Esta función de

procesamiento es la más importante en el funcionamiento de una computadora, por lo cual al procesador se

le denomina Unidad Central de Procesamiento o CPU. En esta unidad analizaremos las estructuras que

requiere un CPU muy sencillo para poder ejecutar una instrucción siguiendo los pasos del ciclo de Instrucción.

2.2 Instrucción y ciclo de instrucción

Como hemos estudiado antes, una instrucción es una orden que emite el programador al procesador

para que ejecute una de las operaciones que forman parte de su repertorio. La instrucción debe especificar

la operación a realizar y cómo obtener los datos u operandos para realizarla. Para este fin, la instrucción debe

tener una estructura lógica denominada formato de instrucción, que se estudiará más adelante.

La secuencia de pasos que sigue el procesador para ejecutar una instrucción se denomina Ciclo de

Instrucción. El Ciclo de Instrucción, se pueden organizar en dos bloques o fases de acuerdo a la acción que

ocurre. La primera fase, denominada FETCH o de Carga. Corresponde a los pasos necesarios para cargar la

instrucción desde la memoria al procesador.

La segunda fase, denominada EXECUTE, corresponde a aquellos pasos que permiten ejecutar la operación en

sí y almacenar el resultado:

-

FASE FETCH

-

Cargar la siguiente instrucción

Incrementar el secuenciador

Interpretar la Instrucción

FASE EXECUTE

Docente: Ing. José Díaz Chow

Cargar los operandos

Ejecutar la operación

Guardar el resultado

Verificar si hay solicitudes de interrupción

Página 11

A R Q U I T E C T U R A

D E

M Á Q U I N A S

C O M P U T A D O R A S

I I .

2.3 Elementos para estructurar el Procesador

Para poder realizar su función, el procesador, necesita una serie de estructuras. A continuación se

expondrá qué tareas requiere llevar a cabo un procesador muy simple y deduciremos qué elementos

constructivos se requieren para ejecutar estas tareas, siguiendo las pautas que nos brinda el ciclo de

instrucción.

Para estar preparado para realizar sus funciones, el procesador debe:

Poder acceder a memoria para leer las instrucciones y los operandos así como escribir los

resultados. Se necesita acceder a la dirección de memoria que apunta el PC para leer la próxima

instrucción. De acuerdo a la instrucción, puede requerirse leer de memoria los operandos y/o escribir

a memoria, los resultados de la operación. Para esto, el CPU debe tener un registro conectado al bus

de direcciones donde poner la dirección a acceder. A este registro lo llamaremos registro de dirección

de memoria o MAR por sus siglas en inglés. También requerimos otro conectado al bus de datos

donde poner el valor a escribir o tomar el valor leído desde la memoria. Este lo llamaremos registro

de datos de memoria o MDR por sus siglas en inglés. Por supuesto, se necesita una forma de indicarle

a la memoria que realice la operación de lectura o escritura y además poder saber cuándo la memoria

terminó la operación, sobre todo la de lectura. Hasta entonces el procesador puede asumir que en el

MDR hay datos válidos. Estas señales se implementan en la unidad de control: READ, WRITE, (que

puede ser una sola línea del Procesador R/W, 0 =R; 1 =W, además de alguna línea de habilitación de

Memoria.) y MFC (Que en nuestro caso será parte de la lógica de control de Memoria y que indicará

al CPU que la función de memoria se ha completado).

Llevar control de la secuencia de instrucciones: Se necesita un secuenciador de instrucciones, es

decir, un mecanismo que vaya indicando una a una las instrucciones a cargar desde la memoria. Para

ello, todas las instrucciones del programa a ejecutar deben estar almacenadas de forma secuencial

en la memoria. El secuenciador se implementa empleando un registro que inicialmente se hace

apuntar a la primera instrucción del programa y luego se incrementará para apuntala a la siguiente y

así en lo sucesivo. Este registro de llama contador de programa o PC por sus siglas en inglés. Este

enfoque es muy flexible pues el PC, puede incrementarse dentro del procesador una vez cargada la

instrucción para que apunte a la siguiente. Otra ventaja, es en el caso de la implementación de saltos

o llamados a subrutinas, pues sólo se pone en el PC la dirección destino del salto o la subrutina y así

controlamos el flujo de instrucciones en el programa.

Guardar la instrucción en un lugar donde la unidad de control la pueda interpretar. Para que durante

la ejecución de la instrucción, se pueda acceder a su contenido en cualquier momento, es necesario

otro registro para almacenar la instrucción durante la fase de ejecución. Este registro se le denomina

registro de instrucciones o IR por sus siglas en inglés. El IR está conectado directamente a los circuitos

de la unidad de control.

Poder realizar cálculos aritméticos y lógicos. Para esto el CPU requiere de una unidad de cálculos

aritméticos y lógicos a la que llamaremos ALU por sus siglas en inglés. Realiza todas las operaciones

aritméticas, como la suma y la resta. Y lógicas como AND, OR, XOR, NOT, etc. También realiza otras

operaciones como comparaciones y operaciones a nivel de Bits.

Obtener los operandos para realizar las operaciones. Estos pueden estar en memoria, ser definidos

directamente en la instrucción o residir en un almacenamiento interno del CPU. Es ventajoso

Página 12

Docente: Ing. José Díaz Chow

A R Q U I T E C T U R A

D E

M Á Q U I N A S

C O M P U T A D O R A S

I I

mantener los operandos dentro del CPU. Para esto se pueden disponer de registros de propósito

general con los cuales pueda la ALU realizar las operaciones.

Mantener el estado de la máquina. Para esto se requieren tener banderas y códigos de condición.

Por ejemplo, para comparar dos números se puede restar el primero del segundo y si el resultado fue

cero, podemos asegurar que son iguales. Si el resultado de diferente de cero y positivo, el primero es

mayor pero si es negativo, el segundo es mayor. Para llegar a estas conclusiones necesitamos

almacenar las condiciones de resultados como cero (Z), Signo (S), etc. Estas banderas y códigos se

almacenan en un registro llamado F o Flags.

Interpretar la instrucción y luego controlar la ejecución de todos los pasos para ejecutarla. Para

esto se requiere de una unidad de control o CU que tenga un decodificador capaz de interpretar los

diferentes campos lógicos del formato de instrucciones. Además esta unidad debe poder generar las

señales necesarias para que se realicen todos los pasos del ciclo de instrucción adecuadamente.

2.4 Estructura Básica del Procesador

Los elementos constructivos del CPU se organizan de acuerdo al trabajo que realizan. Para estructurar

coherentemente el procesador estos elementos se agrupan en unidades que se interconectan para

estructurar un todo. Cada elemento se debe comunicar con los otros para poder realizar su función. Esto se

logra a través de una estructura de interconexión. Existen dos formas de implementar esta estructura:

Uso de conexión directa: Consiste en realizar la conexión cableada directamente de la salida de

un elemento a la entrada del otro. En caso de requerirse lógica de enrutamiento, se emplean los

elementos digitales adecuados como multiplexores.

Uso de Buses: Consiste en definir un conjunto de líneas para interconectar múltiples elementos

entre sí. Debe, sin embargo, implementarse la lógica de control que garantice el enrutamiento

del dispositivo fuente al destino. Cabe mencionar que debe evitarse que dos dispositivos sean

fuente en el bus de forma simultánea pues esto provocaría cortocircuitos en las líneas cuando

esta esté sometida a dos valores lógicos diferentes.

La figura a continuación muestra un ejemplo de estructura de CPU con una posible interconexión de

los elementos mediante buses.

Docente: Ing. José Díaz Chow

Página 13

A R Q U I T E C T U R A

D E

M Á Q U I N A S

C O M P U T A D O R A S

I I .

CPU

R0

MAR

R1

.

.

.

Rn-1

MDR

Entrada / Salida

Bus Interno del Procesador

TMP

SP

Bus de Direcciones

ALUsel

Bus de Datos

Y

SOURCE

Bus del sistema

PC

ALU

IR

Z

Memoria

Unidad de

Control

FLAGS

READ

WRITE

IO/M

INTACK

INT

Figura 2.1 Elementos estructurales del procesador.

Adicionalmente se suele separar la estructura

del CPU en dos vistas: El camino de los datos o

Datapath y el control. Conforman el Datapath

todos los elementos por los que discurren los

datos dentro del CPU, especialmente la ALU, los

registros de propósito general, los registros de

acceso a memoria y los registros adicionales.

Dentro del Datapath se organizan los órganos

de cálculo (ALU y Registros de datos) en una

entidad lógica denominada unidad de

ejecución. Los registros de acceso al bus y

registros auxiliares se suelen organizar en una

unidad denominada “de Interfaz y carga de

instrucciones”.

CPU

Control

Líneas de Control

Unidad de

Control

Instrucciones

Señales de Control

Registros

de Propósito

General

ALU

Interfaz al Bus y

Carga de

Instrucciones

Direcciones y Datos

Flags

Unidad de Ejecución

Datapath

Figura 2.2. Organización del CPU en Datapath y Control

El control incluye a la unidad de control que se encarga de coordinar y realizar las acciones necesarias para

que se ejecuten las instrucciones.

Página 14

Docente: Ing. José Díaz Chow

A R Q U I T E C T U R A

D E

M Á Q U I N A S

C O M P U T A D O R A S

I I

Ejecución de la instrucción:

Habiendo definido una estructura organizativa para nuestro procesador, estudiemos de forma general, los

pasos para traer y ejecutar una instrucción basándonos en éstos elementos constructivos:

El PC tiene siempre la dirección de la próxima instrucción (Cuando la máquina se enciende, éste se

inicializa por hardware para apuntar la primera instrucción del programa de arranque). Primero el

contenido del PC es transferido al MAR y la unidad de control envía una señal de lectura a la memoria.

El PC es incrementado por el esquema de secuenciamiento para apuntar a la siguiente dirección.

Después de un cierto tiempo correspondiente al tiempo de acceso de memoria, la palabra direccionada

(la instrucción del programa) es leída de la memoria y cargada en el MDR.

El contenido del MDR es transferido al IR Ahora la instrucción esta lista para ser decodificada y ejecutada.

Si dicha instrucción involucra una operación que requiere operandos y estos residen en la memoria (ya

que podrían estar en los registros generales del procesador) tienen que ser traídos enviando su dirección

al MAR e iniciando un ciclo de lectura.

Cuando el operando ha sido leído y trasladado de la memoria al MDR, entonces será transferido del MDR

a la ALU o a algún registro de trabajo auxiliar para almacenarlo temporalmente mientras se traen otros

operandos. La operación se repite para traer todos los operandos, normalmente dos.

Se ejecuta la operación, mediante la ALU y el resultado es enviado al MDR si debe ser almacenado en

memoria o al registro destino en el CPU. Si los operandos o el resultado requiere acceso al subsistema de

E/S, se procese de igual forma que si se accede a Memoria, excepto que la UC se encarga de habilitar el

dispositivo específico en lugar de la Memoria.

2.5 Arquitecturas de Acumulador, Pila y Registros.

Dependiendo de la forma en que trae, almacena temporalmente y trata los operandos y el resultado,

los procesadores se han clasificado en tres tipos de arquitecturas o estilos de procesador: De acumulador,

de Registros y de Pila. Cabe mencionar que en la actualidad las máquinas más exitosas combinan

características de las tres aunque predominan las máquinas orientadas a registros.

2.5.1 Máquina de Acumulador

Este es el esquema típico de Von Neumann. En un procesador basado en un solo registro denominado

acumulador, de acuerdo a su función. Se carece de registros de propósito general para manipular los

operados dentro del CPU. Todo el trabajo se realiza el acumulador y la memoria. Hoy día esto parece

contraproducente, sin embargo, en el tiempo que esta arquitectura se implementó, la memoria era más

rápida que los registros del procesador y estos últimos eran extremadamente caros de producir. Para realizar

una operación, el programador debe tomar el primer operando y llevarlo al acumulador, realizar la operación

con el acumulador y el contenido de una dirección de memoria (el resultado se guarda en el acumulador) y

Docente: Ing. José Díaz Chow

Página 15

A R Q U I T E C T U R A

D E

M Á Q U I N A S

C O M P U T A D O R A S

I I .

finalmente transferir el contenido del acumulador a memoria. La figura 2.3 nos muestra una arquitectura

típica de acumulador.

PC

MAR

MDR

Memoria e

Interface de

E/S

IR

Acc

Unidad

de

Control

ALU

F

Figura 2.3. Ejemplo de estructura de una máquina de Acumulador.

En este tipo de procesador tenemos dos instrucciones de acceso a memoria: la que carga un dato al

acumulador y la almacena el acumulador en memoria. Las instrucciones binarias se realizan con el

acumulador como primer operando y un operando en memoria o definido directamente como número. Por

ejemplo:

INSTRUCCION

OPERACIÓN REALIZADA

LOAD X

LOAD (m)

LOAD n

STORE X

STORE (m)

ADD X

ADD (m)

ADD n

Acc M(X) ; X es una variable de memoria

Acc M(m) ; m es una dirección de memoria

Acc n

; n es un número entero.

M(X) Acc ; X es una variable de memoria

M(m) Acc ; m es una dirección de memoria

Acc (Acc) + M(X) ; X es una variable de memoria

Acc (Acc) + M(m) ; m es una dirección de memoria

Acc (Acc) + n

; n es un número entero.

Ejemplos de procesadores basados en acumulador son el IAS de Von Neumann, el M6502 y el 6809 de

Motorola. Este último cuenta con dos acumuladores A y B.

Página 16

Docente: Ing. José Díaz Chow

A R Q U I T E C T U R A

D E

M Á Q U I N A S

C O M P U T A D O R A S

I I

2.5.2 Máquina de Pila

Una máquina de pila es una computadora en la cual el elemento primario de almacenamiento de datos

para la CPU es una pila. Esta se implementa como un área de la memoria controlada por el CPU a la cual no

tienen acceso los programas del usuario. En las primeras máquinas de pila, todos los operandos se manejaban

mediante la pila, hoy día, sin embargo, la pila se emplea como una estructura de datos auxiliar para el CPU.

La ventaja principal de esta organización es que las manipulaciones de las pilas pueden ser realizadas en

una alta velocidad. La alta velocidad es una característica deseable en una computadora que va proporcionar

un servicio rápido de interrupciones, por ejemplo la IBM-370.

Las pilas más comunes son las de

empuje hacia abajo, es decir, que inician

en la dirección más alta de memoria y

crecen en el sentido de las direcciones de

memoria más bajas. La organización de la

máquina de pila es mostrada en la figura

2.4. El registro SP es el puntero a Pila, es

un registro que siempre tiene la dirección

de la última palabra insertada en la pila:

Tope de pila o TOS (Top of Stack). En

función de este registro, también se

puede obtener el elemento inmediato

bajo TOS: Próximo en pila o NOS (Next on

Stack).

PC

MAR

SP

Area de la

memoria para

pila

Resto de la

memoria

IR

Unidad

de

Control

temp

ALU

F

En el evento de una operación

binaria, el primer operando será

Figura 2.4 Ejemplo de estructura de una máquina de pila

removido de la pila y mantenido en el

registro TEMP. El segundo operando será

directamente llevado de la pila a la entrada derecha de la ALU, que en nuestro ejemplo corresponde al puerto

x o primer operando. El resultado de la operación es almacenado en la cabeza o tope de la pila.

Instrucciones típicas para una máquina de pila son:

Instrucción

Operación

PUSH X

PUSH (m)

PUSH n

POP Z

POP (m)

ADD

SUB

MUL

DIV

TOS M(X)

TOS M(m)

TOS n

M(Z) TOS

M(m) TOS

(TOS’) = (NOS) +

(TOS’) = (NOS) (TOS’) = (NOS) *

(TOS’) = (NOS) /

NOS: Next on the stack

Docente: Ing. José Díaz Chow

(TOS)

(TOS)

(TOS)

(TOS)

TOS: Top of the stack.

Página 17

A R Q U I T E C T U R A

D E

M Á Q U I N A S

C O M P U T A D O R A S

I I .

En la actualidad no existen ejemplos de esta organización en forma pura, sin embargo existieron

máquinas que se construyeron con esta arquitectura como las grandes computadoras Burroughs B5500,

B6500 y B6700 y la minicomputadora HP3000. Una de las ventajas de esta arquitectura es que el compilador

sólo necesita convertir a postfija las expresiones algebraicas y luego hacer una traducción directa a

ensamblador, empleando PUSH por cada aparición de variable y la operación correspondiente con cada

operando. El pop es un caso especial; que corresponde a la asignación y se evalúa al final y además arrastra

consigo al miembro izquierdo de la expresión.

2.5.3 Máquina de Registros.

La organización de un procesador de Registros Generales es mostrada en la figura 2.5. En este estilo de

diseño respecto al manejo de los operandos, se promueve el uso de muchos registros de propósito general

para almacenar los operandos temporalmente dentro del CPU. Esto tiene la ventaja que los datos más

frecuentes sólo se cargan una vez desde la memoria.

Una arquitectura típica consta de un banco o fichero de m registros de propósito general (Ro... Rm-1). Son

llamados de esta forma porque en cualquiera de ellos se pueden mantener datos, direcciones de memoria o

el resultado de alguna operación aritmética o lógica. El programador puede emplear estos registros para

realizar las diferentes operaciones en un programa. Algunos procesadores tienen algún destino específico

para algunos de ellos; el registro F (Flag) o PSW (Processor status Word) es un registro de banderas y/o

códigos de condición que mantiene información importante del estado del procesador o del desarrollo del

programa. Por ejemplo, cuando el resultado de una operación fue cero (bandera Z = 1) o cuando ocurrió un

acarreo (bandera C = 1).

PC

MAR

MDR

Memoria e

Interface de

E/S

R0

R1

IR

R2

Unidad

de

Control

Rm-1

ALU

F

Figura 2.5. Ejemplo de estructura de una máquina de Registros Generales

Con procesadores de registros generales podemos tener instrucciones de dos y tres operandos. En

máquinas 2 operandos, el destino o resultado de la operación está implícito en uno de los dos operandos.

Página 18

Docente: Ing. José Díaz Chow

A R Q U I T E C T U R A

D E

M Á Q U I N A S

C O M P U T A D O R A S

I I

Este fenómeno se denomina lectura destructiva de operandos, pues el valor del registro que es a la vez

operando y destino se pierde por sobre escritura del resultado.

Instrucciones de 3 operandos

Instrucción

Operación

ADD Rd, Rf1, Rf2

SUB Rd, Rf1, Rf2

MUL Rd, Rf1, Rf2

DIV Rd, Rf1, Rf2

; Rd Rf1 + Rf2

; Rd Rf1 - Rf2

; Rd Rf1 * Rf2

; Rd Rf1 / Rf2

Instrucciones de 2 operandos

MOV Rd, Rf

MOV Rd, n

MOV Rd, X

MOV Rd, (m)

MOV X, Rf

MOV (m), Rf

ADD Rf, Rd

SUB Rf, Rd

MUL Rf, Rd

DIV Rf, Rd

; Rd Rf

; Rd n | n es un número

; Rd M(X) ; X es una variable en memoria

; Rd M(m) ; m es una dirección en memoria

; M(X) Rf ; X es una variable en memoria

; M(m) Rf ; m es una dirección en memoria

; Rd Rf + Rd

; Rd Rf - Rd

; Rd Rf * Rd

; Rd Rf / Rd

Procesadores del tipo de registros de propósito general son la mayoría de las máquinas grandes modernas y

los procesadores RISC por excelencia. Ejemplos: IBM 370, VAX-11 de DEC, MC 68000 de Motorota, MIPS en

todos sus modelos, SPARC, PowerPC, ARM.

Los diseñadores modernos de computadoras, valorando las virtudes de cada estructura han adoptado

maneras de implementar máquinas con todas las ventajas de cada una, eliminando las limitaciones que

tenían cada una por separado. Por ejemplo, la familia 80x86 de INTEL, son máquinas orientadas a acumulador

con una cantidad no muy abundante de registros de propósitos generales con una pila integrada además.

Para entender mejor cómo varían las instrucciones respecto a cada estilo de CPU, se presenta a continuación

un ejemplo que permite hacer comparaciones entre los diferentes tipos. Se tiene la siguiente sentencia en

pascal: D:= A + B * C, Escriba la secuencia de instrucciones en lenguaje de máquina con tres, dos, una y una

y cero direcciones.

Tres operandos: (Suponer A está en R1, B en R2 y C en R3, R4 es D)

MUL R4, R2, R3

; D = (B) * (C)

ADD R4, R1, R4

; D = (A) + (B * C)

Dos operandos: (Suponer A está en R1, B en R2 y C en R3, R4 es D)

MOV R4, R3

;D = ( C)

MUL R2, R4

;D = (B)*(C)

ADD R1, R4

;D = (A) + (D)

Docente: Ing. José Díaz Chow

Página 19

A R Q U I T E C T U R A

D E

M Á Q U I N A S

C O M P U T A D O R A S

I I .

Un operando (Acumulador) :

LOAD B

; Acc= (B)

MULT C

; Acc= (A)*(C)

ADD A

; Acc= (Acc) + (A)

STORE D

; D = (Acc)

Máquina de Pila:

PUSH A

PUSH B

PUSH C

MUL

ADD

POP D

Página 20

; calcula B*C

; suma A a B*C

; salva resultado

Docente: Ing. José Díaz Chow

A R Q U I T E C T U R A

D E

M Á Q U I N A S

C O M P U T A D O R A S

I I

3 DISEÑO DEL CONJUNTO DE INSTRUCCIONES

3.1 INSTRUCCIÓN Y CONJUNTO DE INSTRUCCIONES

La principal especificación arquitectónica de una computadora o su procesador es quizás el conjunto

de instrucciones, pues éste define las operaciones que puede realizar el procesador y establece cómo el

programador puede instruir su ejecución. Bien podría decirse que el repertorio de instrucciones es la

“identidad” del procesador o su lengua, pues cada arquitectura de procesador diferente tiene un conjunto

de instrucciones diferente. Solo aquellos procesadores que comparten el mismo conjunto de instrucciones

pueden ejecutar los mismos programas, y por tanto se dice de ellos que pertenecen a una misma “familia de

arquitecturas”

3.1.1 Conjunto de Instrucciones

Podemos decir que las instrucciones son comandos que indican al procesador qué operación ejecutar

en cada momento y con cuales operandos. Se denomina conjunto o repertorio de instrucciones a todas las

posibles instrucciones para un procesador específico. El diseño del conjunto de instrucciones es el punto de

partida de toda arquitectura de computadoras.

Es deseable que el conjunto de instrucciones del CPU cumpla con las siguientes características:

Completitud:

Ortogonalidad:

Eficiencia:

3.1.2

El conjunto de instrucciones debe permitir ejecutar todas las operaciones

que es capaz de realizar el procesador.

Debe permitir que todas las operaciones se realicen con todos los tipos de

datos que aplican para la misma.

Debe permitir ejecutar todas las operaciones del procesador pero sin

redundancias. Si ya una operación puede realizarse con una instrucción x

no es eficiente que exista una instrucción y para la misma operación.

Instrucción

Denominamos instrucción a un tipo especial de dato que se emplea para ordenar al CPU que ejecute

una de las operaciones que puede realizar. En términos generales, la instrucción debe tener información

acerca del tipo de operación a realizar, con qué operandos, dónde poner el resultado (si la operación genera

alguno) y alguna forma de obtener la próxima instrucción. En las máquinas del tipo Von Neumann, que son

máquinas secuenciales, se supone que la próxima instrucción está contigua en la memoria. En este caso, la

información de próxima instrucción es implícita. Este esquema de secuenciamiento requiere de un puntero

o contador de programa que se incremente de forma automática para que siempre señale a la próxima

instrucción a ejecutar. Para estos propósitos se emplea un registro del CPU denominado normalmente PC

(Program Counter).

Una instrucción debe, por tanto determinar: la Operación a ejecutar y los Operandos (tanto fuentes como

destino) a emplear en la misma. El secuenciamiento implícito se puede cambiar mediante instrucciones de

Docente: Ing. José Díaz Chow

Página 21

A R Q U I T E C T U R A

D E

M Á Q U I N A S

C O M P U T A D O R A S

I I .

salto que permiten modificar el PC. Los Operandos pueden especificarse de forma explícita o implícita

(cuando están sobreentendidos) en la instrucción. Por ejemplo, las instrucciones de salto no hacen referencia

al PC pero está sobreentendido que éste es el destino de esas operaciones.

Los operandos pueden residir en registros internos del procesador o en la memoria. Los operandos fuentes

también se pueden especificar directamente en la instrucción. Las diferentes formas de obtener los

operandos desde donde residan se denominan modos de direccionamiento. Los operandos que residen en

memoria pueden especificarse mediante muchos diferentes modos de direccionamiento.

3.1.3

Clasificación de las Instrucciones

Podemos clasificar las instrucciones en categorías o tipos de acuerdo a la operación que realizan. En

la tabla a continuación se presenta un cuadro sinóptico con el detalle de esta clasificación.

Tipo

Propósito General

Propósito

Específico

Privilegiadas

Categoría

Ejemplos

Mover datos entre operandos

( puede ser R-R, R-M).

* Cambios en los tamaños y extensión de

Signo

MOVE, LOAD,

STORE

Aritméticas

Operaciones aritméticas.

ADD, SUB, DIV,

MULT, INC, DEC

Lógicas y manejo de

bits (bitwise)

Operaciones lógicas, de comparación y

corrimiento de bits.

AND, OR

RSHIFT, NOT

De Comparación

Operaciones que comparan los valores de

los operandos. Sirven de base para las de

saltos

CMP

Control de flujo de

Programa

Permite modificar la secuencia del

programa para implementar sentencias de

selección, ciclos y llamadas a subrutinas.

JP, JR, BRN, CALL,

RET

E/S

Permite el acceso a direcciones del

espacio de E/S. (Más adelante se

explicará que hay ordenadores que usan

las de transferencia cuando el Mapa de

E/S está Integrado a M)

IN, OUT

Tratamiento de

Cadenas (Strings)

Manipulación de cadenas

COMSTR, CATSTR

Polinomios y

funciones científicas,

Vectores y Matrices

Para aplicaciones científicas. La

instrucción implementada en Hardware

acelera la ejecución. También se

consideran datos especiales como

Vectores, Listas y Matrices

Solicitud de atención de los dispositivos

de E/S y Tratamiento de condiciones

anormales del procesador

EVALUATEPOL,

VADD

Protección de Memoria, Detención del

programa, reinicio o detención del

ordenador, etc.

HALT, NOP

Interrupciones y

Excepciones

De control del

Sistema

Página 22

Uso

Transferencia

INT, Trap

Docente: Ing. José Díaz Chow

A R Q U I T E C T U R A

3.1.4

D E

M Á Q U I N A S

C O M P U T A D O R A S

I I

Filosofías de Diseño del Conjunto de instrucciones

Existen básicamente dos filosofías en torno al diseño del conjunto de instrucciones. Al inicio, el diseño

de las computadoras estaba orientado a proveer al programador con el mayor posible conjunto de

instrucciones con muchas formas de obtener los operandos (modos de direccionamiento), lo cual iba

haciendo el hardware cada vez más complejo y mayor el recargo de trabajo para la decodificación y ejecución

de las instrucciones. Un estudio reveló que era muy reducido el conjunto de éstas que en realidad se

utilizaban y se propuso una nueva filosofía de diseño, basada en el conjunto de instrucciones reducido que

realmente era utilizado con frecuencia y simplificar los modos para reducir la complejidad del hardware y

mejorar el desempeño. Esta corriente filosófica se denominó RISC (Computadora de conjunto reducido de

instrucciones) y a las máquinas con la tendencia de conjunto muy amplio, anteriores a ella se llamó CISC

(Computadoras con conjunto complejo de instrucciones).

A continuación se presenta un cuadro comparativo de estas dos tendencias.

RISC

CISC

Pocos formatos de instrucciones y sencillos

permiten decodificador rápido y control

cableado.

Muchos formatos muy complejos que

normalmente requieren unidad de control

microprogramada.

Las operaciones de cálculo son registroregistro. Instrucciones específicas de carga y

almacenamiento.

Las operaciones permiten operandos en

memoria.

Usan la mínima cantidad de modos de

direccionamiento.

Buscan permitir la máxima cantidad de modos

de direccionamiento.

Programas largos pero sencillos.

Programas cortos pero complejos.

Más fácil de segmentar por su sencillez.

Más difícil de segmentar y controlar.

Mayor rapidez de ejecución.

Ejecución más lenta (complejidad + UC Prog)

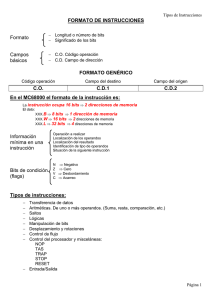

3.2 FORMATO DE INSTRUCCIONES

Una instrucción es un tipo de dato especial que se almacena en la misma memoria en que se

almacenan los datos y de la misma forma, por tanto es una cadena de bits. Lo importante es que estos bits

están organizados de cierta forma para almacenar la información que debe proveer la instrucción. Tal

organización se denomina Formato de instrucción. Este define el tamaño de la instrucción y los campos de

información de la misma.

El formato de instrucción puede ser fijo o variable. En el primero, el tamaño de la instrucción es estático, por

ejemplo, siempre de 32 bits. En el segundo el tamaño depende de la instrucción y puede ser de una palabra,

dos o más. Por ejemplo, el Z80 tiene formatos de 1, 2 y 3 bytes.

Docente: Ing. José Díaz Chow

Página 23

A R Q U I T E C T U R A

D E

M Á Q U I N A S

C O M P U T A D O R A S

I I .

El formato de instrucción, por lo general se organiza en campos. Cada campo posee un tipo de información,

algunas arquitecturas, sin embargo, tienen campos compuestos y otras mezclan información en un mismo

campo. Ejemplos: MIPS siempre mantiene un mismo código de operación para el tipo de instrucción y

mantiene un campo fijo para cada operando, mientras la familia ix86 tiene un código de operación diferente

por cada tipo y cantidad de operandos de la misma operación.

El formato de instrucción debe contener toda la información de la instrucción o la forma de obtenerla,

básicamente:

- Operación a realizar

- Fuente(s): Dependen del tipo de operación (unaria o binaria)

- Destino: Dónde poner el resultado. A veces está implícito ( ADD A, B ; B A + B )

- Secuenciamiento: Necesidad de conocer la dirección de la próxima instrucción. Por lo general está

implícito (en las arquitecturas de máquina secuencial) pero a veces se permite cambiar el flujo de

programa afectando al PC mediante instrucciones de ramificación (en este caso el direccionamiento

puede ser absoluto o relativo).

Nominalmente, el Formato de instrucción, al cual llamaremos F, se compone de Dos partes:

-

Identificación de la operación: COP o CO: Código que identifica la operación.

Direccionamiento: Operandos fuentes y destino.

IDENTIFICACION

DIRECCIONAMIENTO

CO

OP1

MD

OP2

…

OPn

VALOR(ES)

Estructura del Formato de Instrucción

3.3 CODIGOFigura

DE 2.4

OPERACIÓN

Es necesario codificar las instrucciones del conjunto de instrucciones a fin que la unidad de control

pueda identificar de forma única cada instrucción y proceder de acuerdo a la especificación de la misma. La

parte del formato de instrucción que mantiene esta información se denomina bloque de identificación y

está conformado por lo general de un único campo llamado Campo de Código de Operación (CO o COP).

3.3.1 Codificación de bloque fijo

¿Cómo podemos proceder para asignar códigos a las instrucciones? es decir, ¿cómo podemos codificar el

CO? Existen varias técnicas, la más simple consiste en asignar a cada instrucción una de las combinaciones

posibles de un patrón binario. A esta técnica se le conoce como Técnica de Bloque fijo. Para codificar n

instrucciones se requieren log2(n) bits. Por ejemplo, para codificar 13 instrucciones 4 bits son requeridos.

nota: n = n (I); n es la cardinalidad del conjunto I o conjunto de instrucciones.

Página 24

Docente: Ing. José Díaz Chow

A R Q U I T E C T U R A

D E

M Á Q U I N A S

C O M P U T A D O R A S

I I

Ventajas:

Muy fácil de entender

Decodificado fácil de implementar

Desventajas:

Cuando el número de instrucciones no es cercano a la potencia (5 bits para 18)

Tenemos desperdicio o a veces diseños muy costosos (al integrar el resto del

Formato)

3.3.2 Codificación de bloque expandido

Otra técnica empleada es la Técnica de bloque expandido. Esta se basa en el hecho que no todas

las instrucciones usan todos los campos de direccionamiento. Se pueden identificar grupos de 3, 2, 1 y 0

operandos, entonces, se pueden emplear pocos bits para el CO de las instrucciones de más operandos y en

el nuevo grupo usar los bits del operando que no ocupará el anterior para “expandir” el CO a más bits.

Ejemplo: ¿Cuántos bits ( L o longitud) se requieren para el formato de instrucciones de una máquina hipotética, si se tienen

que codificar 15 diferentes instrucciones cada una de 2 operandos, donde el operando fuente 1 asume como destino de la

operación y cada operando requiere 6 bits para codificarse?

L (F) = ?

n = 15

L (CO) = log2(15) = 4 bits

L (F) = L (CO) + 2 * L (Op) = 4 + 2 * 6 = 16 bits

*Nótese que aquí la longitud de los operandos es constante, existen máquinas donde no ocurre lo mismo.

Suponga, ahora que además de las 15 de 2 operandos requiero 30 de 1 operando. ¿Cuántos bits se

requieren?

n = 15 + 30 = 45

L (CO) = log2(45) = 6 bits

En este nuevo escenario, la instrucción pasa a tener un total de 18 bits. Note que esto genera un

problema interesante, pues si la resolución de la memoria es de un byte y no de palabras de 18 bits, el tamaño

de instrucción deberá escalar a 3 * 8 = 24 bits, desperdiciando 6 bits en el formato. Esto no siempre es malo,

en términos de rendimiento, pero puede ser un inconveniente en cuanto a ahorro de espacio en disco y

memoria.

Para evitar el desperdicio del ejemplo anterior, se podría usar la técnica de bloque expandido, así los

6 bits que libera el segundo operando en este nuevo grupo, se pueden emplear para “expandir” el CO. Es

importante que queden algunas combinaciones libres del primer formato para poderlas usar como llave que

nos indique que esa combinación es expandida. En esta caso queda la combinación 1111. Así el decodificador

sabrá que cuando aparezca ésta encabezando el CO, éste será de 4 + 6 = 10 bits.

Docente: Ing. José Díaz Chow

Página 25

A R Q U I T E C T U R A

CO

0000

…

1110

1111

O2

xxxxxx

…

xxxxxx

D E

M Á Q U I N A S

O1

xxxxxx

…

xxxxxx

1111 000000

… …

…

1111 011101

xxxxxx

30

xxxxxx

C O M P U T A D O R A S

I I .

15 inst. de 2 operandos

inst. de 1 operando

Nótese que con este formato, no se requieren más bits para codificar las nuevas 30 instrucciones.

* Asignación: Verifique cuántas instrucciones de 0 operandos podrían caber en el formato

3.3.3 Codificación Huffman

La tercera técnica, se basa en la teoría estadística de la comunicación y está orientada a minimizar

la longitud del CO de las instrucciones más frecuentes. Ésta de denomina Técnica de Codificación de

Huffman. La técnica expandida asume que todas las instrucciones son usadas con la misma probabilidad,

pero realmente en la práctica esto no es así, ya que en un programa de acumulador, el 40% de las

instrucciones son LOAD y STORE, por ejemplo. La técnica de Huffman codifica el CO de las instrucciones

usadas más frecuente con menos bits y las usadas menos frecuentemente con más bits. Esto permite que

el número promedio de bits necesarios para codificar un programa típico sea óptimo.

Ejemplo: Supongamos que se desea codificar el conjunto de instrucción hipotético mostrado en la tabla

siguiente:

Nemónicos de

Instrucciones

Contador de Frecuencia Relativo

LOAD

STO

ADD

AND

NOT

RSHIFT

JUMP

HALT

1/4

1/4

1/8

1/8

1/16

1/16

1/16

1/16

Los valores del contador de frecuencia relativa se obtienen inspeccionando la ocurrencia de cada

Instrucción en un conjunto de programas representativos. En ésta técnica podemos especificar un

algoritmo para crear los Códigos para cada CO de cada instrucción. Primero se ordenan las instrucciones

en función de su frecuencia relativa o probabilidad de ocurrencia, de mayor a menor de izquierda a

derecha. Segundo, se asigna a cada nemónico de Instrucción un nodo etiquetado con el contador de

frecuencia relativa correspondiente (figura a continuación)

Página 26

Docente: Ing. José Díaz Chow

A R Q U I T E C T U R A

LOAD STO

¼

D E

ADD

¼

M Á Q U I N A S

AND

NOT

1/8

1/16

1/8

C O M P U T A D O R A S

I I

RSHIFT JUMP

HALT

1/16

1/16

1/16

Tercero: Asociar los nodos con el menor peso siempre, mediante la operación suma para genera nuevos

nodos hasta que no queden posibles asociaciones. La figuras 2.8 a, b y c muestran este proceso.

Cuarto: Las ramas derechas del árbol obtenido son etiquetadas con “0” y las izquierdas con “1”. Ver el

resultado de este proceso en la Figura 2.8 c.