Programa año 2015

Anuncio

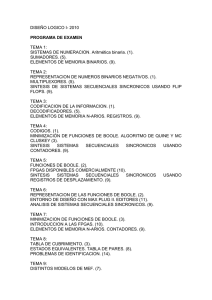

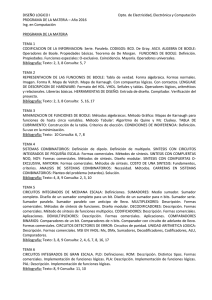

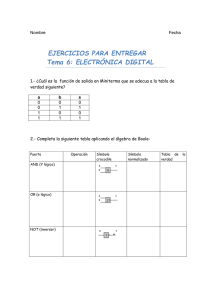

DISEÑO LOGICO I PROGRAMA DE LA MATERIA – Año 2015 Ing. en Computación – Ing. Electrónica – Ing. Biomédica Dpto. de Electricidad, Electrónica y Computación PROGRAMA DE LA MATERIA TEMA 1 (OPCIONAL PARA ING. ELECTRONICA Y BIOMÉDICA) CODIFICACION DE LA INFORMACION: Serie. Paralelo. CODIGOS: BCD. De Gray. ASCII. ALGEBRA DE BOOLE: Operadores de Boole. Propiedades básicas. Teorema de De Morgan. FUNCIONES DE BOOLE: Definición. Propiedades. Funciones especiales: O-exclusivo. Coincidencia. Mayoría. Operadores universales. Bibliografía: Texto: 2, 5, 7 Consulta: 8, 10, 13 TEMA 2 REPRESENTACION DE LAS FUNCIONES DE BOOLE: Tabla de verdad. Forma algebraica. Formas normales. Imagen. Forma R. Mapa de Veitch. Mapa de Karnaugh. Con compuertas lógicas. Con contactos. LENGUAJE DE DESCRIPCION DE HARDWARE: Formato del HDL. VHDL. Señales y tablas. Operadores lógicos, aritméticos y relacionales. Librerías básicas. HERRAMIENTAS DE DISEÑO: Entrada de diseño. Compilador. Verificación del proyecto. Bibliografía: Texto: 8, 9 Consulta: 2, 3, 4, 13 TEMA 3 MINIMIZACION DE FUNCIONES DE BOOLE: Métodos algebraicos. Método Gráfico: Mapas de Karnaugh para funciones de hasta cinco variables. Método Tabular: Algoritmo de Quine y Mc Cluskey. TABLA DE CUBRIMIENTO: Construcción de la tabla. Criterios de elección. CONDICIONES DE INDIFERENCIA: Definición. Su uso en la minimización. Bibliografía: Texto: 9, 13 Consulta: 6, 7, 8, 20 TEMA 4 SISTEMAS COMBINATORIOS: Definición de dipolo. Definición de multipolo. SINTESIS CON CIRCUITOS INTEGRADOS DE PEQUEÑA ESCALA: Formas comerciales. Métodos de síntesis. SINTESIS CON COMPUERTAS NOO, NOY: Formas comerciales. Métodos de síntesis. Diseño modular. SINTESIS CON COMPUERTAS OEXCLUSIVA, MAYORIA: Formas comerciales. Métodos de síntesis. COSTO DE UNA SINTESIS: Fundamentos, criterios. ANALISIS DE SISTEMAS COMBINATORIOS: Necesidad. Métodos. CARRERAS EN SISTEMAS COMBINATORIOS: Planteo del problema (retardos). Solución. Bibliografía: Texto: 4, 8, 9 Consulta: 2, 3, 13 TEMA 5 CIRCUITOS INTEGRADOS DE MEDIANA ESCALA: Definiciones. SUMADORES: Medio sumador. Sumador completo. Diseño de un sumador completo para un bit. Diseño de un sumador para n bits. Sumador serie. Sumador paralelo. Sumador paralelo con anticipo de llevo. MULTIPLEXORES: Descripción. Formas comerciales. Métodos de síntesis de funciones. Diseño modular. DECODIFICADORES: Descripción. Formas comerciales. Método de síntesis de funciones multipolos. CODIFICADORES: Descripción. Formas comerciales. Aplicaciones. DEMULTIPLEXORES: Descripción. Formas comerciales. Aplicaciones. COMPARADORES BINARIOS: Comparadores de un bit. Comparadores de n bits. Comparador con circuito de adelanto de llevo. Formas comerciales. CIRCUITOS DETECTORES DE ERROR: Circuitos de paridad. UNIDAD ARITMETICA LOGICA: Descripción. Formas comerciales. MSI EN VHDL: Mx, DMx, Sumadores, Decodificadores, Codificadores, ALU, Comparadores. Bibliografía: Texto: 3, 8, 9 Consulta: 2, 4, 6, 7, 8 TEMA 6 (OPCIONAL PARA ING. ELECTRONICA Y BIOMÉDICA) CIRCUITOS INTEGRADOS DE GRAN ESCALA. PLD: Definiciones. ROM: Descripción. Distintos tipos. Formas comerciales. Implementación de funciones lógicas. PLA: Descripción. Implementación de funciones lógicas. PAL: Descripción. Implementación de funciones lógicas. Bibliografía: Texto: 8, 9 Consulta: 11, 13 DISEÑO LOGICO I PROGRAMA DE LA MATERIA – Año 2015 Ing. en Computación – Ing. Electrónica – Ing. Biomédica Dpto. de Electricidad, Electrónica y Computación TEMA 7 SISTEMAS SECUENCIALES: Descripción. Tipos. Sistemas Sincrónicos. MAQUINA DE ESTADO FINITO: Definición. Nomenclatura. Características. REPRESENTACION DE LOS SISTEMAS SECUENCIALES SINCRONICOS: Tabla, diagrama y matriz de transición. CLASIFICACION DE ESTADOS Y SUBMAQUINAS: Persistentes. Aislados. Transitorios. Importancia. DISTINTOS MODELOS DE MEF: Mealy, Moore, Grafcet. Bibliografía: Texto: 1 Consulta: 2, 9, 13 TEMA 8 ESTADOS EQUIVALENTES: Definiciones. Estados k-equivalentes. Tablas Pk. Tabla de pares. EQUIVALENCIA DE MAQUINAS: Definiciones. Forma mínima de una máquina. Clasificación. Bibliografía: Texto: 1 Consulta: 2, 9, 13 TEMA 9 SISTEMAS SECUENCIALES SINCRONICOS: Diagrama en bloques. ELEMENTOS DE MEMORIA BINARIOS: Flipflops tipo T, D, RS, JK. SINTESIS DE SISTEMAS SECUENCIALES SINCRONICOS USANDO FLIP FLOPS: Método de trabajo. Asignación de estados. Reglas. Funciones de excitación. ELEMENTOS DE MEMORIA N-ARIOS: Contadores y Registros de Desplazamiento. Distintos tipos comerciales. SINTESIS USANDO CONTADORES: Asignación de estados. Reglas. SINTESIS USANDO REGISTROS DE DESPLAZAMIENTO: Asignación de estados. Reglas. ANALISIS DE SISTEMAS SECUENCIALES SINCRONICOS: Razones. Método. Solución para los estados sobrantes. ELEMENTOS DE MEMORIA SINCRÓNICOS y MEF EN VHDL: Flip Flops T, D, RS, JK, Contadores, Registro de desplazamientos. Bibliografía: Texto: 8, 9 Consulta: 3, 6, 7, 13 TEMA 10 INTRODUCCIÓN A LAS FPGAS: Evolución de los Dispositivos Programables. Definición de un FPGA. Bloque Lógicos. Recursos de Interconexión. Aspectos Económicos. Aplicaciones de las FPGAs. Implementación de Procesos. FPGAS DISPONIBLES COMERCIALMENTE: Tecnologías de Programación. SRAM. Antifusible. EPROM y EEPROM. FPGAs comerciales. FLUJO DE DISEÑO DE UN FPGA: Entrada de diseño. Traducción. Partición. Ubicación. Verificación. Bibliografía: Texto: 14, 15, 16 Consulta: 17 TEMA 11 SISTEMAS DE DESARROLLO EXPERIMENTALES: Descripción. Características. Alimentación. Oscilador. Puentes de configuración. DISPOSITIVOS CycloneII: Terminales de acceso a señales del dispositivo. Visualización. Puertos de Expansión. Verificación. Implementación. Puerto VGA. Puerto Mouse. Bibliografía: Texto: 18, 19 Consulta: 20 TEMA 12 MICROPROCESADORES: Definición. Esquema Básico. Aplicaciones. CONTROLADORES LOGICOS PROGRAMABLES (PLC): Esquema interno. Características principales. Lenguajes de programación. Aplicaciones. Bibliografía: Texto: 5, 6, 7, 9, 12 Consulta: 10 TEMA 13 IMPLEMENTACION DE SISTEMAS DIGITALES EN AUTOMATAS: Programación con lenguaje de lista de instrucciones, con diagramas: ladder y bloques funcionales. BLOQUES DE PROGRAMACIÓN: Temporizadores, contadores. Programación con Grafcet: Aplicaciones. Bibliografía: Texto: 12 Consulta: 9, 21 DISEÑO LOGICO I PROGRAMA DE LA MATERIA – Año 2015 Ing. en Computación – Ing. Electrónica – Ing. Biomédica Dpto. de Electricidad, Electrónica y Computación TEMA 14 (OPCIONAL PARA ING. ELECTRONICA Y BIOMÉDICA) COMPUERTAS DE TRES ESTADOS: Definición. Concepto de bus. Utilidad. CONVERSION A/D: Métodos y parámetros. CONVERSIÓN D/A: Métodos y parámetros. MEMORIAS: Definición. Clasificación. Modo de almacenamiento. Memorias no volátiles ROM. Memorias volátiles RAM. Bibliografía: Texto: 2 - Consulta: 8. PROGRAMA DE EXAMEN ING. en COMPUTACION TEMA 1: LENGUAJE DE DESCRIPCION DE HARDWARE. (2). SUMADORES. (5). ELEMENTOS DE MEMORIA BINARIOS. (9). TEMA 2: HERRAMIENTAS DE DISEÑO. (2). MULTIPLEXORES. (5). SINTESIS DE SISTEMAS SECUENCIALES SINCRONICOS USANDO FLIP FLOPS. (9). TEMA 3: CODIFICACION DE LA INFORMACION. (1). DECODIFICADORES. (5). ELEMENTOS DE MEMORIA N-ARIOS. Registros de Desplazamiento. (9). TEMA 4: CODIGOS. (1). MINIMIZACIÓN DE FUNCIONES DE BOOLE. Algoritmo de Quine Y Mc Cluskey. (3). SINTESIS USANDO CONTADORES. (9). TEMA 5: FUNCIONES DE BOOLE. (1). SINTESIS USANDO REGISTROS DE DESPLAZAMIENTO. (9). FPGAS DISPONIBLES COMERCIALMENTE (10). TEMA 6: REPRESENTACION DE LAS FUNCIONES DE BOOLE. (2). ANALISIS DE SISTEMAS SECUENCIALES SINCRONICOS. (9). FLUJO DE DISEÑO DE UN FPGA (10). TEMA 7: MINIMIZACION DE FUNCIONES DE BOOLE. (3). ELEMENTOS DE MEMORIA N-ARIOS. Contadores. (9). INTRODUCCION A LAS FPGAS. (10). TEMA 8: TABLA DE CUBRIMIENTO. (3). ESTADOS EQUIVALENTES. Tabla de pares. (8). MEMORIAS. (14). TEMA 9: CIRCUITOS INTEGRADOS DE GRAN ESCALA. ROM. (6). DISTINTOS MODELOS DE MEF. (7). CONVERSION A/D. (14). DISEÑO LOGICO I PROGRAMA DE LA MATERIA – Año 2015 Ing. en Computación – Ing. Electrónica – Ing. Biomédica Dpto. de Electricidad, Electrónica y Computación TEMA 10: CIRCUITOS INTEGRADOS DE GRAN ESCALA. PLA. (6). BLOQUES DE PROGRAMACION. Temporizadores, Contadores. (13). CONVERSION D/A. (14). TEMA 11: SINTESIS CON COMPUERTAS NOO, NOY. (4). CIRCUITOS INTEGRADOS DE GRAN ESCALA. PAL. (6). MSI EN VHDL (5). TEMA 12: ELEMENTOS DE MEMORIA SINCRONICOS EN VHDL. (9). SISTEMAS SECUENCIALES. (7). COMPUERTAS DE TRES ESTADOS. (14). TEMA 13: COSTO DE UNA SINTESIS. (4). MAQUINA DE ESTADO FINITO. (7). IMPLEMENTACION DE SISTEMAS DIGITALES EN AUTOMATAS. (13). TEMA 14: ANALISIS DE SISTEMAS COMBINATORIOS. (4). REPRESENTACION DE LOS SISTEMAS SECUENCIALES SINCRONICOS. (7). MICROPROCESADORES. (12). TEMA 15: CARRERAS EN SISTEMAS COMBINATORIOS. (4). MAQUINA DE ESTADO FINITO. (7). CONTROLADORES LOGICOS PROGRAMABLES (PLC). (12). TEMA 16: CIRCUITOS INTEGRADOS DE MEDIANA ESCALA. (5). CIRCUITOS INTEGRADOS DE GRAN ESCALA. PLD. (6). ESTADOS EQUIVALENTES. Tablas Pk. (8). PROGRAMA DE EXAMEN ING. ELECTRONICA Y BIOMÉDICA TEMA 1: LENGUAJE DE DESCRIPCION DE HARDWARE. (2). SUMADORES. (5). ELEMENTOS DE MEMORIA BINARIOS. (9). TEMA 2: HERRAMIENTAS DE DISEÑO (2). MULTIPLEXORES. (5). SINTESIS DE SISTEMAS SECUENCIALES SINCRONICOS USANDO FLIP FLOPS. (9). TEMA 3: DECODIFICADORES. (5). DISTINTOS MODELOS DE MEF. (7). ELEMENTOS DE MEMORIA SINCRÓNICOS EN VHDL (9). DISEÑO LOGICO I PROGRAMA DE LA MATERIA – Año 2015 Ing. en Computación – Ing. Electrónica – Ing. Biomédica Dpto. de Electricidad, Electrónica y Computación TEMA 4: MINIMIZACIÓN DE FUNCIONES DE BOOLE. Algoritmo de Quine Y Mc Cluskey. (3). MSI EN VHDL. (5). SINTESIS USANDO CONTADORES. (9). TEMA 5: FUNCIONES DE BOOLE. (1). SINTESIS USANDO REGISTROS DE DESPLAZAMIENTO. (9). FPGAS DISPONIBLES COMERCIALMENTE (10). TEMA 6: REPRESENTACION DE LAS FUNCIONES DE BOOLE. (2). ANALISIS DE SISTEMAS SECUENCIALES SINCRONICOS. (9). FLUJO DE DISEÑO DE UN FPGA (10). TEMA 7: MINIMIZACION DE FUNCIONES DE BOOLE. (3). ELEMENTOS DE MEMORIA N-ARIOS. Contadores. (9). INTRODUCCION A LAS FPGAS. (10). TEMA 8: TABLA DE CUBRIMIENTO. (3). ESTADOS EQUIVALENTES. Tabla de pares. (8). IMPLEMENTACION DE SISTEMAS DIGITALES EN AUTOMATAS (13). TEMA 9: DISTINTOS MODELOS DE MEF. (7). EQUIVALENCIA DE MAQUINAS. (9). SISTEMAS DE DESARRLLO EXPERIMENTALES. (11). TEMA 10: CLASIFICACION DE ESTADOS Y SUBMAQUINAS. (7). ESTADOS EQUIVALENTES (8). BLOQUES DE PROGRAMACION. Temporizadores. Contadores. (13). TEMA 11: LENGUAJE DE DESCRIPCION DE HARDWARE. (2). SINTESIS CON COMPUERTAS NOO, NOY. (4). CIRCUITOS INTEGRADOS DE MEDIANA ESCALA. (5). TEMA 12: SINTESIS CON COMPUERTAS O-EXCLUSIVA, MAYORIA. (4). SISTEMAS SECUENCIALES. (7). BLOQUES DE PROGRAMACIÓN: Programación con Grafcet. (13). TEMA 13: COSTO DE UNA SINTESIS. (4). MAQUINA DE ESTADO FINITO. (7). SINTESIS USANDO REGISTROS DE DESPLAZAMIENTO. (9). DISEÑO LOGICO I PROGRAMA DE LA MATERIA – Año 2015 Ing. en Computación – Ing. Electrónica – Ing. Biomédica Dpto. de Electricidad, Electrónica y Computación TEMA 14: ANALISIS DE SISTEMAS COMBINATORIOS. (4). REPRESENTACION DE LOS SISTEMAS SECUENCIALES SINCRONICOS. (7). MICROPROCESADORES. (12). TEMA 15: CARRERAS EN SISTEMAS COMBINATORIOS. (4). MAQUINA DE ESTADO FINITO. (7). CONTROLADORES LOGICOS PROGRAMABLES (PLC). (12). TEMA 16: CONDICIONES DE INDIFERENCIA. (3). CIRCUITOS DETECTORES DE ERROR. (5). ESTADOS EQUIVALENTES. TABLAS Pk. (8). BIBLIOGRAFIA - Gill, A. “Introduction to the theory of finite state machines”. Mc Graw Hill. New York. 1962. (1) - R. J. Tocci, N. S. Widmer, G. L. Moss, “Sistemas Digitales. Principios y aplicaciones”, 10th ed. Ed. México: Pearson Educación, 2007. (2) - Floyd, Thomas L. “Fundamentos de Sistemas Digitales”, 6ª ed. Prentice Hall. Madrid 1997. (3) - Peatman. J.B. “The design of digital systems”. Mc Graw Hill. Tokyo. 1972. (4) - Wakerly, John F. “Diseño Digital Principios y Aplicaciones”, Prentice Hall. México (5) - Cuesta, L.; Gil Padilla, A.; Remiro, F. “Electrónica digital”. Mc Graw Hill. Madrid. 1992. (6) - Tokheim, R. “Principios digitales”. Mc Graw Hill. Madrid 1990. (7) - Morris Mano, M. “Diseño Digital”, 3ª ed. Pearson Educación, México, 2003. (8) - Parras Criado; Montanero Molina. “Autómatas programables. Fundamentos”. Mc Graw Hill. 1990. (9) - Cassell, D. “Microcomputers and modern control engineering”. Reston Publishing Company. Prentice Hall. Virginia. USA. 1983. (10) - Manuales de circuitos integrados digitales comerciales. (11) - Manuales de controladores lógicos programables comerciales. (12) - Ginzburg, M. “Introducción a las técnicas digitales con circuitos integrados”. Editorial Mitre. B.A. 1992. (13) - E. Mandado, L. J. Álvarez, M. D. Valdés, “Dispositivos Lógicos Programables y sus aplicaciones”. Ed. España: Thomson, 2002. (14) - E. Mandado Pérez, Y. Mandado Rodriguez, “Sistemas Electrónicos Digitales”, 9th ed. Ed. Alfaomega-Marcombo. 2008. (15) - Brown Stephen D., Francis Robert J., Rose Jonathan, Vranesic Zvonko G. Field-Programmable Gate Arrays. Editorial Kluer Academic Publisher. 1993. (16) - Salcic Zoran, Smailagic Asim. Digital Systems Design and Prototyping Using Field Programmable Logic. Editorial Kluer Academic Publisher. 1997. (17) - Z. Navabi, “Digital design and implementation with field programmable devices”, .Kluer Academic Publishers. 2005 (18) - Altera Corp. Quartus II Web Edition Software. Disponible en: https://www.altera.com/download/software/quartus-ii-we (19) - Sitio web www.Altera.com. (20) - http://www.schneider-electric.com/download/hk/en/results/0/0/1556971-Zelio-Soft/ (21)