Enunciado TPN0

Anuncio

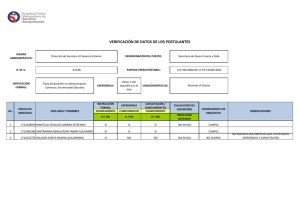

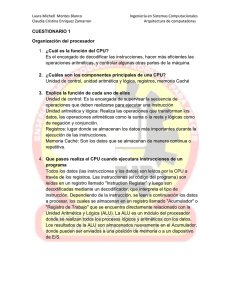

Página 1 de 4 Problemas de Ejercitación de Prerrequisitos Arquitectura de Computadoras 11/03/2014 Instrucciones Los problemas de ejercitación propuestos en el presente trabajo práctico pueden ser resueltos en forma individual o grupal. El planteo de la solución debe realizarse basándose en lo aprendido en las asignaturas correlativas. Puede utilizar las clases de consulta para consultar problemas de enunciado y verificar la validez de la solución obtenida. Posteriormente, se tomará una evaluación con problemas similares a los de este práctico, la cual deberá ser resuelta en forma individual. La fecha de evaluación se encuentra en el sitio web de la materia. Conceptos involucrados Cálculos estadísticos de porcentajes y promedios ponderados. Sistema de numeración binario y hexadecimal. Aritmética binaria. Síntesis. Compuertas y circuitos MSI. Programación en Lenguaje Ensamblador. Componentes internos de la trayectoria de datos de un microprocesador. Transferencias de registros. Ciclo de la Instrucción. Ejercicios Propuestos 1) Se tiene una bolsa con 10 monedas, de las cuales 9 son monedas normales y una es una moneda especial que tiene dos caras. a) Si se saca una sola moneda de la bolsa, y se la tira cinco veces seguidas, ¿cuál es la posibilidad de obtener cinco caras? b) Si se saca una sola moneda de la bolsa, se la tira cinco veces seguidas y se obtienen cinco caras, ¿cuál es la posibilidad de que la moneda que se sacó sea la que tiene dos caras? 2) [Recomendado] Realice las siguientes operaciones en la misma base en que se hayan indicados los números. Para cada apartado, considere primero que son números sin signo, y luego hágalo con números con signo. En caso que alguna operación no sea posible, indíquelo. a) b) c) d) $C3 + $2A $2B – $C3 $FF + $01 $351B + $D2A5 e) f) g) h) $C1A9 + $BC23 $0001 - $FFFE %1010 - %0011 %1010 - %1110 3) Utilizando multiplexores únicamente diseñe un circuito capaz de multiplicar un número binario de cuatro bits por 1, 2, 4 u 8. 4) [Recomendado] Escriba un programa en lenguaje ensamblador del CPU08 para inicializar en cero un arreglo ubicado a partir de la dirección $0090. El tamaño del arreglo se encuentra en la dirección $0080. 5) [Recomendado] Escriba una función en lenguaje ensamblador del CPU08 que multiplique un vector por un escalar. El vector está ubicado a partir de la dirección BASE, su tamaño en la dirección TAM y el número en el acumulador A. Todos los números son de 8 bits. El resultado deberá ser almacenado a partir de la dirección RESULTADO. 6) [Profundización] Escriba una función en lenguaje ensamblador del CPU08 que sume dos vectores A y B. Los mismos están ubicados a partir de la dirección BASE_A y BASE_B respectivamente, el tamaño de ambos está en la dirección TAM y el resultado debe almacenarse a partir de la dirección RESULTADO. Todos los números son de 8 bits. Problemas de Ejercitación de Prerrequisitos Página 2 de 4 7) [Recomendado] Dada la siguiente trayectoria de datos, cuyo esquema simplificado se muestra en la figura, y teniendo en cuenta que en la misma la ALU, todos los registros, rutas de datos y de direcciones son de 32 bits, que cada transferencia entre registros toma 2 ciclos de reloj y que el tiempo de acceso a memoria mínimo es 3 ciclos. AC AR SP DR PC IR SR Y Unidad de Control Z ALU ADDRES BUS DATA BUS Donde los registros son: PC: Registro Contador de Programa AR: Registro de Direcciones IR: Registro de Instrucciones AC: Registro Acumulador, único de propósito general Y, Z: Registros Temporales, utilizados para operar en la ALU SP: Registro Puntero de Stack DR: Registro de Datos SR: Registro de Estado Se le pide que: a) Detalle la implementación de la instrucción PUSH AC, la cual ocupa una palabra de memoria. Considere que la pila del sistema está implementada de la forma más frecuente (el registro SP apunta al último lugar ocupado). b) Calcule el tiempo que se tarda en ejecutar dicha instrucción suponiendo que el control de procesador no presenta retardo alguno. 8) Utilizando el camino de datos del ejercicio anterior, se pide que: a) Detalle la implementación de la instrucción ADD ($1000), la cual realiza la suma del acumulador con el valor contenido en la dirección que viene dada en una palabra a continuación de la instrucción, y almacena el resultado en el acumulador. b) Calcule el tiempo que se tarda en ejecutar dicha instrucción, suponiendo que el control del procesador no presenta retardo alguno. 9) [Recomendado] Sobre la arquitectura del SRC-1 vista en Sistemas con Microprocesadores y Microcomputadoras y la cual se adjunta a continuación, se desea agregar una instrucción JR disp, la cual tiene el siguiente RTN Abstracto: PC PC + disp. Banco de Registros PC MAR MDR IR A C ALU ADDRES BUS DATA BUS a) Indique qué operación conceptual realiza la instrucción JR. b) Indique el formato de la instrucción JR. c) Detalle el RTN concreto de la instrucción JR. Problemas de Ejercitación de Prerrequisitos Página 3 de 4 10) [Profundización] Dada la trayectoria de datos del ejercicio anterior, cuyo esquema simplificado se muestra en la figura, y teniendo en cuenta que en la misma la ALU, todos los registros, rutas de datos y de direcciones son de 32 bits, que cada transferencia entre registros toma 1 ciclo de reloj y que el tiempo de acceso a memoria mínimo es de 4 ciclos, se pide que: a) Detalle el RTN concreto de la instrucción DLD r1, r2, dir, cuyo RTN abstracto es R[r1] M[dir]; R[r2] M[dir+4]. Tener en cuenta que la dirección dir está ubicada en la siguiente palabra después de la instrucción. b) Indique cuántos ciclos de reloj demora en ejecutarse dicha instrucción. 11) Se desea manejar con un procesador HC908QY4 cuatro displays de siete segmentos en forma multiplexada, utilizando solamente el puerto B. Para ello se propone utilizar cuatro displays TLS336T (de cátodo común), un decodificador SN74LS48 y cuatro transistores NPN. El software debe mostrar en los cuatro displays el número BCD compactado almacenado en las direcciones $0080 y $0081. Para ello debe escribir una subrutina transparente Display, que realice un solo barrido actualizando los cuatro dígitos y retornando. Para lograr el efecto de persistencia, el dígito debe permanecer encendido un determinado tiempo, para ello utilice una subrutina Delay ya existente que no requiere parámetros y genera una demora adecuada. Se pide: a) Diagrama del hardware. b) Diagrama de flujo del software de la subrutina Display. c) Código ensamblador de la subrutina Display. 12) Considere un procesador con tres niveles de pedido de interrupciones: 1, 2 y 3, siendo el nivel 1 el de máxima prioridad. En cada nivel, los dispositivos están conectados en Daisy-Chain. A fin de manejar adecuadamente las prioridades, el registro de estado (PSW) contiene una máscara que indica el nivel de prioridad del programa en ejecución, y si el nivel del pedido es superior se procede a atender la interrupción. Las rutinas de servicio de los dispositivos A duran 200 M y las de los B y C duran 50. En el mismo se está ejecutando un programa principal, y en el instante M0 los dispositivos B2, C2 y A2 piden interrupción simultáneamente, en M40 pide A3, en M73 pide B1 y en M120 pide C1. Nivel 1 CPU Nivel 2 Nivel 3 A1 B1 C2 A3 A2 B2 C1 a) Indique qué dispositivo está siendo atendido en M100. b) Indique cuál es el último dispositivo en ser atendido y cuántos ciclos M pasan desde el primer pedido hasta que se completa la atención del mismo. c) Indique cuál es el dispositivo que más tiempo espera en ser atendido y cuánto es este tiempo. d) Si en M121 interrumpe A1, indique cuánto tiempo debe esperar hasta ser atendido. e) Indique cuánto demoran en atenderse todos los pedidos si ahora A1 repite su interrupción cada 300M a partir de M121. 13) [Profundización] Un sistema externo envía paquetes de 1 Byte a través de una interrupción hacia un microcontrolador QY4. El mismo debe esperar a que se cargue un bloque de 10 Bytes antes de procesarlo. Se necesita implementar el código para controlar el procesamiento de los bloques de datos utilizando la técnica de Swinging Buffers. Para ello, se deben utilizar dos tablas en memoria, las cuales serán cargadas en una rutina de interrupción y procesadas en el programa principal. Se utilizará PUNT0, PUNT1 como punteros a cada bloque y COND0, COND1 contadores de buffers. Se pide: a) Escribir la rutina de inicialización del programa. b) Escribir la rutina de interrupción, donde se escribirá en el buffer disponible, el dato recibido utilizando la subrutina recibirDato(CONT, HX), que recibe el contador del dato esperado y un puntero al lugar donde debe escribirlo. c) Escribir la rutina principal del programa, donde se debe esperar a que se cargue cualquiera de las dos tablas completa, y luego se ejecute a la subrutina procesarDatos1() o procesarDatos2() respectivamente. Problemas de Ejercitación de Prerrequisitos Soluciones Propuestas 1) 2) 7) a) 12.81% b) 78% a) b) c) d) e) f) g) h) $ED en ambos casos. $68 con signo, overflow sin signo. $00 con signo, overflow sin signo. $07C0 con signo, overflow sin signo. Overflow en ambos casos. $0003 con signo, overflow sin signo. Overflow con signo, %0111 sin signo %1100 con signo, overflow sin signo. a) La solución se puede realizar en 7 pasos. b) 16T 8) a) La solución se puede realizar en 9 pasos. b) 21T 9) a) Salto relativo b) Cinco bits de Op-Code, el resto desplazamiento c) La solución se puede realizar en 7 pasos. 10) a) La solución se puede realizar en 11 pasos. b) 23 T Página 4 de 4